在16通道演示器中验证的经验型多通道相位噪声模型

本文详细介绍一种在大型多通道系统中预测相位噪声的系统方法,并将预测到的值与在16通道S频段演示器上测量到的值进行比较。这种分析方法基于一小组测量值,可用于估算相关和不相关的噪声贡献。仅依靠少数几个测量值,就可以预测大范围条件下的相位噪声。其观点是:任何特定设计都需建立自己的系统噪声分析,而16通道演示器则提供一个特定设计示例作为基础。本文讨论基于16通道演示器的假设和相关限制,包含该假设何时适用,以及何时因为系统复杂性增加需要增加额外的噪声项。本文主要描述如何在RF系统中实施相位噪声优化。在适当情况下,提供描述本分析中使用的基本原理的参考资料 。

相位噪声是衡量所有RF系统设计的一个重要的性能指标。在相控阵这类大型多通道RF系统中,通道之间彼此关联,其目标之一就是利用分布式接收器和发射器的关联组合,从阵列层级改善动态范围。要达成此目标,面临着一项系统工程挑战:分解出系统中相关和不相关的噪声项。本文展示一种能估算16通道RF演示器的相位噪声的系统方法,以帮助系统工程师开发出一种能评估大型系统的噪声性能的分析方法。

相控阵内的信号都包含在通道上不相关的噪声项和在通道上相关的噪声项。分布式组件的附加噪声就是不相关的。但是,分布式组件共用的信号会产生相关的噪声成分。挑战在于:如何快速识别架构中的相关噪声项。共通或共享的内容都会在通道中引发相关噪声。示例包括共用LO、时钟或电源。随着系统复杂性增加,解决这些噪声项会变得很困难。所以,如果能使用直观方法从噪声角度重新绘制架构,并且快速识别相关噪声贡献项,将对构建下一代系统的系统设计人员大有助益。

在本文中,我们通过16通道S频段系统来演示方法,证明仅使用几个经验测量值,就可以较为准确地预测其他多种通道组合下的相位噪声。对于这种经验模型,关键的一点是需要一些实际测量值。要从组件仿真直接进入大型多通道相位噪声估算(且具有不错的精度)并不容易。但是,仅使用几个测量值,就能提取出相关和不相关的噪声项,使得多通道估算值较为准确。我们的测量将预估值(1 dB以内)和16通道S频段演示器的测量值进行匹配。

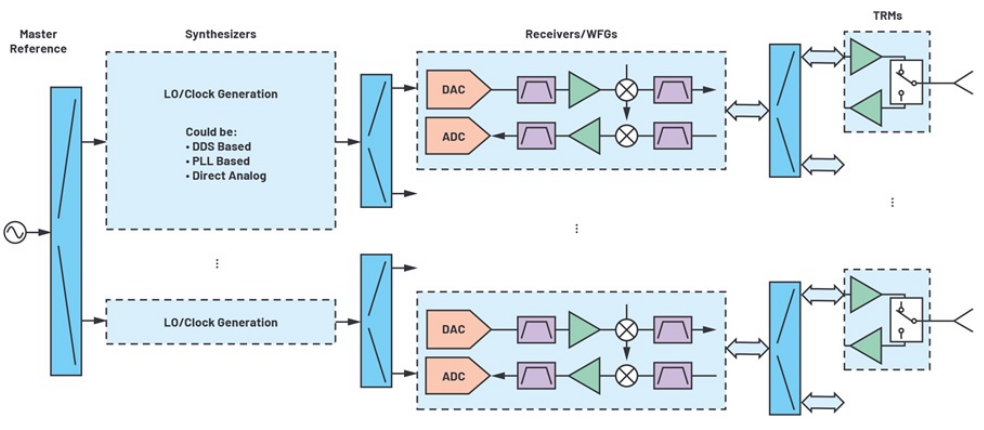

图1. 16通道演示器:该平台包含4个AD9081 芯片。每个AD9081 芯片包含4路射频 DAC和4路射频 ADC,提供总共16路发射和16路接收通道。

在自由空间或RF信号处理组合信号时,每个信号增加的噪声为

其中c表示相关系数,范围为–1至+1。如果c = –1,噪声被消除;如果c = 0,噪声不相关;如果c = 1,噪声完全相关。

假设校准用于一致合并主信号,主信号将以20logN水平增加,其中N是通道数。

-

如果噪声项不相关(c = 0),噪声会以10logN增加。信号电平以20logN速率增加(比噪声速率大10logN),SNR会随之改善10logN。

-

如果噪声项相关(c = 1),噪声和信号一样,也以20logN的速率增加,所以SNR不会改善。对于分布式系统来说,这并不是理想的结果。

-

在噪声抵消电路中,会产生负相关系数。记下此案例,是为了补证公式1,但不加以详述。

事实上,大型分布式系统包含在通道中部分相关的噪声成分。所以,需要开发一种实用且直观的系统级噪声模型的方法。

为了在多通道环境中评估最新的高速数据转换器,16通道直接S频段射频采样平台被开发出来。该平台包含4个AD9081 MxFE ® (混合信号前端)芯片。每个 AD9081 芯片包含4个RF DAC和4个RF ADC,提供总共16个发射和16个接收通道。

16通道评估平台 因为具有4个MxFE 芯片,所以命名为Quad-MxFE。总体框图和板图片分别如图1和图2所示。

图2. Quad-MxFE是一个16通道演示器。

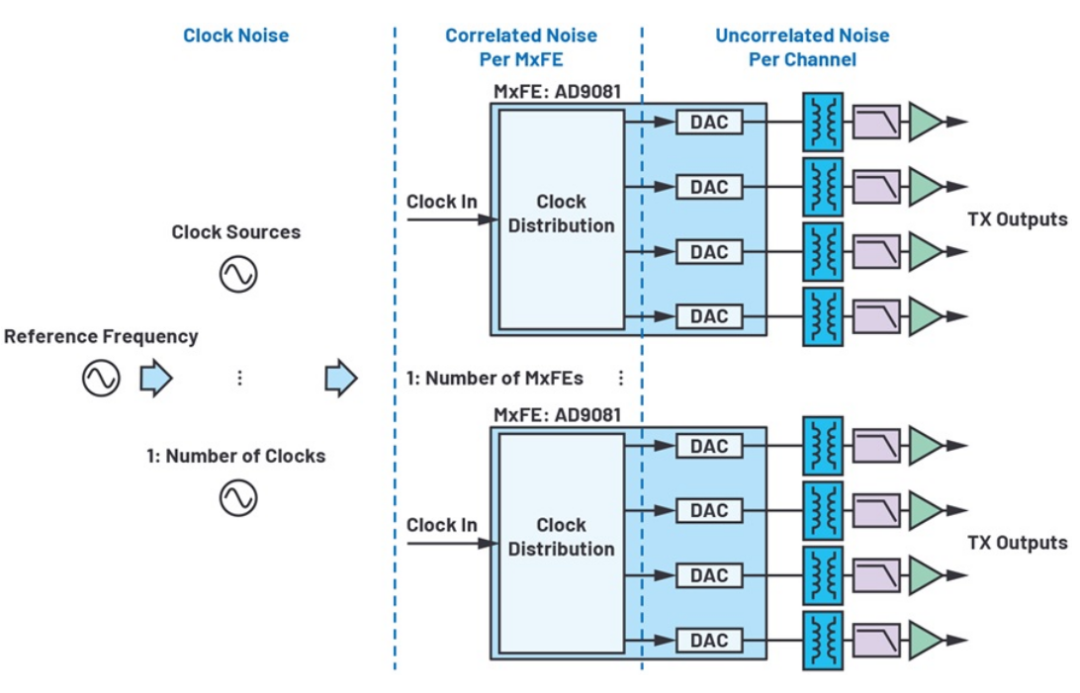

图1所示的16通道开发平台框图显示了其功能范围。从图中可以看出,开始时并不清楚如何查看相关和不相关噪声组件导致的噪声部分。需要提供一种方法,从噪声的角度考虑系统架构。可以通过一份草图,指出所有通道都存在的噪声项、至于某些通道组相关的噪声项,以及与通道完全无关的噪声项。图3是对16通道开发平台的图解,将噪声项分为三类。

图3. 从时钟相位噪声角度重新绘制的图1。

-

时钟噪声:Quad-MxFE提供适用于多种时钟配置的选项。关于使用的特定配置,需要在相位噪声模型中进行说明。我们的测试跨所有通道使用1个通用低相位噪声时钟,或者使用4个独立的分布式 ADF4371 锁相环(PLL)频率合成器来作为4个MxFE各自的时钟输入。对于单个通用时钟,此噪声与所有16个组合通道相关。对于使用4个ADF4371 PLL(1个MxFE 1个)的情况,PLL噪声与每个MxFE相关,但跨MxFE无关,而基准电压源噪声则跨所有通道相关。

-

Peter Delos名为 "带有分布式锁相环的相控阵的系统级LO相位噪声模型"的文章总结了处理分布式锁相环的分析方法。这份参考资料所用的分析方法说明了基准频率、分布式系统和PLL电路的噪声分量,并说明了PLL环路带宽造成的影响。

-

每个MxFE导致的相关噪声:这是来自MxFE,与MxFE中的每个通道相关的噪声。在此分析中,每个MxFE的相关噪声包括每个芯片中常见的附加噪声,以及芯片内部各通道中常见的电源效应。

-

每个通道的不相关噪声:这是来自不同通道的噪声差异。包括DAC内核和所有放大器附加相位噪声。在公式2中,此项被标注为TXNoise。

根据所述的相位噪声的贡献分量,可以如下所示计算相位噪声总和。

接下来,会提供一些额外的细节,介绍如何简化此模型,以适用于此测试台。

-

电源效应:在低相位噪声设计中,电源相位噪声是一个需要重点考虑的因素。有关可用于解决电源噪声问题的方法,请参阅文章 "电源调制比揭秘:PSMR和PSRR有何区别" 和 "改进的DAC相位噪声测量支持超低相位噪声DDS应用。" 在本文的分析中,电源效应被视为公式2中捕捉的噪声项的子项。如果电源噪声是IC中的相位噪声的主要来源,且遍布在所有通道中,则需要像本文之前使用的每个MxFE导致的相关噪声一样,将此效应当做相关项进行说明。

-

基准振荡器噪声:在大型系统中,基准振荡器噪声贡献分量需要按文章"带有分布式锁相环的相控阵的系统级LO相位噪声模型"中所述的一样进行分配。这个测试台使用极低的相位噪声基准电压源,产生的噪声分量比其他分量低得多,所以未在噪声总和公式中特别指出。

在公式2介绍了组合相位噪声模型之后,下一个问题是"如何得到公式中使用的噪声贡献分量值?"在使用Quad-MxFE测试台时,可使用测量值来提取所需的信息:

-

时钟源的绝对相位噪声

-

不同MxFE的通道的附加相位噪声

-

同一个MxFE的通道的附加相位噪声

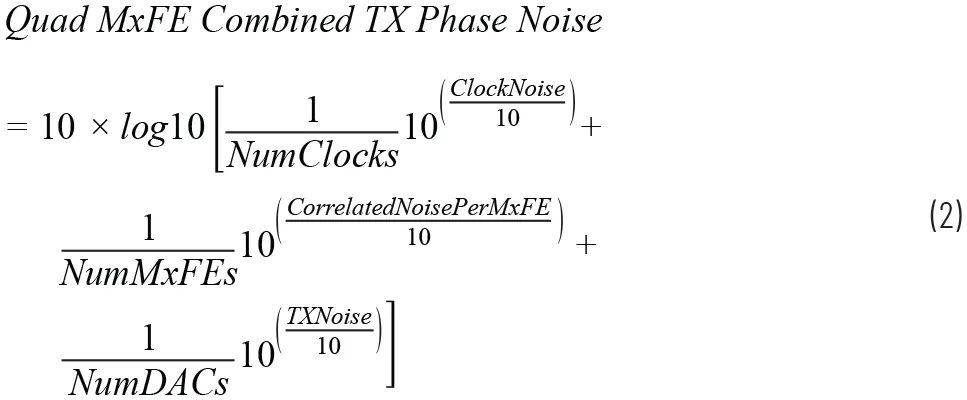

测试设置和测量值如图4所示。图4(b)和图4(c)提供去除了共用时钟源的附加噪声测量。测量单个MxFE中的附加相位噪声时,也会去除MxFE中跨通道的相关噪声。但是,在测量跨MxFE的附加相位噪声时,测量值中会包含MxFE中的相关噪声。

图4. 使用三项测量来验证相位噪声模型。

最后一步是将测量数据更改为公式2中使用的三个项,如下所示:

-

时钟噪声 = 时钟相位噪声测量值(图4(a))+ 20log (F OUT /FCLOCK)

-

每个MxFE导致的相关噪声 = 跨MxFE的附加相位噪声(图4(b))– 通用MxFE的附加相位噪声(图4(c))。注意,进行此计算时,需要先转化为线性功率,然后减去,然后重新转化为dB,得出10log(10^(跨MxFE的附加相位噪声/10)– 10^(通用MxFE的附加相位噪声/10))

-

TxNoise = 通用MxFE的附加相位噪声(图4(c))。

关于附加相位噪声测量的附加备注:我们发现,使用此硬件时,上述项2和3的噪声项也随频率扩展。转化为其他频率时,还额外需要20log(F OUT /F MEAS )。并非所有硬件都是如此,每项设计需要单独评估此项。

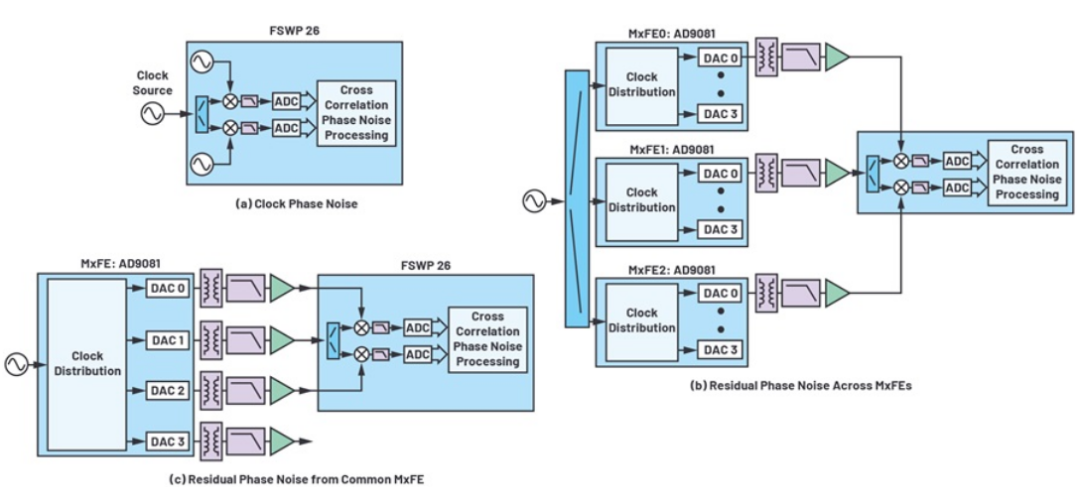

执行此测量时,在整个16通道演示器中使用一个低噪声12 GHz时钟。时钟源为SMA100B,如图1所示被注入到外部时钟注入节点中。所示的条件适用于3.2 GHz发射输出频率。

从图5(b)可以看出,跨MxFE的相关噪声是最主要的贡献分量。在系统中增加MxFE后,这种噪声贡献分量会增大,之后受通用时钟源限制。根据每种贡献分量的曲线形状,仅在曲线上增加几个点不足以得出准确的预测,所以我们发现最好是直接在公式2中使用图5(b)中的数据。然后,进行一系列计算来验证该模型。从图6至图8可以看出,该模型提供的预测值准确度非常高。

图5. a) 用于验证相位噪声模型的测量值,b) 计算得出的在模型中使用的相位噪声贡献分量。这是针对所有MxFE共用一个时钟的情况。

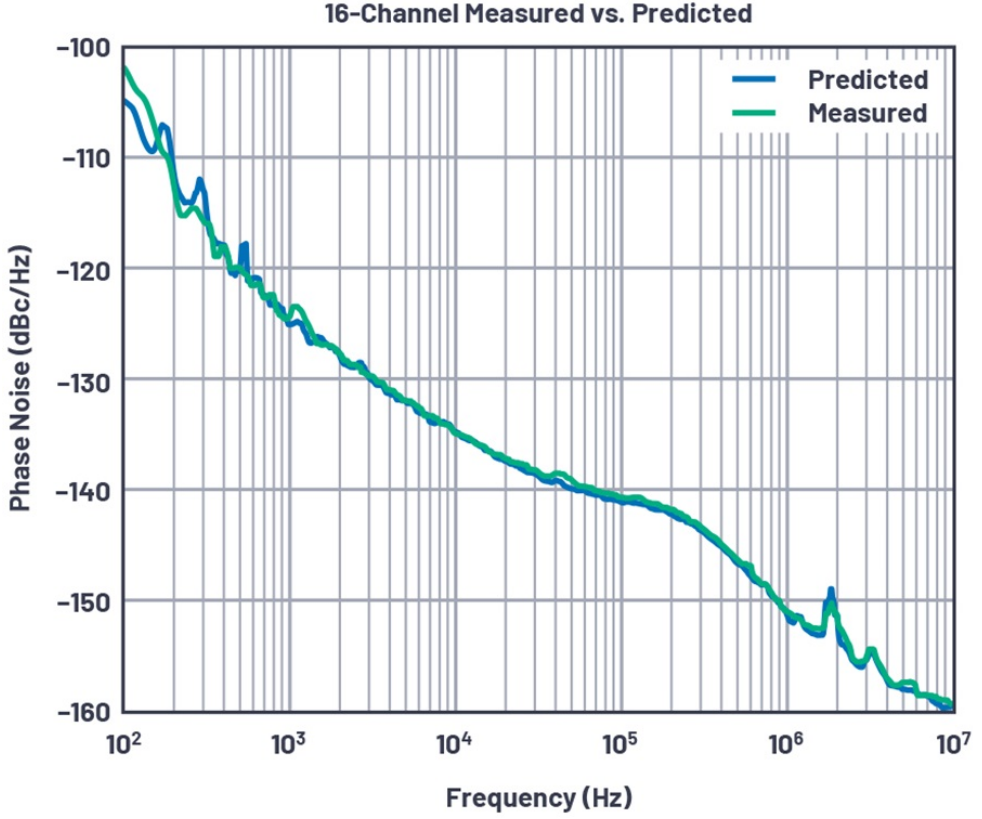

图6. 3.2 GHz时16通道的测量值和模型预测值。

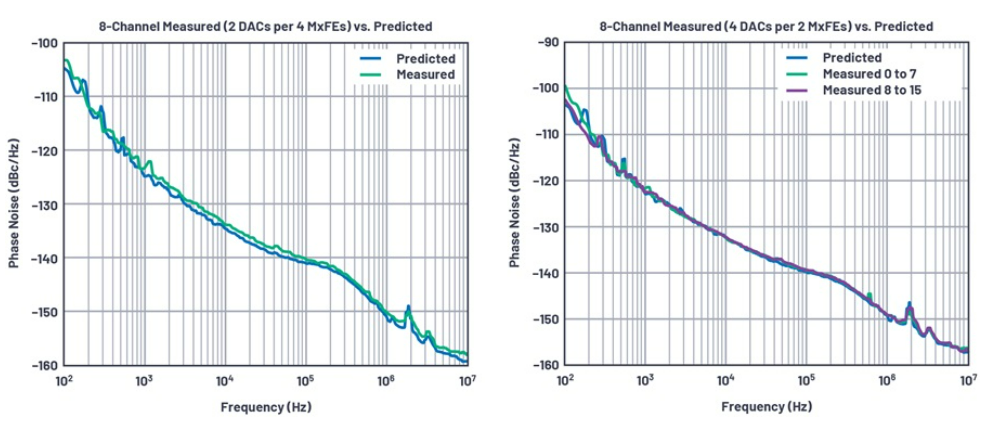

图7. 3.2 GHz时8通道的测量值和模型预测值。两图之间的差异在于:MxFE如何共用发射通道。

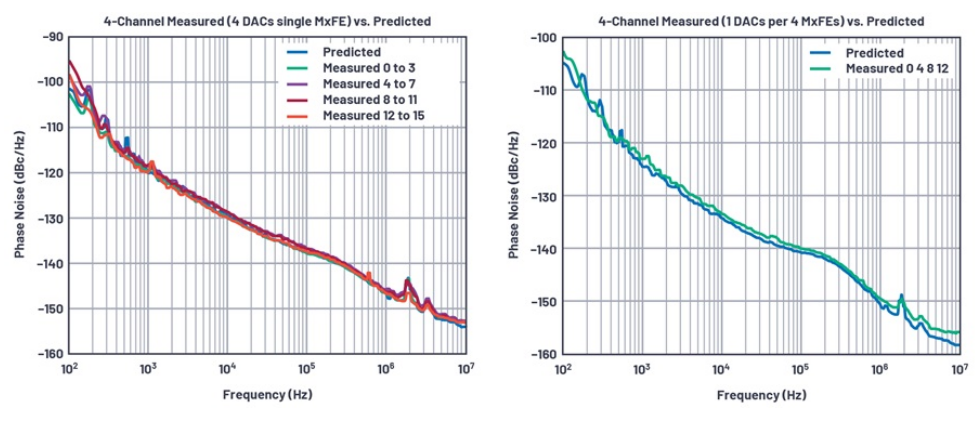

图8. 3.2 GHz时4通道的测量值和模型预测值。两图之间的差异在于:MxFE如何共用发射通道。

一些关于测量值和预测值的观察值得注意。在许多情况下,预测值几乎与测量值完全一样。在某些情况下,测量值略低于预测值。我们承认这一点,但无法给出准确描述。图8左侧的图提供了一个潜在的指示器。当放大这些图时,我们发现预测值与两个测量示例匹配,但测量案例的值稍高一点。可能是因为在AD9081 芯片中,每个MxFE导致的相关噪声不完全相同,导致出现一些差异。第5节中描述的一些简化假设可能也是导致出现差异的原因。在这些示例中,预测都相当准确,我们认为这种方法对这种设计是有效的。

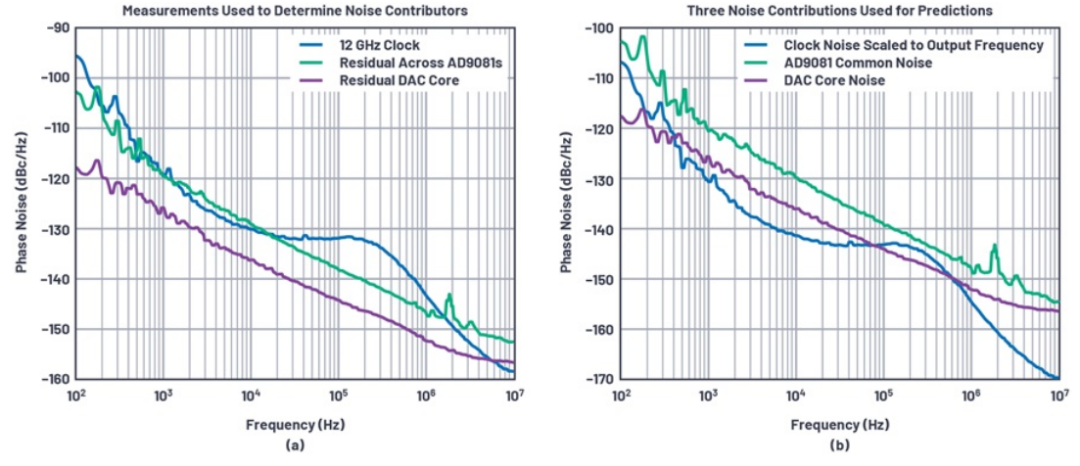

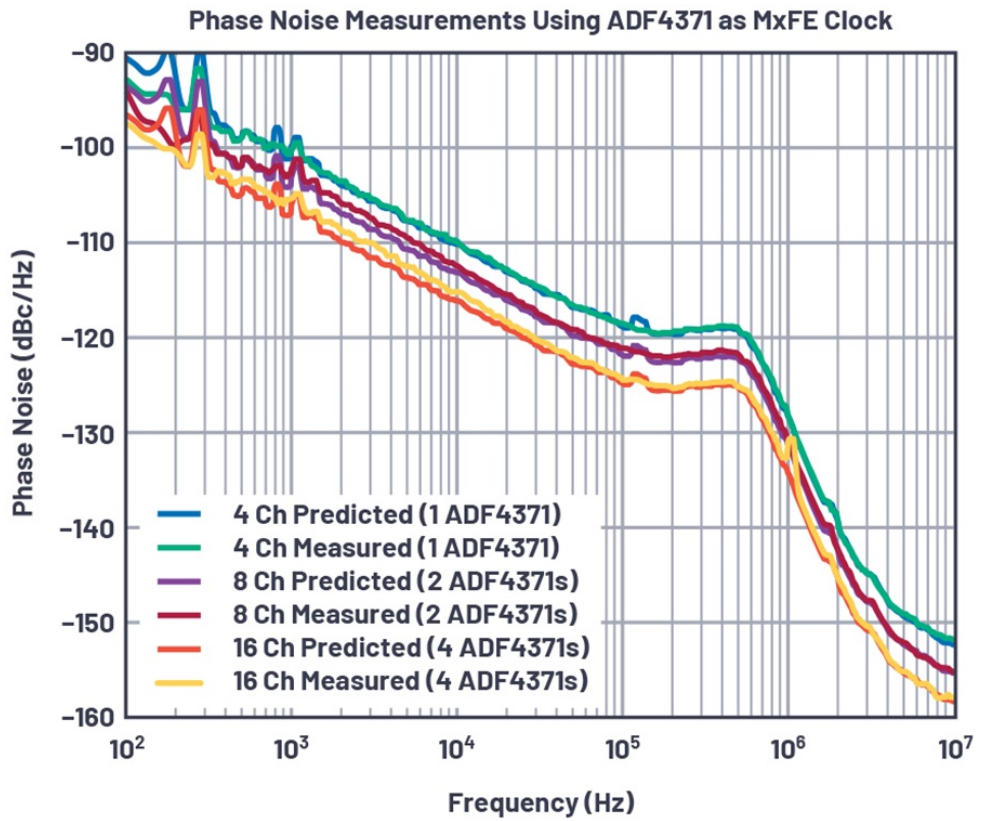

在本测量中,4个MxFE每个使用一个单独的ADF4371,如图1所示。ADF4371锁定使用低相位噪声500 MHz的基准电压源,设置提供12 GHz输出。图9显示用于验证模型的测量值和噪声贡献分量。

图9. A) 使用独立的ADF4371芯片作为时钟输入源时,用于验证相位噪声模型的测量值,b) 计算得出的在模型中使用的相位噪声贡献分量。这是针对每个MxFE的分布式PLL的情况。

在本示例中,PLL是主要的噪声源,MxFE贡献的噪声分量远低于时钟噪声。如图10所示,根据分布式系统使用的PLL的数量,组合噪声相应改善。

图10. 在使用ADF4371作为每个MxFE的时钟源时,在组合多个相位一致的发射通道之后,在3.2 GHz时的测量值和根据模型得出的预测值。

本文显示能够相当准确地预测组合通道中的相位噪声的经验模型。使用此方法的前提是:首先从噪声源的角度查看该系统,并重新绘制框图,以便查看相关项和不相关的项。

我们还着重突出"经验"一词,这意味着建议方法是通过观察或经验进行验证,而不是根据理论或纯逻辑进行验证。对于相位噪声示例,提出的观点是要评估区域和贡献分量,需要使用一些测量值和观察结果。了解上述这些之后,即可系统性地计算系统噪声。

本文使用的数据和公式在一定程度上只适用于该硬件,基于之前描述的观察结果。但是,这种方法可用于任何多通道系统。更通用的框图如图11所示。先介绍系统基准振荡器,然后根据通道级硬件绘制时钟和LO分布,可以更直观地查看大型系统中的噪声贡献源。

图11. 从相位噪声角度绘制的通用相控阵示意图。每个信号都包含噪声项,它们是阵列中分布的噪声分量的组合。从这个角度重新绘制系统图之后,可以更容易在系统层面显示关于相关和不相关噪声的跟踪。如果设计人员先绘制系统基准振荡器,然后根据通道级硬件绘制时钟和LO分布,可以更直观地显示大型系统中的噪声贡献源。

京公网安备 11010802033920号

京公网安备 11010802033920号