干货 | 漫话锁相环——频率合成器

频率合成器的设计要点

频率合成器的设计要点

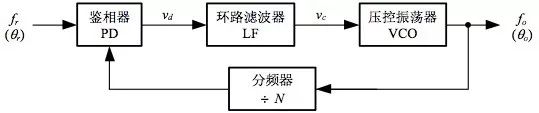

频率合成是最常见的一种锁相环应用电路。本文只讨论最基本的单环电路,其结构如下图所示,图中fr是参考输入信号频率,fo是合成器输出信号频率,fo=N×fr。

通常频率合成器的参考信号fr是由晶振产生的脉冲信号,鉴相器采用鉴相-鉴频结构的PFD,这种结构的鉴相器具有捕捉时间短、不会误锁在倍频频率等优点。

压控振荡器要满足输出频率范围,尤其在输出频率有较大变化范围时这一点尤为重要。

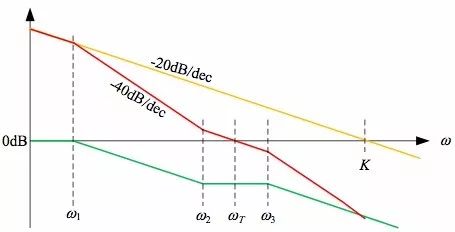

高阶锁相环可以降低输出信号的相位抖动,但阶数越高系统越复杂。频率合成器中常常采用无源RC环路滤波器构成三阶锁相环,根据相位裕量运用开环频率特性进行设计。有些频率合成器可能还有锁定时间的要求,可以在根据相位裕量进行初步设计后通过仿真或实验进行验算,若不满足锁定时间要求则需要根据实际情况修改。

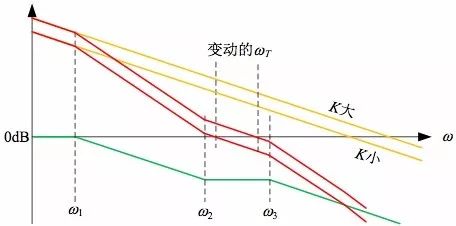

幅频特性的伯德图如下,其中黄色是鉴相器、压控振荡器与分频器的总幅频特性,绿色是环路滤波器的幅频特性,红色是两者合成后的三阶锁相环的开环幅频特性。

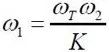

通常在设计中总是已知K且指定ωT、ω2与ω3,在这种情况下有 。

。

相频特性如下:

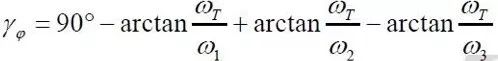

已知ω1、ω2与ω3,则相位裕量

频率合成器的设计实例

频率合成器的设计实例

用74HC4046设计一个频率合成器,输出频率范围为1000kHz~2070kHz,频率步进值为1kHz。设计过程如下:

74HC4046中有三个鉴相器:PC1是异或门,PC2是鉴频-鉴相器(PFD), PC3是JK触发器。作为频率合成器使用时应该用PC2鉴频-鉴相器(PFD),其鉴相增益Kd=VDD/2π(单位是V/rad)。由于为了与分频电路共用电源,VDD=5V,所以Kd=5/2π=0.796。

74HC4046中的压控振荡器(VCO)是一个张弛振荡器,由外接的两个电阻与一个电容确定其振荡频率范围。值得注意的是,通常其控制特性并非完全线性(即Ko不是一个常数),只是在某个控制电压范围内线性较好才能将Ko近似为一个常数。此近似线性的控制电压范围比电源电压范围小很多,超出范围后线性急剧变差。由于74HC4046是一款很通用的锁相环集成电路,好几家公司有相同型号的产品,但是各自的参数略有差异,所以在设计时要注意辨别,必要时可以通过实验测试确定其参数值。

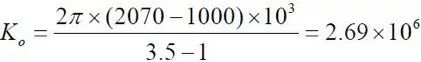

笔者实际使用的74HC4046在VDD=5V条件下的近似线性控制电压范围大约在1V~3.5V左右,本电路要求其振荡频率范围为1000kHz~2070kHz,所以

反馈回路中的分频器采用数字集成电路构成普通的可预置分频电路。由于要求步进频率为1kHz(即输入的参考频率为1kHz),输出频率为1000kHz~2070kHz,所以该分频电路的分频系数为N=1000~2070。综上所述,此锁相环的环路增益

下面设计环路滤波器

下面设计环路滤波器

由于本设计中分频系数N可变,故环路增益K不是一个常数。在环路滤波器的三个时间常数确定后,K变化时穿越频率会随之变化,导致相位裕量随之变化。可参见下面的示意图:

因此在设计环路滤波器时可以先确定一个设计用的K值,可以令 ,以此为据进行设计如下。

,以此为据进行设计如下。

通常情况下,开环频率特性的穿越频率ωT大致上可以取参考输入频率的1/10~1/20,现已知输入参考频率为1kHz,故可以取ωT=2π×1000/20=314。

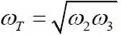

ω3/ω2应该大于Kmax/Kmin且通常不小于10,由于Kmax/Kmin=2.07<10,故取ω3/ω2=10。为了得到最大的相位裕量,通常总是使得 ,由此可得ω2=99,ω3=990。再根据

,由此可得ω2=99,ω3=990。再根据 得到ω1=21。

得到ω1=21。

下面验算相位裕量

下面验算相位裕量

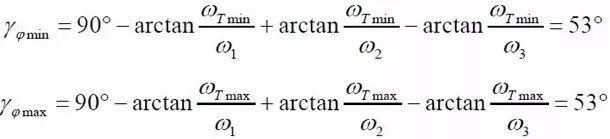

当K=Kmin=1.03×103时,ωTmin=ωT×Kmin /K=219。当K=Kmax=2.14×103时,ωTmax=ωT×Kmax /K=454。

将上述设计参数代入相位裕量公式,得到

由于相频特性曲线在ω2到ω3区间内是凸的,所以上述设计得到的锁相环在整个工作频率范围内的相位裕量均不小于53°。通常相位裕量不小于40°就可以认为系统是稳定的,所以上述设计得到的参数是满足稳定要求的。

实际的环路滤波器电路

实际的环路滤波器电路

在频率合成器中为了避免运放噪声的影响,多采用无源环路滤波器。三阶锁相环中RC无源超前-滞后型滤波器如下图:

这个滤波器的 。根据前面得到的三个频率ω1=21、ω2=99、ω3=990,可以设计这个滤波器的电阻电容值。由于方程个数少于变量个数,通常要先指定一个元件,例如指定C1=1μF,可以算得R1=33.8kΩ,R2=10.1kΩ,C2=141nF。

。根据前面得到的三个频率ω1=21、ω2=99、ω3=990,可以设计这个滤波器的电阻电容值。由于方程个数少于变量个数,通常要先指定一个元件,例如指定C1=1μF,可以算得R1=33.8kΩ,R2=10.1kΩ,C2=141nF。

干货 | 一招处理 MSP432 Debug 出错及芯片故障

长按下方二维码加微信号helloeeworld为好友,注明EEWORLD论坛账号+职业和感兴趣的方向,经审核通过即会被拉入不同领域建立的微信交流群。

京公网安备 11010802033920号

京公网安备 11010802033920号