科技产品下一个重大突破将来自芯片堆叠技术

华尔街日报发布文章称,科技产品下一个重大突破将在芯片堆叠领域出现。

Apple Watch采用了先进的的3D芯片堆叠封装技术

作为几乎所有日常电子产品最基础的一个组件,微芯片正出现一种很有意思的现象。通常又薄又平的微芯片,如今却堆叠得像薄煎饼那样,由二维变成三维——给电子设备带来重大的影响。

芯片设计师们正在发现那种堆叠方式可在性能、能耗和功能上带来各种意想不到的好处。

没有这种技术,苹果智能手表Apple Watch也就无法做出来,三星最先进的固态存储器、来自英伟达和谷歌的人工智能系统和索尼超级快速的新型相机也不例外。

这种3D堆叠类似于城市规划。没有它的话,随着产品需要内置更多的零部件,电路板上的微芯片会不断延伸,微芯片之间的距离会越隔越远。然而,一旦开始对芯片进行堆叠,你就能形成一个硅制“城市”,里面的一切会变得更加邻近。

从物理学角度来看,这种设计的优势显而易见:当电子需要通过铜线行进更长的距离的时候,会消耗更多的能量,产生热量,同时也减少频宽。ARM旗下微芯片设计公司ARM Research未来硅技术主管格雷格·耶里克(Greg Yeric)指出,堆叠式芯片更加高效,产生较少的热量,能够以光速在短得多的互连通道里进行通信。

Apple Watch Series 1的Apple S1芯片X光图

虽然3D堆叠芯片背后的原理简单明了,但要制造起来可不容易。耶里克说道,该技术概念于1960年代被首次提出,此后零星地出现在一些高端应用当中,比如军用硬件。

然而,TechInsights微芯片研究公司分析师辛金·迪克森-沃伦(Sinjin Dixon-Warren)指出,来自大多数大型芯片厂商(AMD、英特尔、苹果、三星和英伟达)以及Xilinx等小型的专业公司的堆叠式芯片产品,才出现了五年左右。为什么大家要这样做呢?因为工程师们开始找不到其它的办法来让芯片有更好的表现。

堆叠式芯片通常是其它蜷缩起来的芯片的“封装”的一部分。除了节省空间以外,这让厂商们能够(通过不同的制造工艺)打造许多不同的芯片,然后多多少少将它们粘合在一起。“3D堆叠式封装”的做法不同于频繁用于手机的“系统级芯片”做法,后者是将所有不同的手机部件蚀刻在单一的硅片上。

迪克森-沃伦称,从第一代开始,Apple Watch就由最先进的3D堆叠式芯片封装之一驱动。在该智能手表中,30种不同的芯片密封在一个塑料包层里面。他说,为了节省空间,存储芯片堆叠在逻辑电路上面。要是没有芯片堆叠技术,该手表的设计就无法做得如此紧凑。

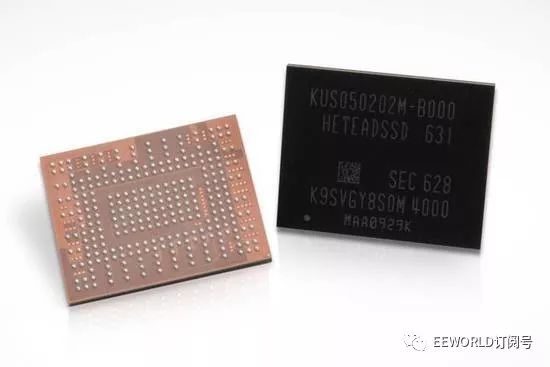

苹果的芯片只是堆叠成两层高,而三星却做出了名副其实的硅制“高楼大厦”。三星用于手机、相机和笔记本数据存储的V-NAND闪存足足堆叠了64层芯片。三星也刚刚宣布,未来的版本将会有96层。

英伟达针对人工智能打造的Volta微处理器,GPU上堆叠了八层的高频宽存储器

存储是芯片堆叠技术的一项自然而然的应用,因为它解决了长久以来一直困扰芯片设计师的一个问题:给从iPad到超级计算机的任何设备增加更多的核心,并不能换来所期望的速度提升,因为逻辑电路之间的通信延迟和所需要的存储能力。而将存储组件直接堆叠在芯片上,则可以让二者之间的连接路径缩短。

英伟达硬件工程高级副总裁布莱恩·凯莱赫(Brian Kelleher)表示,那正是公司针对AI打造的Volta微处理器的运作原理。通过直接在GPU上面堆叠八层的高频宽存储器,这些芯片在处理效率上创造了新的记录。

“我们在电力上是受限的,”凯赫勒说,“我们能够从存储系统腾出的任何电力,都可以用在计算上。”

芯片堆叠也带来了一些全新的功能。有的手机摄像头将图像传感器直接叠加在处理图像的芯片上面。额外的速度意味着,它们能够对照片进行多次曝光,并将其融合在一起,在昏暗的场景里捕捉到更多的光线。

三星的64层V-NAND垂直芯片,拥有更大的数据存储容量和更快的处理速度

来自索尼的原型摄像头通过使用三层而非两层芯片更进一步——包括图像传感器、存储器和逻辑电路,实现每秒最高1000帧的效果。这种做法的作用是,光触达图像传感器,数据直接进入存储器,接着进行实时处理。除了在低光照条件下取得更高的能见度以外,这还可以用于拍摄超慢动作的视频,单帧凝固快速移动的物体。

目前,要将3D微芯片推向更多的电子设备,还需要耗费巨大的资源去解决一些障碍。

耶里克表示,首先,3D芯片诞生不久,用于堆叠的设计工具进化还不充分。在简单的设计工具——类似于用于平整芯片的那些工具——变得广为普及以前,堆叠式芯片仍将只有拥有顶尖工程人才的企业能够制造出来。

另一个问题在于,制造商们仍在学习如何可靠地在物理上相互堆叠和连接芯片。这意味着有的制造工艺成品率会相对较低。

不过,迪克森-沃伦指出,3D堆叠式芯片的普及非常快速,它们也必然会成为行业主流。10年前,该技术几乎仅仅存在于高校实验室;五六年前,还难以找到它的商业化案例。但它如今如雨后春笋般涌现,出现在各类的应用上,如网络化、高性能计算和Apple Watch等高端可穿戴设备。据知名电子产品拆解网站iFixit的CEO凯尔·韦恩斯(Kyle Wiens)称,它也出现在iPhone X的“大脑”当中。

在ARM的耶里克看来,最终3D芯片应该会让我们的可穿戴产品变得跟体积更大的设备那么强大,会让它们能够连续运行数天时间,即便它们布满了传感器。“举例来说,如果有朝一日你的手表变得能够检查你的血糖水平,我不会感到惊讶。”他说道。

让芯片从二维变成三维,只是个开始。不久以后,芯片层将会通过光而非电流来通信。在更遥远的未来,随着我们用拥有前所未见的处理性能的闪亮晶体替换电路板,它们将会完全摆脱硅——可能转向人造钻石。

由EEWORLD论坛版主:dcexpert 写的《microbit入门指南》 终于上市了!

为了答谢大家的支持,即日起~11月30日点击阅读原文参与活动将有机会获得dcexpert亲笔签名《microbit入门指南》一本。

长按下方二维码加微信号helloeeworld为好友,注明EEWORLD论坛账号+职业和感兴趣的方向,经审核通过即会被拉入不同领域建立的微信交流群。

京公网安备 11010802033920号

京公网安备 11010802033920号