这两日,一则消息刷爆了芯片圈,清华又有新成果。

清华大学集成电路学院教授吴华强、副教授高滨团队基于存算一体计算范式,研制出全球首颗全系统集成的、支持高效片上学习(机器学习能在硬件端直接完成)的忆阻器存算一体芯片,在支持片上学习的忆阻器存算一体芯片领域取得重大突破,有望促进人工智能、自动驾驶可穿戴设备等领域发展。研究成果已发表在《科学》(Science)上。

对国内芯片产业来说,处处都是“卡脖子”,全世界也都在集中力量研发下一代产品,这一次,我们走在了前面。

付斌丨作者

电子工程世界(ID:EEworldbbs)丨出品

成果是什么

成果是什么

根据清华大学官方公众号介绍,该芯片包含支持完整片上学习所必需的全部电路模块,成功完成图像分类、语音识别和控制任务等多种片上增量学习功能验证,展示出高适应性、高能效、高通用性、高准确率等特点,有效强化智能设备在实际应用场景下的学习适应能力。

相同任务下,该芯片实现片上学习的能耗仅为先进工艺下专用集成电路(ASIC)系统的1/35,同时有望实现75倍的能效提升。

图片忆阻器存算一体芯片及测试系统,图源丨清华大学

基于忆阻器存算一体实现高效片上学习的通用算法和架构,图源丨清华大学

“存算一体片上学习在实现更低延迟和更小能耗的同时,能够有效保护用户隐私和数据。”博士后姚鹏介绍,该芯片参照仿生类脑处理方式,可实现不同任务的快速“片上训练”与“片上识别”,能够有效完成边缘计算场景下的增量学习任务,以极低的耗电适应新场景、学习新知识,以满足用户的个性化需求。

比如,有些人习惯在数字“7”的中间加一短横。一开始,智能芯片并不认识这个符号,然而训练了两三个这样书写的“7”后,它就能准确将其识别为数字“7”。

小车自动追踪控制的增量学习演示,图源丨清华大学

什么东西,有什么用

什么东西,有什么用

顾名思义,存算一体就是将存储器和处理器合并为一体。想象一下,人类在思考时候从来都是存储和计算一体的,并不会存在分开的情况,而这种架构就是借鉴了我们人脑的处理方式。

我们为什么需要存算一体?冯诺依曼瓶颈经典计算机体系结构中,处理和内存是分开的。而合并在一起,是为了越过两面墙——存储墙和功耗墙。

-

存储墙:冯·诺依曼架构的存算分离会导致外部存储器运行速度远远小于处理器的运算速度,系统整体会受到传输带宽瓶颈的限制,导致算力会远低于处理器标定的理论算力;

-

功耗墙:冯·诺依曼架构中,数据在处理器和外部存储器中频繁高速传递,会导致系统功耗很高。同时,摩尔定律触碰1nm,芯片特征尺寸已进入量子效应显著范围,引起一系列次级物理效应,包括栅隧穿泄漏、载流子界面散射、强场速度饱和、源漏寄生电阻占比增大等,导致功耗密度快速上升。

当我们打破两堵墙,数据就不用来回搬运处理,也不会“交通堵塞”,此时整体功耗就更低了,说白了,就是不绕弯路了。

那忆阻器又是什么?它全称是记忆电阻器(Memristor),由Memory和Resistor两个英文单词组成,它代表着第四种器件。

电路中,四大基本变量电流i、电压u、电荷量q和磁通量φ中,前三者分别对应电阻器、电容器和电感器,而磁通量φ表征磁通量与电荷之间的关系——即忆阻器,它的特性是忆阻器可以记忆流经它的电荷量。

根据材料和物理机制,忆阻器件可分为阻变随机存储器(RRAM),相变存储器(PCRAM),磁随机存储器(MRAM)和铁电随机存储器(FeRAM)四种。此外还有光电忆阻器、有机材料忆阻器、流体忆阻器等。

不同类型忆阻器件参数指标比较,制表丨电子工程世界

参考丨《物理学报》

存算一体则也分为多种介质,不同介质实现效果和关键点也不同,包括各种易失性存储器件和非易失性存储器件(NVM)。

其中,前沿研究更多偏向于技术成熟的SRAM来探索和设计存算一体架构,但SRAM存在瓶颈,较大的单元面积会导致随着工艺发展,CMOS扩展难度会相应增大,芯片计算密度增长会逐渐放缓;相比之下非易失性存储(NVM)在计算密度方面表现出更大的潜力,不过NVM尚不成熟,基于该技术设计的存算一体架构短时间很难得到广泛应用。

除了存算一体,未来科学要将忆阻器应用范围扩大到“感存算一体系统”,也就是说,未来的系统不仅存和算在一起,感知系统也会同时进行,计算效率继续倍增。

应用于感存算一体化系统的忆阻器的性能比较,制表丨电子工程世界

参考丨《物理学报》

更值得强调的是,无论是存算一体,还是忆阻器,都与类脑芯片,或者说是神经形态计算相关联,毕竟这两者已经是模仿人脑。

类脑芯片就是从算法(SNN)、架构上彻底模仿人脑计算的“突触可塑性”,这是大脑记忆和学习的重要基础。它允许突触根据其活动增强或减弱,并由突触上的神经递质受体控制。

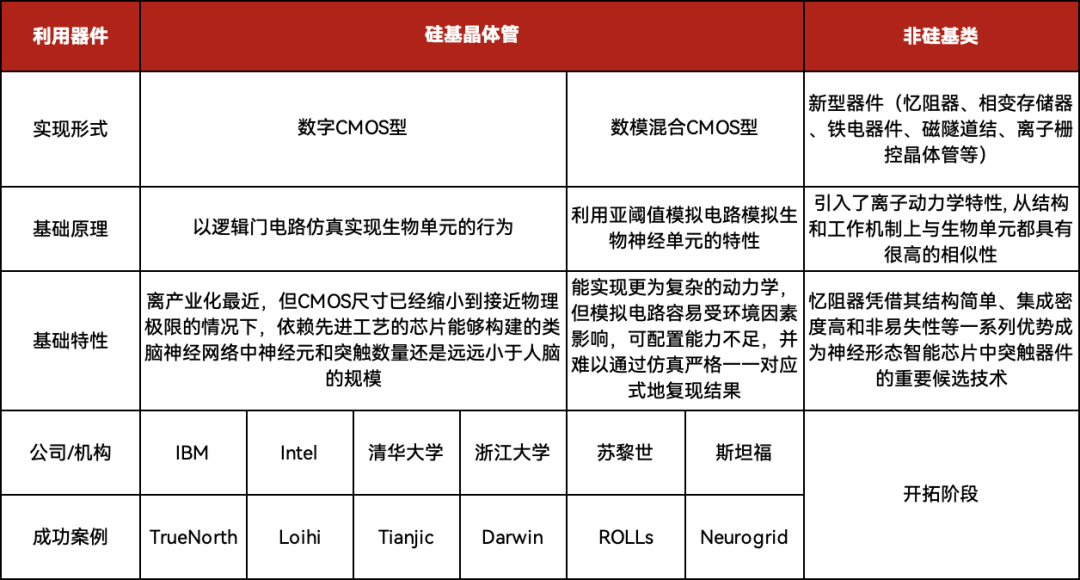

当然,类脑芯片又是非常复杂的一个分支,用忆阻器实现的类脑芯片属于最难的那一种,也是非硅基类的类脑芯片。

不同类型的类脑芯片实现方式,制表丨电子工程世界

说了这么多,那存算一体到底有啥用?一句话总结就是——能让芯片快速获得十倍甚至百倍的能效比。低功耗,就是它最大的作用,而压低功耗就意味着移动设备能够拥有更多想象力,而我们也就越来越能用现有能源系统,触达更大算力。

举一个最典型的例子就是,AlphaGo下棋打败了人类,但人类只用了20瓦的大脑能耗,而AlphaGo是2万瓦。

当然,我们清楚一项成果转化到业界并非一蹴而就,而这项成果不仅涉及存算一体、忆阻器,也涉及仿生类脑处理,再把这些东西集合在一起制造出来,就更复杂了,可想而知技术含量有多高。

存算一体迎来新增长机会?

存算一体迎来新增长机会?

虽然一时间,我们可能很难看到这款芯片,不过存算一体芯片在近几年已经逐渐产业化,不知道这个消息是否会成为市场的有一强心剂。

实际上,国际上多数巨头早已开展相关的研究,就比如说工程师所熟知的英特尔、三星、IBM、东芝、SK海力士等公司,而国际市场上最典型的消息包括:

-

三星2021年2月发布HBM2-PIM,将4片常规DRAM die和4片具有计算功能的DRAM die通过TSV通孔垂直组合在一起。其运行频率为300 MHz,每个裸片上 (PIM-DRAM die) 有32个PCU。2022年初,三星电子发表首个基于MRAM的存算一体芯片,采用28nm CMOS工艺重新构建MRAM阵列结构;

-

Mythic2021年5月获得7000万美元的C轮融资,2021年6月发布由72个AMP切片构成,每个切片内部集成一系列闪存单元、ADC阵列、1个32位RISC纳米处理器、1个16位SIMD矢量处理器、SRAM和1个片上网络 (NOC) 路由器,算力达25TOPS;

-

IBM公司2018年通过PCM实现在数据存储的位置执行计算来加速全连接神经网络训练,该芯片能效比是传统GPU280倍,单位面积算力是传统GPU100倍;

-

2016年,英特尔基于SRAM实现了支持逻辑操作的存储器,并在此基础上实现了支持无进位乘法运算的计算型缓存。

反观国内,回看前几年,涌现了大量存算一体公司,这批公司在两年前大多还处在A轮以前,彼时多家公司获亿元融资,短短两年时间许多明星公司又获2~3轮新融资,赛道热度依旧,资本依然看好这项新技术。

并且,有很多产品也逐渐浮现:

-

今年5月,后摩智能正式发布首款存算一体智驾芯片——鸿途H30。12nm工艺制程下,该芯片物理算力达256TOPS,在Int8全精度的计算提供下,计算延时只有1.5ns,能效比为30~150TOPS/W,比业界同等精度计算条件下的水平提高了3倍以上,而且它是车规量产支持L4,而这也存算一体在大算力这一领域走在了前列;

-

苹芯科技已开发实现多款基于SRAM的存内计算加速单元,致力于为人工智能行业提供了低成本、高效率、低能耗、高性能的芯片解决方案;

-

九天睿芯拥有自有专利的模拟预处理与6T SRAM存算一体技术,解决了传统计算架构的瓶颈和耗电散热难题,做到更低的延迟和更快的处理速度;

-

达摩院研发的存算一体芯片是全球首次采用混合键合(Hybrid Bonding)的3D堆叠技术,将计算芯片和存储芯片 face-to-face 地用特定金属材质和工艺进行互联。

国内类存算一体公司不完全统计,制表丨电子工程世界

展望未来,从技术上,存算一体存在三个难点:一是器件特性难以满足全部需求,存算一体的形态太多了,但每种器件的侧重点又不一样,不一定能够满足全部应用需求;二是阵列存在泄露路径、写串扰以及寄生电容电阻问题;三是现有集成电路设计与集成技术难以满足需求,本身存算一体是为了低功耗而来,但外围控制辅助电路的面积和功耗都很高,也会减少存算一体的一部分收益,同时存储存在工艺差距,统一制程增加硬件开销,3D异质集成是可行之路。

从市场角度来看,存算一体还是一种比较超前的技术,还在找应用的阶段。目前仅有后摩智能一家企业已经公开展开规模化落地,瞄准的则是车规级,而许多企业则更看好AIoT低功耗方面的应用、感存算一体、图计算和基因工程等方面的应用。当然,

在此前笔者与苹芯科技的对话中,该公司也表示,存算一体中早期产品更多出现在端侧对低功耗和高能效有强烈需求的场景。随着智能城市、智能生态等应用普及,长远地看,存算产品的适用范围也可能会延伸至超大算力领域。

[1] 人民日报:

https://mp.weixin.qq.com/s/Km1VHS02wDsGE66Fr-d-7w

[2] 清华大学:

https://mp.weixin.qq.com/s/w0VZNIQ1KbClJJ8c05hPqg

[3] 恒烁半导体(合肥)股份有限公司:首次公开发行股票招股说明书(申报稿).2021.10.19.https://data.eastmoney.com/notices/detail/A21521/AN202110191523750446.html

[4] 高雅丽,李晨,王之康. 解决重大原创问题 勇闯创新“无人区”[N]. 中国科学报,2021-06-01(004).DOI:10.28514/n.cnki.nkxsb.2021.001764.

[5] Acta Phys. Sin., 2022, 71(14): 140101. doi: 10.7498/aps.71.140101

[6] 温新宇, 王亚赛, 何毓辉, 缪向水. 忆阻类脑计算. 物理学报, 2022, 71(14): 140501. doi: 10.7498/aps.71.20220666

[7] 张宇琦, 王俊杰, 吕子玉, 韩素婷. 应用于感存算一体化系统的多模调控忆阻器. 物理学报, 2022, 71(14): 148502. doi: 10.7498/aps.71.20220226

[8] 信息通信技术与政策:专题丨存算一体技术产业发展研究.2023.7.24.

https://mp.weixin.qq.com/s/mZJMeES8IUOw6MIQLKZu6A

成果是什么

成果是什么

什么东西,有什么用

什么东西,有什么用

什么东西,有什么用

什么东西,有什么用

存算一体迎来新增长机会?

存算一体迎来新增长机会?

京公网安备 11010802033920号

京公网安备 11010802033920号