近些年来,计算机技术、多媒体技术和数据通信技术的发展飞速,促使数字视频的应用也越来越广(如视频监控、视频会议和移动电视等)。随后,各种压缩算法的研究使得数字视频的存储和传输极为方便,同时也相继出现了各种视频记录系统。本文设计的嵌入式视频记录系统,可以将摄像头拍摄到的模拟视频数据转变成数字视频数据,经压缩后存储在大容量的存储器上,并可通过专用的回放设备再现汽车行使的整个过程。该视频记录系统可用来记录汽车内各项仪表和前方外视景等视频信息及突发事件标记,它可以将汽车行使过程中的所有信息以数字视频的方式连续动态地记录下来。本系统可以和汽车黑匣子结合,以方便管理部门根据所记录的有关数据对车辆进行有效的管理,更能为事故后的分析提供准确的依据,判断汽车肇事的真正原因。同时可以通过记录查看平常是否紧急加速、是否急刹车等行驶数据,以此分析并改善不良驾驶习惯,起到预防事故的作用。

常见的视频压缩方法有MPEG系列租H.26X系列。考虑到压缩技术的成熟度、成本和主要用途,本记录系统采用MPEG-1数字图像压缩记录技术,来实现对1路视频信号的连续图像长达4小时的实时循环记录。此外,本视频记录系统还具有成本低、体积小、功耗低等特点。

1 系统工作原理

视频记录系统设计的侧重点是降低成本,减小体积,同时降低系统的功耗,提高系统的整体性能。它能够对汽车上的1路视频信号进行长达4小时的连续实时动态循环记录。本系统主要由视频解码及压缩编码器、ARM处理器、电子盘三部分组成。其中视频解码器和压缩编码器共同组成压缩单元,ARM处理器是系统的控制单元,电子盘是系统的存储单元。其视频记录系统的结构组成如图1所示。系统工作时,先将摄像机拍摄到的视频信号通过视频解码器SAA7113H进行解码和A/D转换,以输出8位4:2:2格式的YCbCr数字视频信号,该数字化视频信号送入SZ1510压缩编码芯片进行压缩后可产生MPEG-1数据流,然后由ARM处理器将压缩好的数据通过IDE接口存入存储载体——电子盘,从而实现对1路视频信号的连续实时循环记录。

系统上电并启动后,ARM处理器首先通过SZ1510芯片的HOST接口对SZ1510内部寄存器进行配置,并通过I2C总线对视频解码器SAA7113H进行初始化。当设置好MPEG-1压缩格式及数据速率后,系统开始正常工作,并对输入的模拟视频信号经视频解码器进行解码和A/D转换,再将生成的CCIR-601数字视频流传人压缩编码芯片SZ1510进行处理,然后由SZ1510将数字视频数据转化为符合MPEG-1格式的影视文件,最后将MPEG-1数据流在ARM处理器的控制下通过IDE接口以文件形式写入电子硬盘进行存储。系统工作时,ARM还将不断监视相关信号,并在图像中加入相应的标志,直到接收到关机信号,系统自动结束压缩工作。

2 硬件电路设计

2.1 视频解码及压缩编码电路设计

由于MPEG-1压缩算法需要很大的运算量,用软件很难实时完成,所以本系统采用专用的视频压缩芯片来实现对视频信号的实时高效压缩。目前,常用的MPEG-1压缩芯片有VW2010、W99200F、WIS 7007SB等。本设计选用SAA7113H进行解码,并采用Zapex公司的SZ1510MPEG-1 A/V编码芯片进行图象压缩。SAA7113的主要作用是把输入的模拟视频信号解码成标准的8位“VPO”数字信号,它相当于一种“A/D'’器件,是一种可编程视频处理芯片,可通过I2C总线实现编程控制,并具有4路视频输入、抗混叠滤波、自动钳位和增益控制、多制式解码以及亮度、对比度和饱和度控制等功能。它对输人的PAL制式视频信号进行采样和解码后,可将生成的CCIR-601数字视频流(色度空间为YCbCr,取样为4:2:2)送到视频压缩芯片SZ1510的数字视频输入接口。它的输入时钟由24.576 MlHz的有源晶振提供,并可分别从RTS1和RTS0管脚输出为SZ1510提供的行同步信号HS和场同步信号VS,其中行同步信号HS又可作为行有效象素识别信号输入到SZ1510的VIHACT管脚;并从LLC脚输出27 MHz的像素时钟,作为SZ1510内部的数字视频流的采样时钟和芯片的主时钟。系统初始化可通过ARM芯片的I2C总线来实现。片选信号由ARM产生RESET信号来提供。

系统中的压缩编码芯片SZ1510是ZAPEX公司生产的一款高性能的MJPEG、MPEG-1编码芯片,可对视频信号实现高达25 f/s的压缩,并支持多种工作模式和比特率模式,还可灵活实现模式组合,同时可在视频中叠加视频标记和时间标记。该芯片内部主要由视频编码核、TMS320C54X高性能DSP核、接口电路(视频接口、存储器接口、主机与串口接口)、DMA控制器和时钟产生电路等组成。其内部的压缩核已经过优化,适合于高效、实时的MPEG-1数字图像压缩,且具有功能多、功耗低、温度范围宽等特点。

系统中的SZ1510是从设备,受主机ARM的控制。它的HOST接口是控制和数据交换的接口。SZ1510可以选择多种总线类型,它有复用和不复用的Intel和Motorola总线类型(复用模式下,HAD[7:0]即可作为数据线,又可作为地址线;非复用模式时,HAD[7:0]只能作为数据线),不复用总线又可分为8位和16位,并可由HCONFIG[l:0]引脚和Syscofig[3]寄存器进行选择配置。本系统把HCONFIG0置低,HCONFIG1置高,Sysconfig[3]写1,故可使其工作在Intel 8051类型的非复用16位数据总线模式下。

由于SZ1510有多种工作模式,根据系统要求,本设计使SZ1510工作在LVE(Live Video Encoding)实时视频编码模式。在这种模式下,SZ1510可从视频解码器获得实时数字视频数据,然后根据MPEG1/M-JPEG进行压缩并传到主机。具体工作过程是:SZ1510对输入到其内部的CCIR-601数字视频流经过视频预处理、自动裁减、场景变化检测、运动估计、运动补偿、离散余弦变换/反离散余弦变换和可变长编码等处理后,再将生成的MPEG-1视频基本流存储于SDRAM中,然后经过输出端口大小为256字节的FIFO缓冲进行数据输出。正常工作时,FIFO每满一次就产生一个FRDY (FIFO读)中断以通知主机读取FIFO中的数据,并由主机从Data_out寄存器读取数据。之后,当SZ1510发出一个EOD(数据结束)中断时,数据传输结束。

在视频压缩工作模式下,SZ1510有3种输出比特率可供选择:恒定比特率、最大比特率、可变比特率。恒定比特率需要填充冗余,最大比特率不需要填充冗余,可变比特率的压缩质量比恒定比特率可变。比特率的选择可通过设置Ven_cntl寄存器的1、2位来确定,当其为0时,选择的是恒定比特率;为1时,选择的是最大比特率;为3时,选择的是可变比特率。

2.2 控制及存储电路设计

考虑到控制部分的体积、可靠性和控制能力,本系统中的CPU采用Philips公司的ARM7TD-MI-S内核微控制器LPC2210。这是一个能够支持实时仿真和跟踪的16/32位ARM7TDMI-S CPU。对于代码规模有严格控制的应用,可使用16位Thumb模式,该模式可将代码规模降低30%以上,而性能的损失却非常小。LPC2210采用144脚封装,具有极低的功耗。另外,该芯片还具有多个32位定时器、8路10位ADC、PWM输出以及多达9个外部中断。通过配置总线,LPC2210最多可提供76个GPIO。

LPC2210可与SZ1510的HOST接口相连,并可通过HOST接口对SZ1510进行控制和设置。正常工作时,LPC2210把从HOST接口输出的MPEG-1格式视频流以文件形式送人电子盘进行存储。LPC2210与SZ1510的接口电路如图2所示。其中,HAD[0…15]接到ARM的P2.0~P2.15A作为16根数据线;P3.0接到HALE脚可实现SZ1510内部IOAR(I/O Address Registerl)和IODR(I/O DataRegister)寄存器的选择;P1.1和P3.27分别接读、写选通管脚HRD和HWR;通过将P3.24接到HCS可选通SZ1510;将P0.9接到HINT可发送SZ1510中断请求信号。

[page]

从重量和可靠性出发,本记录单元最终选用电子盘来实现。该电子盘的主体为Flash芯片,该芯片耐冲击,耐高温,体积小,寿命长,适合在汽车环境下工作。虽然电子盘的价格昂贵,但是考虑到系统只采集1路视频信号,记录的数据量也不是很大(计算后得出记录单元的容量为3G时),记录长度可达4.5个小时,所以,选用电子盘完全能够实现任务要求。

LPC2210的GPIO引脚与IDE接口的连接电路如图3所示。图中,P2.16~P2.31为数据线,P1.16~P1.20为地址和选通信号,P0.17和P0.20为设备的复位和状态请求信号,用P0.21和P0.19则可实现读写控制。

3 系统软件设计

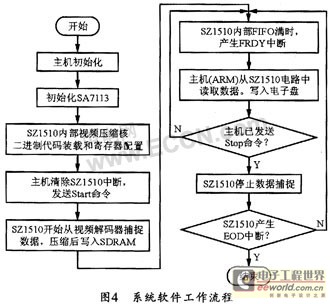

本系统的所有软件程序事先均应通过JTAG口烧录到ARM中,这样,系统上电后便可自动运行这些程序以控制系统的工作。系统软件工作流程图如图4所示。

3.1 SZ1510的寄存器配置

SZ1510有128个寄存器,每个寄存器都有一个索引号,外部主机是通过HOST接口(HALE管脚)来设置SZ1510内部的两个寄存器IOAR (I/O地址寄存器)、IODR(I/O数据寄存器)以实现对SZ1510的控制和配置。访问时,首先由主机的A0管脚发送一个低电平到HALE管脚以选中IOAR寄存器,然后将要访问的寄存器索引号写入IOAR;接着由主机的A0管脚发送一个高电平到HALE管脚,以选中IODR寄存器,然后再将要写入的数据写入IODR,这样,SZ1510就会自动把配置的数据送到指定地址的寄存器。

对Z1510进行初始化时,先由主机写任意值到0x0B寄存器;接着在主机至少等待1微秒后,向Int_enable中断使能寄存器写入0x40,以使能RDY(Ready)中断;然后,主机便等待SZ1510的Ready(Int_source[6])中断;之后,当主机等到RDY中断后,它将清除RDY中断并开始向SZ1510的内部DSP装载二进制代码。

3.2 SZ1510的二进制代码装载

由于复位后内部寄存器的内容是未知的,因此,主机必须进行程序代码的装载,以初始化视频编码核的可编程RAM。SZ1510内部的程序空间是以块(Blank)为单位进行划分的,每块的大小是256字节。用于视频编码核的二进制代码的装载空间为0x000~0x004和0x00c六个块,共1.5k字节代码。具体装载时,先由主机向0x2E寄存器写0x01,以表示外部的SDRAM是1M×16bits;接着由主机向0x0C寄存器写0x03,以使能FIFOReady和End of Data中断;然后由主机向0x11寄存器写0x1,以设定工作模式为内部内存写模式;再由主机向0x10写0x20,以设定SZ1510输出数据的FIFO大小为256字节;最后对每块程序空间进行二进制代码装载,其具体过程如下:

(1)主机写0x3F寄存器,选择下载程序空间;

(2)主机向0x08寄存器写0x04,发送开始命令;

(3)主机等待Ready中断;

(4)主机通过读0x0e寄存器,清除Ready中断;

(5)主机向Data_in寄存器0x01写256个字节;

(6)主机等待EOD(End 0f Data)中断,

(7)主机通过读0x0e寄存器,清除EOD中断;

(8)主机查程序空间的代码是否装载完毕,如没有则继续装载。

4 结束语

本系统可实时长时间记录摄像头传输的汽车外部及车内各仪表显示的视频信号,所记录的压缩数据流符合MPEG-1图像压缩标准。本设计中采用的压缩视频流速率为1.5 Mbps。对于一个3GB的电子盘,本系统可连续记录超过4.5个小时的汽车视频数据。由此可见,本系统体积小、功耗低,便于移动环境下对视频数据的实时长时间压缩数据记录。

上一篇:宝马全系轿车装备NVIDIA芯片

下一篇:基于TI 16位MCU的新型倒车雷达设计

- 热门资源推荐

- 热门放大器推荐

Verilog HDL数字集成电路设计原理与应用

Verilog HDL数字集成电路设计原理与应用 AP358N

AP358N

京公网安备 11010802033920号

京公网安备 11010802033920号