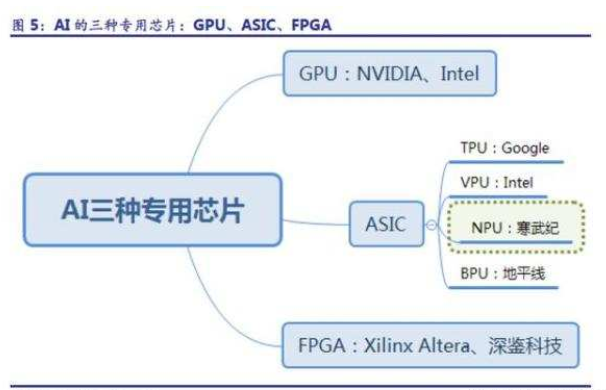

人工智能芯片主要包括GPU、FPGA、ASIC以及类脑芯片。在人工智能时代,它们各自发挥优势,呈现出百花齐放的状态。现在,人工智能已经不再局限于机器学习上,而且更多可以以更快的速度运行AI系统的新型架构正在被开发出来。英伟达、高通、英特尔、IBM、谷歌、Facebook和其它公司正在加速涌入这个领域。

实际上,这些器件并不是真正的芯片,而是一种系统级封装。它们通常包含一颗或者两颗具有大规模处理能力的基于最新半导体制造工艺(16nm及以下)的ASIC,和大容量的超高带宽内存(比如HBM2堆栈),所有这些芯片都通过先进封装技术集成在一起。

人工智能相关ASIC近来渐获市场注意,多家厂商如NVIDIA、英特尔、Google及部分新创企业均相继抢进开发,有望在未来形成数十亿美元市场商机规模。随着NVIDIA将GPU重新定位成为云端AI引擎角色下,也确定带动ASIC业务跟进发展,如Google如今已推出第二代TPU、英特尔在买下Nervana公司后也取得自有Nervana芯片,另外由多名前Google TPU员工创办的新创企业Groq,近日也宣布将在2018年初推出自有下一代AI芯片等等。

Google的TPU,是专门为其深度学习算法Tensor Flow设计的,TPU也用在了AlphaGo系统中。今年发布的第二代Cloud TPU理论算力达到了180T Flops,能够对机器学习模型的训练和运行带来显著的加速效果,其实也是一款ASIC芯片。选择做ASCI定制化研发,一方面是资金不愁,另一方面也是出于Google所需提供的服务考虑。包括Google图像搜索、照片,云视觉API、Google翻译等产品和服务都需要用到深度神经网络。Google有这个需求以及能力去开发一种专门的芯片并具备规模化应用(大量分摊研发成本)的可能。

Nervana由英特尔购并后,计划在2017年底前推出第一款AI专用化Nervana神经网络处理器(NNP)。Nervana NNP也是一款ASIC芯片,能以极高运算效率从事深度学习演算法的训练与执行。英特尔舍弃了CPU上常见的快取,改由特殊软件负责特定演算法的芯片存储器管理,希望能借此将芯片的运算密度与性能提升到新的层次。

由前Google TPU员工创办的新创企业Groq打算在2018年发布第一代AI芯片。这款芯片对标英伟达的GPU,是专门为人工智能重新定制一款芯片。官网资料显示,这款芯片的运算速度将可以达到400万亿次每秒,每瓦特能进行8万亿次的运算。而谷歌最新一代的TPU才达到每秒180万亿次运算,Groq芯片的性能将会是谷歌TPU的两倍多。

联发科也将有所动作。联发科共同CEO蔡力行表示,ASIC的布局联发科会发挥既有资源,通过现有团队实力,配合客户需求积极开发ASIC领域。但毕竟才刚开始,现阶段不会太挑客户,还是以整体业务成长为优先考虑。

全球AI芯片首个独角兽寒武纪,走的也是ASIC路线。

事实上,由于定制化、低功耗等好处,在AI领域ASIC正在被越来越多地采用,带动了ASIC设计及市场快速增长。根据Semico Research的最新调查报告,在2021年以前,人工智能声控装置ASIC的设计预计将以接近20%的年复合成长率成长,几乎达到2016年至2021年间所有ASIC设计成长率(10.1%)的两倍,去年全球ASIC出货量增长为7.7%,明年物联网ASIC单位出货量将超过18亿个单位。Semico Research指出,ASIC增长主要动力来自于工业与消费市场的成长,由于市场饱和加上需求减少,许多传统终端应用的成长速度开始减慢,而与物联网有关的应用正在起飞。

Semico Research指出,除了物联网和人工智能以外,与智能电网、穿戴式电子产品、固态硬盘、无人机、工业物联网、先进驾驶辅助系统(ADAS)和5G基础设施相关的ASIC产品成长率预计也将较广泛的市场更迅速。在2021年以前,消费电子领域的基础SoC设计专案将以19%的CAGR成长,而工业物联网ASIC设计专案则将成长25%。

ASIC设计研发成本难以负荷,设计服务浴火重生

尽管如此,ASIC在AI领域的应用还是面临着不少难题。

ASIC是依照产品需求不同而定制化的集成电路,由特定用户需求和特定电子系统的需求而设计、制造。一般来说,ASIC在特定功能上进行了专项强化,可以根据需要进行复杂的设计,可实现更高处理速度和更低功耗,相对地,ASIC的设计、制造成本也非常高。一般的IC公司很难承担为深度学习开发专门处理器ASIC芯片的成本的风险。首先未来为了性能必须使用最好的半导体工艺制程,而现在用最新的工艺制造芯片一次性成本就要几百万美元,非常贵。就算有钱,还需要组建一个团队从零开始设计,设计周期往往也非常长,可以说time to market时间太长,风险很大。且ASIC芯片还将必须不断升级以跟上新技术及工艺水平,加上ASIC芯片设计者在开发过程初期便已固定其逻辑,因此若在AI这类快速演进的领域有新想法出现,ASIC芯片将无法对此快速做出反应。如果无法实现规模化的应用,就算开发成功也美元实际应用价值。所以,IC公司一般倾向于采用通用芯片如CPU、GPU,或者半定制化芯片FPGA。

显然,随着工艺的不停升级,ASIC的流片费用已经抬高了ASIC保底的最少芯片销售量,到最后全球也就为数不多的几家ASIC厂商能够承受这种巨额的ASIC流片成本和失败风险。借此,ASIC设计服务再次回到业界关注焦点。

例如,美国无晶圆厂FinFET级ASIC设计服务企业eSilicon日前宣布,成功将自有深度学习ASIC送交制造所发布,eSilicon提到这款ASIC采定制IP、先进2.5D封装工艺以及为业界大型芯片之一,并为该公司首款采用台积电2.5D CoWoS封装技术的量产芯片。

台积电业务发展副总裁BJ Woo博士指出,台积电CoWoS封装技术是针对满足这类芯片设计深度学习应用的需求,此先进封装解决方案可实现高性能及整合需求,以达到eSilicon的设计目标。前文中提到的Google TPU、Nervana NNP、Groq即将推出的第一代AI芯片,均是由ASIC公司所送交制造,并交由台积电制造。

目前,人工智能类ASIC的发展仍处于早期。其根本原因是,ASIC一旦设计制造完成后电路就固定了,只能微调,无法大改。而硬件的研发设计与生产成本很高,如果应用场景是否为真市场尚不清晰,企业很难贸然尝试。此外,能设计出适用于人工智能芯片的公司必然是要既具备人工智能算法又擅长芯片研发的公司,进入门槛较高。因此,AI算法+ASIC设计服务+代工的商业模式的发展得宜,可以让愈来愈多AI ASIC得以陆续问世及开发。

代工厂这边,全球有很多代工厂,但是因为难度太高,能做AI系统封装的厂商并不多,台积电、三星和格芯都在榜单之列。那么,是哪些厂商在设计AI系统封装呢?你需要看看哪些厂商真正擅长2.5D集成和拥有设计所需的关键IP(比如HBM2物理层接口和高速SerDes)。HBM2 PHY和高速SerDes模块执行该封装系统内多个组件之间的任务关键性通信。这些都是模拟设计中非常苛刻的挑战,从ASIC供应商那里购买IP可以把风险降至最低。上面提到的三项关键技术eSilicon都有涉及。擅长这些领域的ASIC厂商并不多,不过由于人工智能市场可能会出现爆炸性增长,所以这些ASIC厂商将会受益匪浅。

台湾也有众多IC设计服务企业,在人工智能市场驱动下,ASIC生意再度好起来,且业者预期这波荣景可望持续很久。台积电大胆预言,2020年高性能计算(HPC)、AI相关芯片业绩将高达150亿美元,创意及世芯、智原亦看好来自全球AI客户对于ASIC芯片的需求热潮,可望自2017年起延续好一阵子,尤其是强调先进制程技术、极度复杂芯片设计、高效能与低功耗等,将是IC设计服务业者的新蓝海市场。

上一篇:儒卓力和英飞凌达成亚洲市场分销协议

下一篇:让FPGA替代GPU,你会有怎样的顾虑?

推荐阅读最新更新时间:2024-05-03 02:02

人工智能算法(卷2)-受大自然启发的算法

人工智能算法(卷2)-受大自然启发的算法 嵌入式网络那些事:LwIP协议深度剖析与实战演练

嵌入式网络那些事:LwIP协议深度剖析与实战演练

京公网安备 11010802033920号

京公网安备 11010802033920号