摘要:介绍了基于MIPS指令集的嵌入式处理器BCM1250的双向核、大容量片内缓存、多类型通信接口等主要特性,并对其应用方案、启动过程、操作系统选择等进行了探讨。

关键词:MIPS 嵌入式RTOS SMP

1983年,斯坦福大学的John L.Hennessy成功完成了第一个采用RISC理念瓣MIPS(Microprocessor without Interlocked Pipeline Stages)微处理器。次年,他在硅谷创立了MIPS公司。该公司本身不生产微处理器,只设计高性能工业级的32位和64位CPU的体系结构,并且向其他半导体公司提供使用其内核(IP)的授权,用于生产基于MIPS而又各具特色的微处理器。目前已经有50多家公司申请了授权,相继推出了一批个性鲜明的微处理器,如PMC-Sierra公司的RM7000系列、RM9000X2,NEC公司的VR55000、VR7700,而Broadcom公司开发的BCM1250一举夺得了当年度嵌入式处理器论坛的“最佳高效能嵌入式处理器”大奖。

1 BCM1250处理器

BCM1250是Broadcom公司开发的基于MIPS架构的双内核、高性能64位RISC微处理器,采用0.13μm CMOS工艺制造,860引脚BGA封装(42.5%26;#215;42.5mm),最高主频1GHz。芯片集成了两个名为“SB-1”的内核(CPU0和CPU1)。SB-1内核不仅实现了标准的MIPS64指令集架构,而且增加了MIPS-3D和MIPS-MDMX专用扩展指令。在1GHz时,两个内核具有4000MIPS或10Mpps的处理能力。

BCM1250是一种紧耦合共享内存对称式多处理器(SMP)。SMP系统定义为通过一个公共高速总线,将多个相同的处理器与内存和I/O设备等一系列外围设备连接起来的系统。“对称”意味着每个处理器在访问共享内存和外围设备时,访问机制相同。所谓“紧耦合”是指各内核个体之间距离很近,并通过一个通用高速总线实现物理互连。这些内核通过公共高速总线共享一个全局内存模块(即共享内存)以及诸多外围设备。

图1

图1是BCM1250的内部结构框图。主要特点如下。

1.1 高性能双内核和大容量缓存

(1)两个64位MIPS内核SB-1。每个内核能够在一个时钟周期发射4条指令。每个内核包含32KB 4路组关联指令缓存和32KB 4路组关联数据缓存,64位入口的全关联TLB(Translation Lookaside Buffer)。

(2)两个SB-1共享4路组关联二级高速缓存(L2 Cache),每路128KB,共512KB。与其它系统不同的是,内核与I/O DMA主设备共享这片缓存,就像缓存处于内核和SDRAM(内存)之间,所有对内存的访问都在二级缓存中检验。并且,每路Cache可以单独设置为存储器模式,作为存储器使用,而且速度不变。

(3)面向网络分组处理优化的片内公共高速总线Zbbus,256位(1个缓存线长cache line)数据宽度,速率是CPU主频的一半,将两个CPU、L2 Cache、SDRAM控制器和I/O桥等连接起来。总线使用MESI协议以保证两个CPU、L2 Cache、内存和外部设备的数据的一致性。

(4)两个内核之间可以通过指令(ll、lld、sc和scd指令)和中断等方式进行通信。每个内核含有一个邮箱(mailbox)寄存器。当一个内核通过Zbbus总线访问另一个内核的邮箱寄存器时,产生中断。

1.2 外围控制模块和多类型通信接口

(1)DDR SDRAM控制器包括两个通道,每个通道64位数据宽度,另加8位ECC数据,支持两条JEDEC标准的133MHz DDR DIMM。每个通道的带宽高达16Gbps。如果采用DRAM芯片,辅以严格的走线控制,速度可达到200MHz,带宽高达50Gbps。ECC单元能够检测2位错误,纠正1位错误。

(2)一个遵循PCI2.2标准的PCI接口,32位数据宽度,最高速率66MHz。内部PCI仲裁器支持4个外部设备。

图2

(3)一个遵循HyperTransport 1.03标准的HyperTransport接口(简称HT接口)。HyperTransport的性能比PCI总线高,是PCI总线的升级换代产品,由AMD公司在1999年的微处理器论坛上首先提出。HT设备采用标准的PCI配置方法。发送和接收的数据宽度都是8位。HT总线的参考时钟是100MHz,但是发送数据的速率可以是参考时钟的6位,而且时钟的上下边沿都能触发。

(4)三个遵循IEEE802.3标准的MAC控制器,支持10Mbps、100Mbps、1Gbps以太网接口,可以运行在全双工或者半双工模式,可以设置收发数据包的最大长度和最短长度,甚至支持16K~1B的大包。MAC控制器支持VLAN——一个便于组建虚拟局域网的标志。不仅如此,控制器还能够识别以太网包的类型、Ipv4包的校验和TCP/UDP包的校验和,并且能够根据数据包的目的地址进行过滤,选择是否接收广播包。控制器包含32位RMON统计寄存器,可以统计接收和发送的数据量、失败次数、CRC出错次数等。所以,有的资料将BCM1250称作网络处理器,因为其MAC的功能比普通MAC强大。

(5)除了标准的以太网模式,网络接口还能够配置成Packet FIFO模式。在此模式下,MAC控制器引脚复用作Packet FIFO,设置为8位或者16位数据通道,速率可达208MHz。

(6)两个串口既可以工作于同步模式,也可以工作于异步模式的最高速率为5Mbps。两个串口的模式选择分别由AD[12]和AD[14]引脚在启动时的电平决定。当然,CPU可以通过系统配置寄存器改变串口模式。串口的同步模式分为两种子模式:HDLC和Transparent。

(7)设备控制器向外引出通用总线,用于连接外围设备。它有8个片选信号CS[0:7],其中CS[0]专用于连接bootrom,CS[7]用于连接PCMCIA设备。每个片选空间的最大容量为256MB,可以独立设置时序、数据宽度、地址空间等参数。上电时,CS[0]映射到4MB物理空间,从0x1FC00000~0x1FFFFFFF。0x1FC00000是MIPS处理器的启动中断入口地址。

(8)一个遵循PCMCAI 2.1标准的PCMCIA接口,支持外接PCMCIA存储卡的热插拔,能够根据卡的插入和拔出相应地上下电。PCMCIA接口、中断、通用输入输出口三者的引脚是复用的,设计师应根据实际需要决定取舍。PCMCIA接口需要消息10个GPIO引脚。

(9)16个GPIO引脚既可以配置成中断引脚,也可以配置成普通数据输入输出引脚或者PCMCIA接口。

(10)两个SMBus接口,遵循SMBus(系统管理总线)标准1.1,与I2C总线兼容。最高工作频率为400kHz。系统可以选择从SMBus 0接口的EEPROM启动。启动方式由引脚AD[17:18]在上电时的电平决定。

(11)多个DMA控制器。每个同步串口含有一个发送和接收DMA通道,每个网口有两个支持QoS的发磅和接收DMA通道。还有4个专用于存储器和其它设备(例如PCI,Flash)之间搬运数据的DMA。

(12)I/O桥0和I/O桥1将外围模块和内部高速总线Zbbus隔离开来。

(13)两个看门狗(Watchdog),4个通用定时器,4个40bit性能计数寄存器。定时器的最小单位为1μs。

(14)一个符合IEEE1149.1标准的JTAG接口,方便了硬件调试和测试。

1.3 其它

(1)低功耗,运行在800MHz主频下的功耗为8~10W。

(2)芯片既可以工作于Big Endian模式,也可以工作于Little Endian模式,取决上电时引脚AD[22]的电平。

(3)为减少抖动,外部100MHz时钟以差分信号方式输入到芯片,经过内部的PLL倍频或分频,分别输送给内核、存储器、Zbbus、HT接口、定时器、波特率发生器等单元。

(4)内核电压和HT接口电压为1.2V,DDR SDRAM接口电压为2.5V,其它模块接口电压为3.3V。

2 应用与实现的探讨

2.1 典型应用

图2是BCM1250的典型应用框图,配合不同的外围器件,可以构成多种应用方式。PMC插槽可以扩展多种应用,例如网卡、DSP卡、IPSec卡等,DDR SDRAM既可以是内存条,也可以是焊在电路板上的SDRAM芯片。串行设备可以是EEPROM或者实时时钟芯片等,其它设备可以是USB控制器等。本系统的特点是可靠性高、扩展性强、通信接口多、占用空间少,适合于大型路由器、VoIP网关、交换机、无线基站等高端场合。

2.2 启动

因为是双核CPU,所以在实现过程中应特别注意合理安排系统的启动顺序。上电后,上电复位信号COLDRES_L必须保持为低电平直到电源和参考时钟稳定在工作范围之内;然后BCM1250读取配置PLL倍频系数的引脚电平,从AD引脚读取系统其它配置信息,例如,是否选用PCI内部仲裁器,串口是否工作在同步模式等。启动时,芯片根据AD[17:18]信号电平,选择从挂在通用总线CS0上的Flash,或者从SMBus 0口的串行EEPROM读取启动代码。

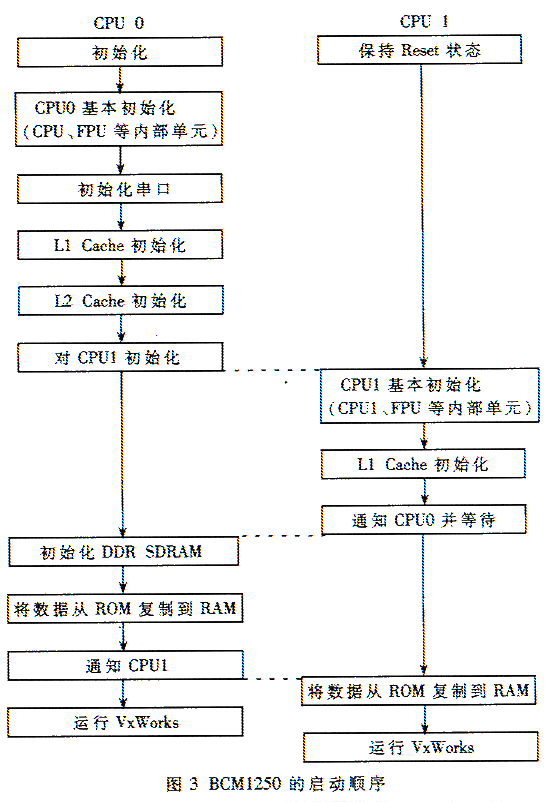

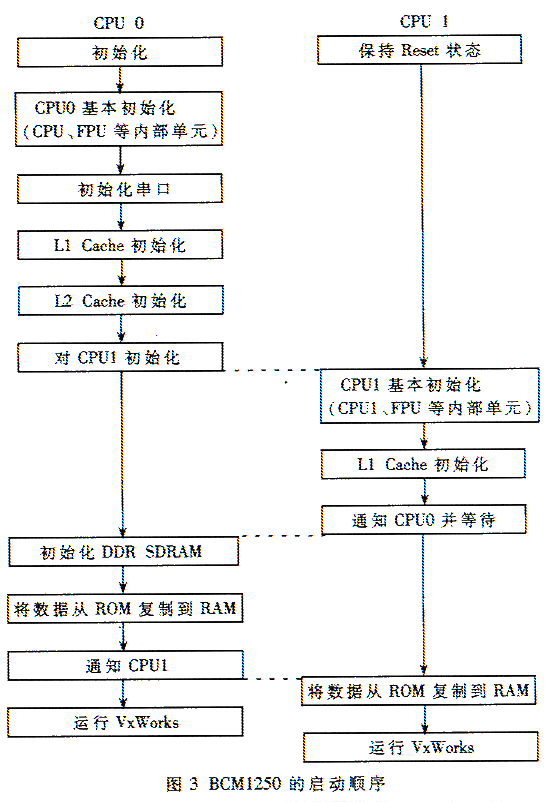

图3以Windriver公司的VxWorks嵌入式实时操作系统为例,说明了启动顺序。其它操作系统的启动顺序类似。CPU0首先初始化,CPU1保持启动状态,等待CPU0完成基本的内核初始化、串口初始化、L1 Cache和L2 Cache的初始化;然后CPU0对CPU1初始化,包括内核的基本初始化和CPU1内部的L1 Cache初始化;接着,CPU1再次等待,CPU0对DDR SDRAM进行初始化,再将操作系统等数据从ROM复制到SDRAM,通知CPU1,然后启动操作系统;CPU1收到通知后,也将数据从ROM复制到SDRAM,运行操作系统的复本。较早地初始化串口,是为了便于通过计算机屏幕及监测系统的启动状况,判断故障所在。

2.3 选择操作系统的考虑

因为BCM1250是一种SMP系统,所以选择操作系统时应考虑SMP系统的特点,充分发挥BCM1250的双内核特性。与单核处理器相比,SMP系统的优势是显然的:

(1)在完成一组任务时,两个CPU并行运行比一个CPU单独运行的速度快得多。

(2)即使有一个CPU出现了致命故障,另一个CPU也能无缝地接管它的工作,降低系统的停工时间。

SMP系统与分布式多处理器的区别在于:在一个分布式多处理器系统中,处理单元个体通常以单独节点的形式存在,每个这样的节点中的处理器类型可以不同,并且各自配备内存和I/O设备。每个处理器可以运行自己的操作系统,只通过一种互连方式(例如以太网),利用消息或旗语来与其它处理器同步。而紧耦合共享内存SMP系统则不同。在SMP系统中,所有的处理器都运行操作系统的同一个副本,该操作系统可协调每个相似的CPU上同时发生的活动。由于紧耦合CPU所访问的是一个公共内存区,所以它们必须通过一种基于低延时共享内存的通信机制实现相互之间的同步。这对操作系统提出了要求。

其次,如果操作系统选择得当,能使硬件中确切的处理单元数对应用程序员透明。于是应用软件就能不进行任何针对SMP的修改而运行。

再次,BCM1250同时有两个任务在运行,两个CPU都可以处理中断,所以操作系统还必须具备“旋转锁”等机制,保证任务的合理调度和中断的及时处理。

业界流行的MontaVistaLinux专业版、VxWorks等RTOS均支持SMP系统。当然,用户也可以将单处理器RTOS扩展为支持SMP的系统。

虽然BCM1250比单内核处理器在结构上只多了一个内核,但是在启动顺序、任务调度、中断管理等方面却有着较大的差别,相应地对RTOS提出了较高的要求。BCM1250主要用于高端设备,在国内的开发应用还不普及。

2.2 启动

因为是双核CPU,所以在实现过程中应特别注意合理安排系统的启动顺序。上电后,上电复位信号COLDRES_L必须保持为低电平直到电源和参考时钟稳定在工作范围之内;然后BCM1250读取配置PLL倍频系数的引脚电平,从AD引脚读取系统其它配置信息,例如,是否选用PCI内部仲裁器,串口是否工作在同步模式等。启动时,芯片根据AD[17:18]信号电平,选择从挂在通用总线CS0上的Flash,或者从SMBus 0口的串行EEPROM读取启动代码。

图3以Windriver公司的VxWorks嵌入式实时操作系统为例,说明了启动顺序。其它操作系统的启动顺序类似。CPU0首先初始化,CPU1保持启动状态,等待CPU0完成基本的内核初始化、串口初始化、L1 Cache和L2 Cache的初始化;然后CPU0对CPU1初始化,包括内核的基本初始化和CPU1内部的L1 Cache初始化;接着,CPU1再次等待,CPU0对DDR SDRAM进行初始化,再将操作系统等数据从ROM复制到SDRAM,通知CPU1,然后启动操作系统;CPU1收到通知后,也将数据从ROM复制到SDRAM,运行操作系统的复本。较早地初始化串口,是为了便于通过计算机屏幕及监测系统的启动状况,判断故障所在。

2.3 选择操作系统的考虑

因为BCM1250是一种SMP系统,所以选择操作系统时应考虑SMP系统的特点,充分发挥BCM1250的双内核特性。与单核处理器相比,SMP系统的优势是显然的:

(1)在完成一组任务时,两个CPU并行运行比一个CPU单独运行的速度快得多。

(2)即使有一个CPU出现了致命故障,另一个CPU也能无缝地接管它的工作,降低系统的停工时间。

SMP系统与分布式多处理器的区别在于:在一个分布式多处理器系统中,处理单元个体通常以单独节点的形式存在,每个这样的节点中的处理器类型可以不同,并且各自配备内存和I/O设备。每个处理器可以运行自己的操作系统,只通过一种互连方式(例如以太网),利用消息或旗语来与其它处理器同步。而紧耦合共享内存SMP系统则不同。在SMP系统中,所有的处理器都运行操作系统的同一个副本,该操作系统可协调每个相似的CPU上同时发生的活动。由于紧耦合CPU所访问的是一个公共内存区,所以它们必须通过一种基于低延时共享内存的通信机制实现相互之间的同步。这对操作系统提出了要求。

其次,如果操作系统选择得当,能使硬件中确切的处理单元数对应用程序员透明。于是应用软件就能不进行任何针对SMP的修改而运行。

再次,BCM1250同时有两个任务在运行,两个CPU都可以处理中断,所以操作系统还必须具备“旋转锁”等机制,保证任务的合理调度和中断的及时处理。

业界流行的MontaVistaLinux专业版、VxWorks等RTOS均支持SMP系统。当然,用户也可以将单处理器RTOS扩展为支持SMP的系统。

虽然BCM1250比单内核处理器在结构上只多了一个内核,但是在启动顺序、任务调度、中断管理等方面却有着较大的差别,相应地对RTOS提出了较高的要求。BCM1250主要用于高端设备,在国内的开发应用还不普及。

引用地址:双内核嵌入式处理器BCM1250及其应用

2.2 启动

因为是双核CPU,所以在实现过程中应特别注意合理安排系统的启动顺序。上电后,上电复位信号COLDRES_L必须保持为低电平直到电源和参考时钟稳定在工作范围之内;然后BCM1250读取配置PLL倍频系数的引脚电平,从AD引脚读取系统其它配置信息,例如,是否选用PCI内部仲裁器,串口是否工作在同步模式等。启动时,芯片根据AD[17:18]信号电平,选择从挂在通用总线CS0上的Flash,或者从SMBus 0口的串行EEPROM读取启动代码。

图3以Windriver公司的VxWorks嵌入式实时操作系统为例,说明了启动顺序。其它操作系统的启动顺序类似。CPU0首先初始化,CPU1保持启动状态,等待CPU0完成基本的内核初始化、串口初始化、L1 Cache和L2 Cache的初始化;然后CPU0对CPU1初始化,包括内核的基本初始化和CPU1内部的L1 Cache初始化;接着,CPU1再次等待,CPU0对DDR SDRAM进行初始化,再将操作系统等数据从ROM复制到SDRAM,通知CPU1,然后启动操作系统;CPU1收到通知后,也将数据从ROM复制到SDRAM,运行操作系统的复本。较早地初始化串口,是为了便于通过计算机屏幕及监测系统的启动状况,判断故障所在。

2.3 选择操作系统的考虑

因为BCM1250是一种SMP系统,所以选择操作系统时应考虑SMP系统的特点,充分发挥BCM1250的双内核特性。与单核处理器相比,SMP系统的优势是显然的:

(1)在完成一组任务时,两个CPU并行运行比一个CPU单独运行的速度快得多。

(2)即使有一个CPU出现了致命故障,另一个CPU也能无缝地接管它的工作,降低系统的停工时间。

SMP系统与分布式多处理器的区别在于:在一个分布式多处理器系统中,处理单元个体通常以单独节点的形式存在,每个这样的节点中的处理器类型可以不同,并且各自配备内存和I/O设备。每个处理器可以运行自己的操作系统,只通过一种互连方式(例如以太网),利用消息或旗语来与其它处理器同步。而紧耦合共享内存SMP系统则不同。在SMP系统中,所有的处理器都运行操作系统的同一个副本,该操作系统可协调每个相似的CPU上同时发生的活动。由于紧耦合CPU所访问的是一个公共内存区,所以它们必须通过一种基于低延时共享内存的通信机制实现相互之间的同步。这对操作系统提出了要求。

其次,如果操作系统选择得当,能使硬件中确切的处理单元数对应用程序员透明。于是应用软件就能不进行任何针对SMP的修改而运行。

再次,BCM1250同时有两个任务在运行,两个CPU都可以处理中断,所以操作系统还必须具备“旋转锁”等机制,保证任务的合理调度和中断的及时处理。

业界流行的MontaVistaLinux专业版、VxWorks等RTOS均支持SMP系统。当然,用户也可以将单处理器RTOS扩展为支持SMP的系统。

虽然BCM1250比单内核处理器在结构上只多了一个内核,但是在启动顺序、任务调度、中断管理等方面却有着较大的差别,相应地对RTOS提出了较高的要求。BCM1250主要用于高端设备,在国内的开发应用还不普及。

2.2 启动

因为是双核CPU,所以在实现过程中应特别注意合理安排系统的启动顺序。上电后,上电复位信号COLDRES_L必须保持为低电平直到电源和参考时钟稳定在工作范围之内;然后BCM1250读取配置PLL倍频系数的引脚电平,从AD引脚读取系统其它配置信息,例如,是否选用PCI内部仲裁器,串口是否工作在同步模式等。启动时,芯片根据AD[17:18]信号电平,选择从挂在通用总线CS0上的Flash,或者从SMBus 0口的串行EEPROM读取启动代码。

图3以Windriver公司的VxWorks嵌入式实时操作系统为例,说明了启动顺序。其它操作系统的启动顺序类似。CPU0首先初始化,CPU1保持启动状态,等待CPU0完成基本的内核初始化、串口初始化、L1 Cache和L2 Cache的初始化;然后CPU0对CPU1初始化,包括内核的基本初始化和CPU1内部的L1 Cache初始化;接着,CPU1再次等待,CPU0对DDR SDRAM进行初始化,再将操作系统等数据从ROM复制到SDRAM,通知CPU1,然后启动操作系统;CPU1收到通知后,也将数据从ROM复制到SDRAM,运行操作系统的复本。较早地初始化串口,是为了便于通过计算机屏幕及监测系统的启动状况,判断故障所在。

2.3 选择操作系统的考虑

因为BCM1250是一种SMP系统,所以选择操作系统时应考虑SMP系统的特点,充分发挥BCM1250的双内核特性。与单核处理器相比,SMP系统的优势是显然的:

(1)在完成一组任务时,两个CPU并行运行比一个CPU单独运行的速度快得多。

(2)即使有一个CPU出现了致命故障,另一个CPU也能无缝地接管它的工作,降低系统的停工时间。

SMP系统与分布式多处理器的区别在于:在一个分布式多处理器系统中,处理单元个体通常以单独节点的形式存在,每个这样的节点中的处理器类型可以不同,并且各自配备内存和I/O设备。每个处理器可以运行自己的操作系统,只通过一种互连方式(例如以太网),利用消息或旗语来与其它处理器同步。而紧耦合共享内存SMP系统则不同。在SMP系统中,所有的处理器都运行操作系统的同一个副本,该操作系统可协调每个相似的CPU上同时发生的活动。由于紧耦合CPU所访问的是一个公共内存区,所以它们必须通过一种基于低延时共享内存的通信机制实现相互之间的同步。这对操作系统提出了要求。

其次,如果操作系统选择得当,能使硬件中确切的处理单元数对应用程序员透明。于是应用软件就能不进行任何针对SMP的修改而运行。

再次,BCM1250同时有两个任务在运行,两个CPU都可以处理中断,所以操作系统还必须具备“旋转锁”等机制,保证任务的合理调度和中断的及时处理。

业界流行的MontaVistaLinux专业版、VxWorks等RTOS均支持SMP系统。当然,用户也可以将单处理器RTOS扩展为支持SMP的系统。

虽然BCM1250比单内核处理器在结构上只多了一个内核,但是在启动顺序、任务调度、中断管理等方面却有着较大的差别,相应地对RTOS提出了较高的要求。BCM1250主要用于高端设备,在国内的开发应用还不普及。

上一篇:MCU应用系统与Internet连接的一种新技术

下一篇:用GNU工具开发基于ARM的嵌入式系统

- 热门资源推荐

- 热门放大器推荐

Verilog HDL数字集成电路设计原理与应用

Verilog HDL数字集成电路设计原理与应用 LT1997IDF-2#TRPBF

LT1997IDF-2#TRPBF

京公网安备 11010802033920号

京公网安备 11010802033920号