摘要:以交通十字路口实时DSP图像采集系统为例,说明了基于PCI总线的DSP图像采集系统的优点,并详细阐明了系统的硬件结构和基于VxWorks操作平台的软件实现,最后介绍了系统实现的效果。

关键词:PCI总线 DSP VxWorks操作系统 图像采集系统

本文从实时性和大容量两方面介绍了在通用计算机上加入DSP加速卡实现的图像采集系统。利用DSP芯片的高速处理特性完成大部分的图像处理工作,上位机只完成辅助操作和存储系统。这种方法发挥了DSP的高速性能又具有相当大的灵活性,而且开发工具比较完善。

实时性要求足够的传输速度,PCI总线速度最高可达528MB/s(66MHz、64位)。这是其他总线无法比拟的速度,如ISA总线速度只有5MB/s。另外,系统中DSP的可扩展存储空间高达1GB。这完全可以满足一般图像处理系统的需要。

1 基于PCI总线的DSP图像采集系统

本系统主要用于路口违章车辆抓拍,包括闯红灯抓拍、超速行驶抓拍等。通过摄像头对车流进行监测,当有车辆在红灯期间越过停止线或在限速地段超速行驶,系统拍下车辆的行为并把数据传送到DSP进行处理,然后经PCI总线把处理后的数据上传到上位机。当然这套系统也可用于其他的监控系统,如楼宇监控等,其硬件系统基本一致,只是软件功能有所区别。

本系统采用TI公司C6000系列DSP中的TMS320C6211作为系统的CPU。图像数据通过摄像机采集并输出模拟图像信号。这些信号经视频解码芯片转换为数字信号;再经FIFO输入DSP进行图像的增强、分割、特征提取和数据压缩等;然后输出信号经PCI解码芯片转换为符合PCI总线规范的标准信号,通过PCI总线接口传到上位机。系统的控制逻辑由EPLD(Erasable Programmable Logic Device)控制器实现。系统结构图如图1。

(1)视频解码芯片

系统中采集的图像信号采用Philips公司的SAA7111A完成A/D转换。SAA7111A允许四路模拟视频输入,具有两个模拟处理通道,支持四路CVBS模拟信号或二路Y/C模拟信号或二路CVBS信号和一路Y/C信号。SAA7111A对摄像头输入的标准PAL格式的模拟图像信号进行A/D转换,然后输出符合CCIR601格式的4:2:2的16位YUV数据到FIFO。其中亮度信号Y为8位、色度信号Cr和Cb合为8位数据。FIFO采用IDT公司的IDT72V215LB芯片,FIFO的深度为512%26;#215;18bit,支持STANDARD(标准)和FWFT(First Word Fall-Through,首字直接通过)两种工作模式。按照CCIR601格式,YUV图像分辨率为720%26;#215;576象素,当按行输出时,SAA7111A输出数据流大小为:720%26;#215;16=1440bit。因为DSP通过32位的SBSRAM接口与FIFO通信,故YUV数据写入FIFO时需要在FIFO之间实现乒乓切换。这时一行720%26;#215;16bit的数据在两片FIFO中存储变为360%26;#215;32bit。两片FIFO可以满足上述要求。FIFO的初始化及时序由EPLD实现。

本系统采用TI公司C6000系列DSP中的TMS320C6211作为系统的CPU。图像数据通过摄像机采集并输出模拟图像信号。这些信号经视频解码芯片转换为数字信号;再经FIFO输入DSP进行图像的增强、分割、特征提取和数据压缩等;然后输出信号经PCI解码芯片转换为符合PCI总线规范的标准信号,通过PCI总线接口传到上位机。系统的控制逻辑由EPLD(Erasable Programmable Logic Device)控制器实现。系统结构图如图1。

(1)视频解码芯片

系统中采集的图像信号采用Philips公司的SAA7111A完成A/D转换。SAA7111A允许四路模拟视频输入,具有两个模拟处理通道,支持四路CVBS模拟信号或二路Y/C模拟信号或二路CVBS信号和一路Y/C信号。SAA7111A对摄像头输入的标准PAL格式的模拟图像信号进行A/D转换,然后输出符合CCIR601格式的4:2:2的16位YUV数据到FIFO。其中亮度信号Y为8位、色度信号Cr和Cb合为8位数据。FIFO采用IDT公司的IDT72V215LB芯片,FIFO的深度为512%26;#215;18bit,支持STANDARD(标准)和FWFT(First Word Fall-Through,首字直接通过)两种工作模式。按照CCIR601格式,YUV图像分辨率为720%26;#215;576象素,当按行输出时,SAA7111A输出数据流大小为:720%26;#215;16=1440bit。因为DSP通过32位的SBSRAM接口与FIFO通信,故YUV数据写入FIFO时需要在FIFO之间实现乒乓切换。这时一行720%26;#215;16bit的数据在两片FIFO中存储变为360%26;#215;32bit。两片FIFO可以满足上述要求。FIFO的初始化及时序由EPLD实现。

(2)DSP图像处理模块

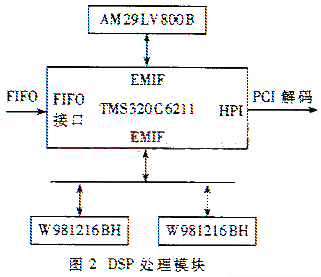

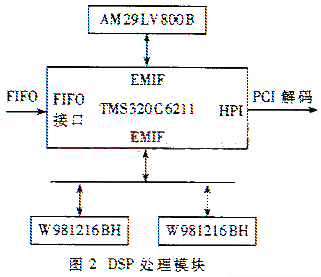

TMS320C6211是TI公司发布的面向视频处理领域的新款高速数字处理芯片,适用于移动通信基站、图像监控、雷达系统等对速度要求高和高度智能化的应用领域。存储空间分两部分:运行过程的临时数据存在Winbond公司的两片128Mbit的W981216BH中;系统程序则固化在FLASH存储器中,该存储器选用AMD公司生产的8Mbit的AM29LV800B。Flash存储器具有在线重写入功能。这对系统启动程序的修改和升级都带来了很大的方便。DSP处理模块结构如图2所示。图2中的HPI(Host Port Interface)为主机口;EMIF(External Memory Interface)为外部存储器接口,兼容同步/异步传输方式。

TMS320C6211 DSP的高速性能主要体现在以下方面:①TMS320C6211的存储空间最大可扩展到1GB,完全可以满足各种图像处理系统所需的内存空间,而且其最高时钟可达200MHz,峰值性能可达1600MIPS(百万条指令/秒)、2400MOPS(百万次操作/秒)。②并行处理结构。TMS320C6211芯片内有8个并行处理单元,分为相同的两组,并行结构大大提高芯片的性能。③芯片体系采用VelociTI结构。VelociTI是一种高性能的甚长指令字(VLIW)结构,单指令字字长为32bit,8个指令组成一个指令包,总字长为256bit。即每秒钟可以执行8条指令。VelociTI结构大大提高了DSP芯片的性能。④采用流水线操作实现高速度、高效率。TMS320C6211只有在流水线充分发挥作用的情况下,才能达到最高的峰值性能。与其他系列DSP相比,优势在于简化了流水线的控制以消除流水线互锁,并增加流水线的深度来消除传统流水线的取指、数据访问和乘法操作上的瓶颈。

本系统DSP主要完成从FIFO读出数据的处理以及压缩等。数据处理由自行编写的算法实现,数据压缩算法采用JPEG(Joint Photographic Expert Group)标准。当摄像头采集速度为每秒25帧图像时,它留给DSP处理的时间最多为每帧40ms。如果考虑系统有一定的延时以及处理后图像的存储时间,那么DSP处理一幅图像时间不能超过30ms。按照C6211的处理速度,在30ms内可以处理48M(0.03%26;#215;1600MIPS)条指令。DSP读出FIFO中的行数据并存入SDRAM,一帧图像有576行,在最后一行时会收到系统的帧中断,这时SDRAM中的图像数据总共有1440%26;#215;576=810KB。让C6211用36M条指令周期的时间处理810KB的数据显然绰绰有余。粗略的计算过程如下:

系统采用快速DCT(离散余弦变换),每8%26;#215;8矩阵需要11次乘法、29次加法,因此一帧图像的FDCT,共需要(11+29)%26;#215;720%26;#215;576%26;#215;2/64=518400个指令周期;对于量化模块,每8%26;#215;8矩阵需要64个量化指令周期,一帧需要64%26;#215;720%26;#215;576%26;#215;2/64=829440个指令周期;对于编码部分,假设编码后非0元素占25%,对每8%26;#215;8矩阵进行Zig-Zag扫描、编码估计需要120个指令周期,则共需120%26;#215;720%26;#215;576%26;#215;2/64=1555200个指令周期。按以上计算,在系统中进行JPEG编码大约需要2903040个指令周期,耗时19.3536ms(TMS320C6211工作在150MHz时)。可以看出,实际需要的指令远小于36M条,而时间也远小于30ms,DSP完全可以实时处理从FIFO传过来的数据。

(3)PCI总线模块

PCI总线规范吸引人的地方不仅是其高速度,更在于

(2)DSP图像处理模块

TMS320C6211是TI公司发布的面向视频处理领域的新款高速数字处理芯片,适用于移动通信基站、图像监控、雷达系统等对速度要求高和高度智能化的应用领域。存储空间分两部分:运行过程的临时数据存在Winbond公司的两片128Mbit的W981216BH中;系统程序则固化在FLASH存储器中,该存储器选用AMD公司生产的8Mbit的AM29LV800B。Flash存储器具有在线重写入功能。这对系统启动程序的修改和升级都带来了很大的方便。DSP处理模块结构如图2所示。图2中的HPI(Host Port Interface)为主机口;EMIF(External Memory Interface)为外部存储器接口,兼容同步/异步传输方式。

TMS320C6211 DSP的高速性能主要体现在以下方面:①TMS320C6211的存储空间最大可扩展到1GB,完全可以满足各种图像处理系统所需的内存空间,而且其最高时钟可达200MHz,峰值性能可达1600MIPS(百万条指令/秒)、2400MOPS(百万次操作/秒)。②并行处理结构。TMS320C6211芯片内有8个并行处理单元,分为相同的两组,并行结构大大提高芯片的性能。③芯片体系采用VelociTI结构。VelociTI是一种高性能的甚长指令字(VLIW)结构,单指令字字长为32bit,8个指令组成一个指令包,总字长为256bit。即每秒钟可以执行8条指令。VelociTI结构大大提高了DSP芯片的性能。④采用流水线操作实现高速度、高效率。TMS320C6211只有在流水线充分发挥作用的情况下,才能达到最高的峰值性能。与其他系列DSP相比,优势在于简化了流水线的控制以消除流水线互锁,并增加流水线的深度来消除传统流水线的取指、数据访问和乘法操作上的瓶颈。

本系统DSP主要完成从FIFO读出数据的处理以及压缩等。数据处理由自行编写的算法实现,数据压缩算法采用JPEG(Joint Photographic Expert Group)标准。当摄像头采集速度为每秒25帧图像时,它留给DSP处理的时间最多为每帧40ms。如果考虑系统有一定的延时以及处理后图像的存储时间,那么DSP处理一幅图像时间不能超过30ms。按照C6211的处理速度,在30ms内可以处理48M(0.03%26;#215;1600MIPS)条指令。DSP读出FIFO中的行数据并存入SDRAM,一帧图像有576行,在最后一行时会收到系统的帧中断,这时SDRAM中的图像数据总共有1440%26;#215;576=810KB。让C6211用36M条指令周期的时间处理810KB的数据显然绰绰有余。粗略的计算过程如下:

系统采用快速DCT(离散余弦变换),每8%26;#215;8矩阵需要11次乘法、29次加法,因此一帧图像的FDCT,共需要(11+29)%26;#215;720%26;#215;576%26;#215;2/64=518400个指令周期;对于量化模块,每8%26;#215;8矩阵需要64个量化指令周期,一帧需要64%26;#215;720%26;#215;576%26;#215;2/64=829440个指令周期;对于编码部分,假设编码后非0元素占25%,对每8%26;#215;8矩阵进行Zig-Zag扫描、编码估计需要120个指令周期,则共需120%26;#215;720%26;#215;576%26;#215;2/64=1555200个指令周期。按以上计算,在系统中进行JPEG编码大约需要2903040个指令周期,耗时19.3536ms(TMS320C6211工作在150MHz时)。可以看出,实际需要的指令远小于36M条,而时间也远小于30ms,DSP完全可以实时处理从FIFO传过来的数据。

(3)PCI总线模块

PCI总线规范吸引人的地方不仅是其高速度,更在于

它适应了现代I/O设备对系统的要求,对PCI扩展卡及器件能进行全自动配置,并且只需很少的接口逻辑就可以实现并支持其他总线系统。

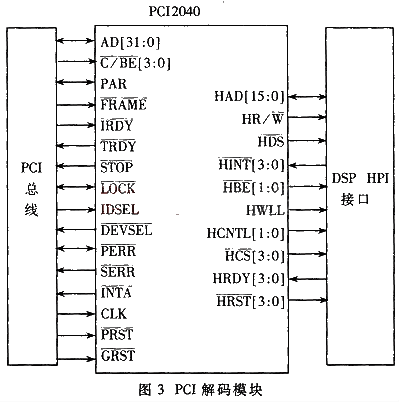

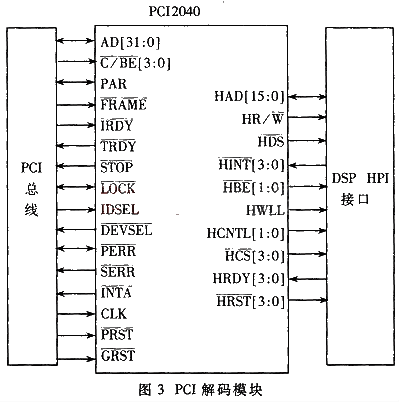

TMS320C6211的HPI口不支持PCI总线的无缝接口。本系统采用TI公司的PCI2040实现DSP的HPI与PCI总线的连接。DSP处理后的数据经HPI口输出到PCI2040进行解码,然后输出到PCI总线上。其逻辑结构如图3所示。

PCI2040是TI公司设计的专门用来完成C5000系列和C6000系列DSP与PCI总线进行接口的专用芯片。PCI2040符合PCI局部总线2.2规范,能够方便地实现PCI总线与TMS320C54X或TMS320C6X DSP的HPI接口的无缝连接。PCI2040可以兼容3.3V和5V,以适应不同的PCI总线电压。PCI2040与C6211之间不需要信号的电平转换,也不需要额外的控制逻辑电路,接口电路十分简单。

在本系统中,PCI2040上存在两种电压:5V和3.3V。其中3.3V是HPI口电压,5V是PCI总线电压。PCI2040启动时需要对其PCI总线寄存器和HPI寄存器参数进行预加载。系统中PCI解码模块包括一块配置ROM——AT24C08A,属于EEPROM型ROM,便于对配置参数修改和升级。当系统启动时,存储在AT24C08A的数据下载到PCI2040的寄存器中并进行配置。

图3中HINT[3:0]、HCS[3:0]、HRDY[3:0]、HRST[3:0]分别与四片DSP中的相应信号相连。即PCI2040可以同时与四片DSP接口。

2 系统的软件设计

本软件系统包括两部分,即底层软件和系统软件。

底层软件主要是DSP图像处理算法以及启动等运行程序。这些程序主要在CCS环境下由C语言编写并进行汇编优化。CCS即Code Composer Studio,是TI公司发布的DSP软件运行环境。

在系统软件方面,基于PCI总线的图像处理系统面临的难点颇多,其中难度最大的是PCI驱动问题。当然这对于不同的系统软件可能难度各异。若在Windows操作系统下,可以充分利用Windows的窗口特性:一方面,因为Windows技术成熟,软件编写相对比较简单;另一方面,在Windows平台下,PCI驱动无需开发,可以直接利用Windows的PCI驱动程序实现图像卡的驱动。但是Windows操作系统比较庞大,而且无法依照系统的需要进行自由裁减,不适合做成嵌入式系统。这里主要阐述在VxWorks操作系统下的软件设计方法。

相对于Windows操作系统,VxWorks的优点表现在:①VxWorks系统具有较好的可裁减性,可裁剪的组件超过80个,用户可根据自己系统的功能目标通过交叉开发环境方便地配置;②VxWorks支持应用程序的动态链接和动态下载,开发者省去了每次调试都将应用程序与操作系统内核进行链接和下载的步骤,缩短了编辑/调试周期;③VxWorks具有较好的兼容性,它是最早兼容POSIX1003.1b标准的嵌入式实时操作系统之一;④VxWorks具有很高的可靠性和稳定性;⑤VxWorks具有很好的实时性,实时性的强弱以完成规定功能和做出响应时间的长短来衡量。VxWorks的多任务机制对任务的控制采用了优先级抢占(Preemptive Priority Scheduling)和轮转调度(Round-Robin Scheduling)机制。这充分保证了可靠的实时性,使同样的硬件配置能满足更强的实时性要求,为应用的开发留下更大的余地。

为阐明如何在VxWorks操作系统下实现PCI总线的驱动,还需了解PCI设备的配置空间。PCI设备有三种物理存储空间:配置空间、存储器空间和I/O空间。配置空间是长度为256字节的一段连续空间,空间的定义如图4?眼1?演。在配置空间中只读空间有设备标识、供应商代码、修改版本、分类代码以及头标类型。其中供应商代码用来标识设备供应商的代码;设备标识用来标识某一特殊的设备;修改版本标识设备的版本号;分类代码用来标识设备的种类;而头标类型用来标识头类型以及是否为多功能设备。除供应商代码之外,其他字段的值由供应商分配。

基地址寄存器最重要的功能是分配PCI设备的系统地址空间。在基地址寄存器中bit0(最低位)用来标识存储器空间还是I/O地址空间,基地址寄存器映射到存储器空间时bit0为“0”,映射到I/O地址空间时bit0为“1”。

它适应了现代I/O设备对系统的要求,对PCI扩展卡及器件能进行全自动配置,并且只需很少的接口逻辑就可以实现并支持其他总线系统。

TMS320C6211的HPI口不支持PCI总线的无缝接口。本系统采用TI公司的PCI2040实现DSP的HPI与PCI总线的连接。DSP处理后的数据经HPI口输出到PCI2040进行解码,然后输出到PCI总线上。其逻辑结构如图3所示。

PCI2040是TI公司设计的专门用来完成C5000系列和C6000系列DSP与PCI总线进行接口的专用芯片。PCI2040符合PCI局部总线2.2规范,能够方便地实现PCI总线与TMS320C54X或TMS320C6X DSP的HPI接口的无缝连接。PCI2040可以兼容3.3V和5V,以适应不同的PCI总线电压。PCI2040与C6211之间不需要信号的电平转换,也不需要额外的控制逻辑电路,接口电路十分简单。

在本系统中,PCI2040上存在两种电压:5V和3.3V。其中3.3V是HPI口电压,5V是PCI总线电压。PCI2040启动时需要对其PCI总线寄存器和HPI寄存器参数进行预加载。系统中PCI解码模块包括一块配置ROM——AT24C08A,属于EEPROM型ROM,便于对配置参数修改和升级。当系统启动时,存储在AT24C08A的数据下载到PCI2040的寄存器中并进行配置。

图3中HINT[3:0]、HCS[3:0]、HRDY[3:0]、HRST[3:0]分别与四片DSP中的相应信号相连。即PCI2040可以同时与四片DSP接口。

2 系统的软件设计

本软件系统包括两部分,即底层软件和系统软件。

底层软件主要是DSP图像处理算法以及启动等运行程序。这些程序主要在CCS环境下由C语言编写并进行汇编优化。CCS即Code Composer Studio,是TI公司发布的DSP软件运行环境。

在系统软件方面,基于PCI总线的图像处理系统面临的难点颇多,其中难度最大的是PCI驱动问题。当然这对于不同的系统软件可能难度各异。若在Windows操作系统下,可以充分利用Windows的窗口特性:一方面,因为Windows技术成熟,软件编写相对比较简单;另一方面,在Windows平台下,PCI驱动无需开发,可以直接利用Windows的PCI驱动程序实现图像卡的驱动。但是Windows操作系统比较庞大,而且无法依照系统的需要进行自由裁减,不适合做成嵌入式系统。这里主要阐述在VxWorks操作系统下的软件设计方法。

相对于Windows操作系统,VxWorks的优点表现在:①VxWorks系统具有较好的可裁减性,可裁剪的组件超过80个,用户可根据自己系统的功能目标通过交叉开发环境方便地配置;②VxWorks支持应用程序的动态链接和动态下载,开发者省去了每次调试都将应用程序与操作系统内核进行链接和下载的步骤,缩短了编辑/调试周期;③VxWorks具有较好的兼容性,它是最早兼容POSIX1003.1b标准的嵌入式实时操作系统之一;④VxWorks具有很高的可靠性和稳定性;⑤VxWorks具有很好的实时性,实时性的强弱以完成规定功能和做出响应时间的长短来衡量。VxWorks的多任务机制对任务的控制采用了优先级抢占(Preemptive Priority Scheduling)和轮转调度(Round-Robin Scheduling)机制。这充分保证了可靠的实时性,使同样的硬件配置能满足更强的实时性要求,为应用的开发留下更大的余地。

为阐明如何在VxWorks操作系统下实现PCI总线的驱动,还需了解PCI设备的配置空间。PCI设备有三种物理存储空间:配置空间、存储器空间和I/O空间。配置空间是长度为256字节的一段连续空间,空间的定义如图4?眼1?演。在配置空间中只读空间有设备标识、供应商代码、修改版本、分类代码以及头标类型。其中供应商代码用来标识设备供应商的代码;设备标识用来标识某一特殊的设备;修改版本标识设备的版本号;分类代码用来标识设备的种类;而头标类型用来标识头类型以及是否为多功能设备。除供应商代码之外,其他字段的值由供应商分配。

基地址寄存器最重要的功能是分配PCI设备的系统地址空间。在基地址寄存器中bit0(最低位)用来标识存储器空间还是I/O地址空间,基地址寄存器映射到存储器空间时bit0为“0”,映射到I/O地址空间时bit0为“1”。

PCI设备的驱动过程主要包括下面几个步骤:

首先,PCI设备的查找。在嵌入式操作系统中一般提供相应的API函数查找。在VxWorks操作系统中通过函数pciFindDevice(PCI_VENDOR_ID,PCI_DEVICE,index, &pciBus, &pciDevice,&pciFunc_可以找到供应商代码为PCI_VENDOR_ID、设备标识为PCI_DEVICE的第n(index+1)个设备,并且返回总线号、设备号以及功能号,分别保存于&pciBus、&pciDevice、&pciFunc中。

其次,PCI设备的配置。通过操作系统提供的API函数访问PCI设备的配置空间,配置PCI设备基址寄存器的配置、中断配置、ROM基地址寄存器的配置等,这样可以得到PCI的存储器空间和I/O地址空间映射、设备的中断号等。在VxWorks操作系统中访问PCI设备配置空间的API函数有pciConfigOutLong、pciConfigInLong等,它们分别完成对PCI设备配置空间的读写操作。

然后,根据PCI设备的配置参数,对不同的设备编写初始化程序、中断服务程序以及对PCI设备存储空间的访问程序。

很显然,用VxWorks操作系统实现虽然有一定的难度,但是系统具有很大的灵活性,系统比较小、适应性强,并且可以在工业控制计算机上运行。

图像采集系统的关键在于如何对大容量的信息进行暂存、压缩和传输等问题进行处理。本系统很好地解决了这三个难题。在图像信息暂存方面充分利用了DSP存储空间的可扩展性,保证了系统可暂存的信息量足够大;信息压缩是DSP最擅长做的事情,可以在很短的时间内完成大量的信息压缩工作;PCI总线的引入保证了信息在足够的带宽下进行快速传输。采用嵌入式VxWorks操作系统实现使得系统具有良好的灵活性和适应性,并大大降低了系统的成本。

PCI设备的驱动过程主要包括下面几个步骤:

首先,PCI设备的查找。在嵌入式操作系统中一般提供相应的API函数查找。在VxWorks操作系统中通过函数pciFindDevice(PCI_VENDOR_ID,PCI_DEVICE,index, &pciBus, &pciDevice,&pciFunc_可以找到供应商代码为PCI_VENDOR_ID、设备标识为PCI_DEVICE的第n(index+1)个设备,并且返回总线号、设备号以及功能号,分别保存于&pciBus、&pciDevice、&pciFunc中。

其次,PCI设备的配置。通过操作系统提供的API函数访问PCI设备的配置空间,配置PCI设备基址寄存器的配置、中断配置、ROM基地址寄存器的配置等,这样可以得到PCI的存储器空间和I/O地址空间映射、设备的中断号等。在VxWorks操作系统中访问PCI设备配置空间的API函数有pciConfigOutLong、pciConfigInLong等,它们分别完成对PCI设备配置空间的读写操作。

然后,根据PCI设备的配置参数,对不同的设备编写初始化程序、中断服务程序以及对PCI设备存储空间的访问程序。

很显然,用VxWorks操作系统实现虽然有一定的难度,但是系统具有很大的灵活性,系统比较小、适应性强,并且可以在工业控制计算机上运行。

图像采集系统的关键在于如何对大容量的信息进行暂存、压缩和传输等问题进行处理。本系统很好地解决了这三个难题。在图像信息暂存方面充分利用了DSP存储空间的可扩展性,保证了系统可暂存的信息量足够大;信息压缩是DSP最擅长做的事情,可以在很短的时间内完成大量的信息压缩工作;PCI总线的引入保证了信息在足够的带宽下进行快速传输。采用嵌入式VxWorks操作系统实现使得系统具有良好的灵活性和适应性,并大大降低了系统的成本。

引用地址:基于PCI总线的嵌入式实时DSP图像采集系统

本系统采用TI公司C6000系列DSP中的TMS320C6211作为系统的CPU。图像数据通过摄像机采集并输出模拟图像信号。这些信号经视频解码芯片转换为数字信号;再经FIFO输入DSP进行图像的增强、分割、特征提取和数据压缩等;然后输出信号经PCI解码芯片转换为符合PCI总线规范的标准信号,通过PCI总线接口传到上位机。系统的控制逻辑由EPLD(Erasable Programmable Logic Device)控制器实现。系统结构图如图1。

(1)视频解码芯片

系统中采集的图像信号采用Philips公司的SAA7111A完成A/D转换。SAA7111A允许四路模拟视频输入,具有两个模拟处理通道,支持四路CVBS模拟信号或二路Y/C模拟信号或二路CVBS信号和一路Y/C信号。SAA7111A对摄像头输入的标准PAL格式的模拟图像信号进行A/D转换,然后输出符合CCIR601格式的4:2:2的16位YUV数据到FIFO。其中亮度信号Y为8位、色度信号Cr和Cb合为8位数据。FIFO采用IDT公司的IDT72V215LB芯片,FIFO的深度为512%26;#215;18bit,支持STANDARD(标准)和FWFT(First Word Fall-Through,首字直接通过)两种工作模式。按照CCIR601格式,YUV图像分辨率为720%26;#215;576象素,当按行输出时,SAA7111A输出数据流大小为:720%26;#215;16=1440bit。因为DSP通过32位的SBSRAM接口与FIFO通信,故YUV数据写入FIFO时需要在FIFO之间实现乒乓切换。这时一行720%26;#215;16bit的数据在两片FIFO中存储变为360%26;#215;32bit。两片FIFO可以满足上述要求。FIFO的初始化及时序由EPLD实现。

本系统采用TI公司C6000系列DSP中的TMS320C6211作为系统的CPU。图像数据通过摄像机采集并输出模拟图像信号。这些信号经视频解码芯片转换为数字信号;再经FIFO输入DSP进行图像的增强、分割、特征提取和数据压缩等;然后输出信号经PCI解码芯片转换为符合PCI总线规范的标准信号,通过PCI总线接口传到上位机。系统的控制逻辑由EPLD(Erasable Programmable Logic Device)控制器实现。系统结构图如图1。

(1)视频解码芯片

系统中采集的图像信号采用Philips公司的SAA7111A完成A/D转换。SAA7111A允许四路模拟视频输入,具有两个模拟处理通道,支持四路CVBS模拟信号或二路Y/C模拟信号或二路CVBS信号和一路Y/C信号。SAA7111A对摄像头输入的标准PAL格式的模拟图像信号进行A/D转换,然后输出符合CCIR601格式的4:2:2的16位YUV数据到FIFO。其中亮度信号Y为8位、色度信号Cr和Cb合为8位数据。FIFO采用IDT公司的IDT72V215LB芯片,FIFO的深度为512%26;#215;18bit,支持STANDARD(标准)和FWFT(First Word Fall-Through,首字直接通过)两种工作模式。按照CCIR601格式,YUV图像分辨率为720%26;#215;576象素,当按行输出时,SAA7111A输出数据流大小为:720%26;#215;16=1440bit。因为DSP通过32位的SBSRAM接口与FIFO通信,故YUV数据写入FIFO时需要在FIFO之间实现乒乓切换。这时一行720%26;#215;16bit的数据在两片FIFO中存储变为360%26;#215;32bit。两片FIFO可以满足上述要求。FIFO的初始化及时序由EPLD实现。

(2)DSP图像处理模块

TMS320C6211是TI公司发布的面向视频处理领域的新款高速数字处理芯片,适用于移动通信基站、图像监控、雷达系统等对速度要求高和高度智能化的应用领域。存储空间分两部分:运行过程的临时数据存在Winbond公司的两片128Mbit的W981216BH中;系统程序则固化在FLASH存储器中,该存储器选用AMD公司生产的8Mbit的AM29LV800B。Flash存储器具有在线重写入功能。这对系统启动程序的修改和升级都带来了很大的方便。DSP处理模块结构如图2所示。图2中的HPI(Host Port Interface)为主机口;EMIF(External Memory Interface)为外部存储器接口,兼容同步/异步传输方式。

TMS320C6211 DSP的高速性能主要体现在以下方面:①TMS320C6211的存储空间最大可扩展到1GB,完全可以满足各种图像处理系统所需的内存空间,而且其最高时钟可达200MHz,峰值性能可达1600MIPS(百万条指令/秒)、2400MOPS(百万次操作/秒)。②并行处理结构。TMS320C6211芯片内有8个并行处理单元,分为相同的两组,并行结构大大提高芯片的性能。③芯片体系采用VelociTI结构。VelociTI是一种高性能的甚长指令字(VLIW)结构,单指令字字长为32bit,8个指令组成一个指令包,总字长为256bit。即每秒钟可以执行8条指令。VelociTI结构大大提高了DSP芯片的性能。④采用流水线操作实现高速度、高效率。TMS320C6211只有在流水线充分发挥作用的情况下,才能达到最高的峰值性能。与其他系列DSP相比,优势在于简化了流水线的控制以消除流水线互锁,并增加流水线的深度来消除传统流水线的取指、数据访问和乘法操作上的瓶颈。

本系统DSP主要完成从FIFO读出数据的处理以及压缩等。数据处理由自行编写的算法实现,数据压缩算法采用JPEG(Joint Photographic Expert Group)标准。当摄像头采集速度为每秒25帧图像时,它留给DSP处理的时间最多为每帧40ms。如果考虑系统有一定的延时以及处理后图像的存储时间,那么DSP处理一幅图像时间不能超过30ms。按照C6211的处理速度,在30ms内可以处理48M(0.03%26;#215;1600MIPS)条指令。DSP读出FIFO中的行数据并存入SDRAM,一帧图像有576行,在最后一行时会收到系统的帧中断,这时SDRAM中的图像数据总共有1440%26;#215;576=810KB。让C6211用36M条指令周期的时间处理810KB的数据显然绰绰有余。粗略的计算过程如下:

系统采用快速DCT(离散余弦变换),每8%26;#215;8矩阵需要11次乘法、29次加法,因此一帧图像的FDCT,共需要(11+29)%26;#215;720%26;#215;576%26;#215;2/64=518400个指令周期;对于量化模块,每8%26;#215;8矩阵需要64个量化指令周期,一帧需要64%26;#215;720%26;#215;576%26;#215;2/64=829440个指令周期;对于编码部分,假设编码后非0元素占25%,对每8%26;#215;8矩阵进行Zig-Zag扫描、编码估计需要120个指令周期,则共需120%26;#215;720%26;#215;576%26;#215;2/64=1555200个指令周期。按以上计算,在系统中进行JPEG编码大约需要2903040个指令周期,耗时19.3536ms(TMS320C6211工作在150MHz时)。可以看出,实际需要的指令远小于36M条,而时间也远小于30ms,DSP完全可以实时处理从FIFO传过来的数据。

(3)PCI总线模块

PCI总线规范吸引人的地方不仅是其高速度,更在于

(2)DSP图像处理模块

TMS320C6211是TI公司发布的面向视频处理领域的新款高速数字处理芯片,适用于移动通信基站、图像监控、雷达系统等对速度要求高和高度智能化的应用领域。存储空间分两部分:运行过程的临时数据存在Winbond公司的两片128Mbit的W981216BH中;系统程序则固化在FLASH存储器中,该存储器选用AMD公司生产的8Mbit的AM29LV800B。Flash存储器具有在线重写入功能。这对系统启动程序的修改和升级都带来了很大的方便。DSP处理模块结构如图2所示。图2中的HPI(Host Port Interface)为主机口;EMIF(External Memory Interface)为外部存储器接口,兼容同步/异步传输方式。

TMS320C6211 DSP的高速性能主要体现在以下方面:①TMS320C6211的存储空间最大可扩展到1GB,完全可以满足各种图像处理系统所需的内存空间,而且其最高时钟可达200MHz,峰值性能可达1600MIPS(百万条指令/秒)、2400MOPS(百万次操作/秒)。②并行处理结构。TMS320C6211芯片内有8个并行处理单元,分为相同的两组,并行结构大大提高芯片的性能。③芯片体系采用VelociTI结构。VelociTI是一种高性能的甚长指令字(VLIW)结构,单指令字字长为32bit,8个指令组成一个指令包,总字长为256bit。即每秒钟可以执行8条指令。VelociTI结构大大提高了DSP芯片的性能。④采用流水线操作实现高速度、高效率。TMS320C6211只有在流水线充分发挥作用的情况下,才能达到最高的峰值性能。与其他系列DSP相比,优势在于简化了流水线的控制以消除流水线互锁,并增加流水线的深度来消除传统流水线的取指、数据访问和乘法操作上的瓶颈。

本系统DSP主要完成从FIFO读出数据的处理以及压缩等。数据处理由自行编写的算法实现,数据压缩算法采用JPEG(Joint Photographic Expert Group)标准。当摄像头采集速度为每秒25帧图像时,它留给DSP处理的时间最多为每帧40ms。如果考虑系统有一定的延时以及处理后图像的存储时间,那么DSP处理一幅图像时间不能超过30ms。按照C6211的处理速度,在30ms内可以处理48M(0.03%26;#215;1600MIPS)条指令。DSP读出FIFO中的行数据并存入SDRAM,一帧图像有576行,在最后一行时会收到系统的帧中断,这时SDRAM中的图像数据总共有1440%26;#215;576=810KB。让C6211用36M条指令周期的时间处理810KB的数据显然绰绰有余。粗略的计算过程如下:

系统采用快速DCT(离散余弦变换),每8%26;#215;8矩阵需要11次乘法、29次加法,因此一帧图像的FDCT,共需要(11+29)%26;#215;720%26;#215;576%26;#215;2/64=518400个指令周期;对于量化模块,每8%26;#215;8矩阵需要64个量化指令周期,一帧需要64%26;#215;720%26;#215;576%26;#215;2/64=829440个指令周期;对于编码部分,假设编码后非0元素占25%,对每8%26;#215;8矩阵进行Zig-Zag扫描、编码估计需要120个指令周期,则共需120%26;#215;720%26;#215;576%26;#215;2/64=1555200个指令周期。按以上计算,在系统中进行JPEG编码大约需要2903040个指令周期,耗时19.3536ms(TMS320C6211工作在150MHz时)。可以看出,实际需要的指令远小于36M条,而时间也远小于30ms,DSP完全可以实时处理从FIFO传过来的数据。

(3)PCI总线模块

PCI总线规范吸引人的地方不仅是其高速度,更在于

它适应了现代I/O设备对系统的要求,对PCI扩展卡及器件能进行全自动配置,并且只需很少的接口逻辑就可以实现并支持其他总线系统。

TMS320C6211的HPI口不支持PCI总线的无缝接口。本系统采用TI公司的PCI2040实现DSP的HPI与PCI总线的连接。DSP处理后的数据经HPI口输出到PCI2040进行解码,然后输出到PCI总线上。其逻辑结构如图3所示。

PCI2040是TI公司设计的专门用来完成C5000系列和C6000系列DSP与PCI总线进行接口的专用芯片。PCI2040符合PCI局部总线2.2规范,能够方便地实现PCI总线与TMS320C54X或TMS320C6X DSP的HPI接口的无缝连接。PCI2040可以兼容3.3V和5V,以适应不同的PCI总线电压。PCI2040与C6211之间不需要信号的电平转换,也不需要额外的控制逻辑电路,接口电路十分简单。

在本系统中,PCI2040上存在两种电压:5V和3.3V。其中3.3V是HPI口电压,5V是PCI总线电压。PCI2040启动时需要对其PCI总线寄存器和HPI寄存器参数进行预加载。系统中PCI解码模块包括一块配置ROM——AT24C08A,属于EEPROM型ROM,便于对配置参数修改和升级。当系统启动时,存储在AT24C08A的数据下载到PCI2040的寄存器中并进行配置。

图3中HINT[3:0]、HCS[3:0]、HRDY[3:0]、HRST[3:0]分别与四片DSP中的相应信号相连。即PCI2040可以同时与四片DSP接口。

2 系统的软件设计

本软件系统包括两部分,即底层软件和系统软件。

底层软件主要是DSP图像处理算法以及启动等运行程序。这些程序主要在CCS环境下由C语言编写并进行汇编优化。CCS即Code Composer Studio,是TI公司发布的DSP软件运行环境。

在系统软件方面,基于PCI总线的图像处理系统面临的难点颇多,其中难度最大的是PCI驱动问题。当然这对于不同的系统软件可能难度各异。若在Windows操作系统下,可以充分利用Windows的窗口特性:一方面,因为Windows技术成熟,软件编写相对比较简单;另一方面,在Windows平台下,PCI驱动无需开发,可以直接利用Windows的PCI驱动程序实现图像卡的驱动。但是Windows操作系统比较庞大,而且无法依照系统的需要进行自由裁减,不适合做成嵌入式系统。这里主要阐述在VxWorks操作系统下的软件设计方法。

相对于Windows操作系统,VxWorks的优点表现在:①VxWorks系统具有较好的可裁减性,可裁剪的组件超过80个,用户可根据自己系统的功能目标通过交叉开发环境方便地配置;②VxWorks支持应用程序的动态链接和动态下载,开发者省去了每次调试都将应用程序与操作系统内核进行链接和下载的步骤,缩短了编辑/调试周期;③VxWorks具有较好的兼容性,它是最早兼容POSIX1003.1b标准的嵌入式实时操作系统之一;④VxWorks具有很高的可靠性和稳定性;⑤VxWorks具有很好的实时性,实时性的强弱以完成规定功能和做出响应时间的长短来衡量。VxWorks的多任务机制对任务的控制采用了优先级抢占(Preemptive Priority Scheduling)和轮转调度(Round-Robin Scheduling)机制。这充分保证了可靠的实时性,使同样的硬件配置能满足更强的实时性要求,为应用的开发留下更大的余地。

为阐明如何在VxWorks操作系统下实现PCI总线的驱动,还需了解PCI设备的配置空间。PCI设备有三种物理存储空间:配置空间、存储器空间和I/O空间。配置空间是长度为256字节的一段连续空间,空间的定义如图4?眼1?演。在配置空间中只读空间有设备标识、供应商代码、修改版本、分类代码以及头标类型。其中供应商代码用来标识设备供应商的代码;设备标识用来标识某一特殊的设备;修改版本标识设备的版本号;分类代码用来标识设备的种类;而头标类型用来标识头类型以及是否为多功能设备。除供应商代码之外,其他字段的值由供应商分配。

基地址寄存器最重要的功能是分配PCI设备的系统地址空间。在基地址寄存器中bit0(最低位)用来标识存储器空间还是I/O地址空间,基地址寄存器映射到存储器空间时bit0为“0”,映射到I/O地址空间时bit0为“1”。

它适应了现代I/O设备对系统的要求,对PCI扩展卡及器件能进行全自动配置,并且只需很少的接口逻辑就可以实现并支持其他总线系统。

TMS320C6211的HPI口不支持PCI总线的无缝接口。本系统采用TI公司的PCI2040实现DSP的HPI与PCI总线的连接。DSP处理后的数据经HPI口输出到PCI2040进行解码,然后输出到PCI总线上。其逻辑结构如图3所示。

PCI2040是TI公司设计的专门用来完成C5000系列和C6000系列DSP与PCI总线进行接口的专用芯片。PCI2040符合PCI局部总线2.2规范,能够方便地实现PCI总线与TMS320C54X或TMS320C6X DSP的HPI接口的无缝连接。PCI2040可以兼容3.3V和5V,以适应不同的PCI总线电压。PCI2040与C6211之间不需要信号的电平转换,也不需要额外的控制逻辑电路,接口电路十分简单。

在本系统中,PCI2040上存在两种电压:5V和3.3V。其中3.3V是HPI口电压,5V是PCI总线电压。PCI2040启动时需要对其PCI总线寄存器和HPI寄存器参数进行预加载。系统中PCI解码模块包括一块配置ROM——AT24C08A,属于EEPROM型ROM,便于对配置参数修改和升级。当系统启动时,存储在AT24C08A的数据下载到PCI2040的寄存器中并进行配置。

图3中HINT[3:0]、HCS[3:0]、HRDY[3:0]、HRST[3:0]分别与四片DSP中的相应信号相连。即PCI2040可以同时与四片DSP接口。

2 系统的软件设计

本软件系统包括两部分,即底层软件和系统软件。

底层软件主要是DSP图像处理算法以及启动等运行程序。这些程序主要在CCS环境下由C语言编写并进行汇编优化。CCS即Code Composer Studio,是TI公司发布的DSP软件运行环境。

在系统软件方面,基于PCI总线的图像处理系统面临的难点颇多,其中难度最大的是PCI驱动问题。当然这对于不同的系统软件可能难度各异。若在Windows操作系统下,可以充分利用Windows的窗口特性:一方面,因为Windows技术成熟,软件编写相对比较简单;另一方面,在Windows平台下,PCI驱动无需开发,可以直接利用Windows的PCI驱动程序实现图像卡的驱动。但是Windows操作系统比较庞大,而且无法依照系统的需要进行自由裁减,不适合做成嵌入式系统。这里主要阐述在VxWorks操作系统下的软件设计方法。

相对于Windows操作系统,VxWorks的优点表现在:①VxWorks系统具有较好的可裁减性,可裁剪的组件超过80个,用户可根据自己系统的功能目标通过交叉开发环境方便地配置;②VxWorks支持应用程序的动态链接和动态下载,开发者省去了每次调试都将应用程序与操作系统内核进行链接和下载的步骤,缩短了编辑/调试周期;③VxWorks具有较好的兼容性,它是最早兼容POSIX1003.1b标准的嵌入式实时操作系统之一;④VxWorks具有很高的可靠性和稳定性;⑤VxWorks具有很好的实时性,实时性的强弱以完成规定功能和做出响应时间的长短来衡量。VxWorks的多任务机制对任务的控制采用了优先级抢占(Preemptive Priority Scheduling)和轮转调度(Round-Robin Scheduling)机制。这充分保证了可靠的实时性,使同样的硬件配置能满足更强的实时性要求,为应用的开发留下更大的余地。

为阐明如何在VxWorks操作系统下实现PCI总线的驱动,还需了解PCI设备的配置空间。PCI设备有三种物理存储空间:配置空间、存储器空间和I/O空间。配置空间是长度为256字节的一段连续空间,空间的定义如图4?眼1?演。在配置空间中只读空间有设备标识、供应商代码、修改版本、分类代码以及头标类型。其中供应商代码用来标识设备供应商的代码;设备标识用来标识某一特殊的设备;修改版本标识设备的版本号;分类代码用来标识设备的种类;而头标类型用来标识头类型以及是否为多功能设备。除供应商代码之外,其他字段的值由供应商分配。

基地址寄存器最重要的功能是分配PCI设备的系统地址空间。在基地址寄存器中bit0(最低位)用来标识存储器空间还是I/O地址空间,基地址寄存器映射到存储器空间时bit0为“0”,映射到I/O地址空间时bit0为“1”。

PCI设备的驱动过程主要包括下面几个步骤:

首先,PCI设备的查找。在嵌入式操作系统中一般提供相应的API函数查找。在VxWorks操作系统中通过函数pciFindDevice(PCI_VENDOR_ID,PCI_DEVICE,index, &pciBus, &pciDevice,&pciFunc_可以找到供应商代码为PCI_VENDOR_ID、设备标识为PCI_DEVICE的第n(index+1)个设备,并且返回总线号、设备号以及功能号,分别保存于&pciBus、&pciDevice、&pciFunc中。

其次,PCI设备的配置。通过操作系统提供的API函数访问PCI设备的配置空间,配置PCI设备基址寄存器的配置、中断配置、ROM基地址寄存器的配置等,这样可以得到PCI的存储器空间和I/O地址空间映射、设备的中断号等。在VxWorks操作系统中访问PCI设备配置空间的API函数有pciConfigOutLong、pciConfigInLong等,它们分别完成对PCI设备配置空间的读写操作。

然后,根据PCI设备的配置参数,对不同的设备编写初始化程序、中断服务程序以及对PCI设备存储空间的访问程序。

很显然,用VxWorks操作系统实现虽然有一定的难度,但是系统具有很大的灵活性,系统比较小、适应性强,并且可以在工业控制计算机上运行。

图像采集系统的关键在于如何对大容量的信息进行暂存、压缩和传输等问题进行处理。本系统很好地解决了这三个难题。在图像信息暂存方面充分利用了DSP存储空间的可扩展性,保证了系统可暂存的信息量足够大;信息压缩是DSP最擅长做的事情,可以在很短的时间内完成大量的信息压缩工作;PCI总线的引入保证了信息在足够的带宽下进行快速传输。采用嵌入式VxWorks操作系统实现使得系统具有良好的灵活性和适应性,并大大降低了系统的成本。

PCI设备的驱动过程主要包括下面几个步骤:

首先,PCI设备的查找。在嵌入式操作系统中一般提供相应的API函数查找。在VxWorks操作系统中通过函数pciFindDevice(PCI_VENDOR_ID,PCI_DEVICE,index, &pciBus, &pciDevice,&pciFunc_可以找到供应商代码为PCI_VENDOR_ID、设备标识为PCI_DEVICE的第n(index+1)个设备,并且返回总线号、设备号以及功能号,分别保存于&pciBus、&pciDevice、&pciFunc中。

其次,PCI设备的配置。通过操作系统提供的API函数访问PCI设备的配置空间,配置PCI设备基址寄存器的配置、中断配置、ROM基地址寄存器的配置等,这样可以得到PCI的存储器空间和I/O地址空间映射、设备的中断号等。在VxWorks操作系统中访问PCI设备配置空间的API函数有pciConfigOutLong、pciConfigInLong等,它们分别完成对PCI设备配置空间的读写操作。

然后,根据PCI设备的配置参数,对不同的设备编写初始化程序、中断服务程序以及对PCI设备存储空间的访问程序。

很显然,用VxWorks操作系统实现虽然有一定的难度,但是系统具有很大的灵活性,系统比较小、适应性强,并且可以在工业控制计算机上运行。

图像采集系统的关键在于如何对大容量的信息进行暂存、压缩和传输等问题进行处理。本系统很好地解决了这三个难题。在图像信息暂存方面充分利用了DSP存储空间的可扩展性,保证了系统可暂存的信息量足够大;信息压缩是DSP最擅长做的事情,可以在很短的时间内完成大量的信息压缩工作;PCI总线的引入保证了信息在足够的带宽下进行快速传输。采用嵌入式VxWorks操作系统实现使得系统具有良好的灵活性和适应性,并大大降低了系统的成本。

面向自然语言处理的深度学习:用Python创建神经网络

面向自然语言处理的深度学习:用Python创建神经网络 NJM022M

NJM022M

京公网安备 11010802033920号

京公网安备 11010802033920号