本文描述了一个精密时钟发生器电路板的设计,该设计可在一些电信或数据通信专门实验室测试工作中用作波形发生器。该时钟发生器输出一组固定频率的时钟,使用一个外部同步时钟参考作为输入。

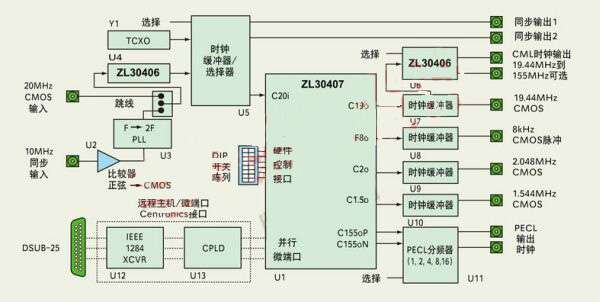

设计的核心是U1,即ZL30407光同步网络/同步数字系列(Sonet/SDH)网络元件PLL(见图1)。ZL30407将产生一组同步到20MHz输入主时钟的SONET和PDH时钟。当与Stratum 3或更高质量的主时钟耦合时,其输出将满足Stratum 3E漂移精度要求。

ZL30407可通过DIP开关配置为运行于硬件模式,还可以对该器件输出时钟小频率偏移进行编程。为此,器件必须工作在软件模式。软件模式操作需要使用一个外部控制器,该控制器通过8位并行端口来读和写内部设备寄存器。例如,ZL30407微端口接口可用于与IEEE 1284 PC打印机端口(U12)和CPLD(U13)连接,以实现端口接口逻辑。

一个峰峰值大约为1V的10MHz正弦同步参考输入,通过比较器(U2)转换成CMOS方波时钟,然后通过时钟倍频器(U3)使频率加倍。多时钟发生器板可以通与另一块电路板的Syncout输出连接并作为该板的20MHz输入,而相互同步。

ZL30406 PLL(U4)用作抖动滤波器,以净化选定的输入时钟。一个额外的时钟缓冲器(U5)用于在本地 TCXO(Y1)和外部同步参考之间选择一个作为主电路板时钟。为使 ZL30406 VCO的频率以20MHz为中心,外部电阻必须采用数据表单指导准则中给出的阻值。

ZL30407有12个输出时钟,图中电路中显示了其中5个。CMOS 输出包括19.44MHz、8kHz帧脉冲、2.048 MHz 和1.544 MHz输出。输出时钟引脚到扇出缓冲器 (U7、U8、U9和U10)以及连接器的分配没有特定限制,只要适合目标应用即可。每个时钟均进行了缓冲,以提供一定的扇出和到同轴连接器的电缆驱动能力。

第二个ZL30406(U6)将C19o的一个输出时钟转换为抖动很低的差分CML输出时钟,可选择四种倍频(19.44 MHz、38.88MHz、77.76MHz和155.52MHz)。U11是一个可通过硬件配置的差分时钟分频器,可通过DIP开关进行编程,以便对ZL30407芯片的155MHz LVDS输出时钟进行1、2、4、8或16分频。

|

| 图1:这个精密时钟发生器电路板采用ZL30407 SONET/SDH网络元件PLL。 |

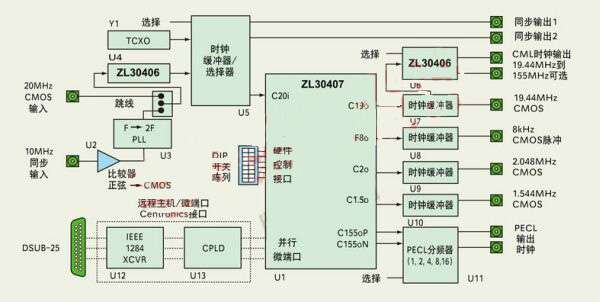

每个输出时钟均进行了抖动测量,以验证设计的性能。总之,观测到的时钟抖动符合ZL30407和ZL30406器件的技术规格。ZL30406输出的RMS抖动为2ps到8ps,这与使用12KHz~20MHz的测量带宽在一个质量良好的函数发生器的输出上测得的结果相当接近。

|

| 图2:ZL30406的155MHz CML输出时钟的相位噪声与在质量良好的函数发生器的输出上测得的结果相当。 |

图2显示了ZL30406(U6)的155MHz CML输出时钟的相位噪声图。ZL30406 PLL环路滤波器带宽配置为14kHz。

关键字:时钟 发生器 输出

引用地址:

万能时钟发生器板的设计

推荐阅读最新更新时间:2024-05-07 15:53

新型以太网控制器ENC28J60及其接口技术

引言 ENC28J60是Microchip Technology(美国微芯科技公司)近期推出的28引脚独立以太网控制器。 在此之前,嵌入式系统开发可选的独立以太网控制器都是为个人计算机系统设计的,如RTL8019、AX88796L、DM9008、 CS8900A、LAN91C111等。这些器件不仅结构复杂,体积庞大,且比较昂贵。目前市场上大部分以太网控制器的封装均超过80引脚,而符合 IEEE 802.3协议的ENC28J60只有28引脚,既能提供相应的功能,又可以大大简化相关设计,减小空间。 图1 ENC28J60的硬件连接 1 结构和功能 采用业界标准串行外设接口(SPI)的以太网控制器

[应用]

如何利用频谱分析仪、前置放大器和信号发生器测量噪声系

只使用频谱分析仪和前置放大器,可以进行多种噪声系数的测量。通过简单的频谱分析仪、前置放大器和信号发生器,可以实现对被测器件频率的覆盖。此法的精度低于需要校正噪声源的Y因子技术,其精度与分析器关注频率的幅度精度相当。步骤如下: 1.将信号发生器和频谱分析仪设定为噪声系数的频率,以测量设备的增益。将此值作为Gain(D)。 2.用相同的方法测量前置放大增益。将此值作为Gain(P)。 3.断开频谱分析仪的输入,将输入衰减值设为0dB。没有任何连接的前置放大器输入。将其输出与频谱分析器输入。做这个连接,你可以看到分析器显示出的平均噪音级增加。 4.将被测装置的输入连接到特性阻抗上,将输出与前置放大器输入相连接。分析器显示的噪音级别在

[测试测量]

时钟闹铃控制电路原理图

原理图说明: 1、共阳极四位一体12引脚数码管引脚号是:将数码管的数字面朝向观察者,左下角是第1脚,逆时针方向依次是2、3、4、5、6、7、8、9、10、11、12脚。 2、如果是单个的数码管或两位一体的数码管,先测出数字显示段控制引脚和公共控制引脚,再将四个数码管的相同的段控制引脚用导线并联连接在一起后(每位数码管共八段即八根连接导线),连接在电阻R5~R13上,公共控制引脚分别连接到三极管 Q1 到 Q4 的发射极上。 3、用 40 脚的集成块插座焊接在电路板上,集成块 AT89C51 写入程序后插入到集成块插座上。 4、自己设计控制程序或用黄有全老师的程序; 5、时钟控制输出由继电器执行,控

[单片机]

stm32单片机引脚介绍及功能

stm32是一种ARM Cortex-M内核单片机,下面小编为大家介绍一下单片机引脚介绍及功能。单片机旁边的一排金属针脚就是引脚,不同的引脚有不同的功能。 引脚大概分为4种,分别是电源、时钟、控制和I/O引脚。stm32的引脚一般有GPIO和AFIO两种用途。 比如有的引脚是电源正极和黑色标记的电源负极,这是来给单片机提供电源的,要把电流引到对应的引脚才能正常工作。 还有晶体震荡电路反向输入端和输出端引脚,晶体能够为单片机提供基本的震荡源。如果没有晶振的话,单有电源单片机是不能启动的,就和人们的心跳一样。 RESET(PC6)复位信号输入端引脚是用来重启单片机的,和电脑一样,有时候单片机也会死机,这个时候就需要RE

[单片机]

TYPE-C转DC转接头方案FS8024A支持9V、12V、15V、20V电压输出

如今随着这几年的USB-C PD适配器的普及,消费者手上的PD适配器越来越普遍,如何让以前的电源适配器也可以用上PD适配器呢?如此一来以前的电源适配器坏了,就不需要费心费力的寻找相同的适配器进行更换,甚至于只能将整个设备换掉。 不妨加入一颗受电端PD SINK取电芯片——FS8024A。小雅将为大家介绍FS8024A芯片TYPE-C转DC转接头的详细方案。 一.概述 FS8024A 是泛海微电子针对 USB PD 协议开发的一款兼容 USB PD 的通信芯片。输入端主要接 PD 的适配器,输出端配置输出固定的电压。FS8024A 从支持 USB PD 的适配器取电,然后供电给设备。比如可以配置适配器输出需要的电压,给无线充

[嵌入式]

什么是信号发生器 信号发生器类型总结

信号发生器是一种以波的形式产生电信号的测试设备。这被用作对被测试项目的刺激。 各种形式的信号发生器广泛用于测试和开发系统,与其他测试仪器一起使用。 当查看信号发生器是什么时,会发现它们有多种形式——信号发生器有多种类型,每一种都用于提供不同形式的信号。一些提供射频信号,另一些提供音频信号,一些可以提供不同形状的波形,而另一些可能只提供脉冲。 信号发生器已使用多年。按照当今不同类型信号发生器的标准,早期类型非常基本。性能水平以及可用设施的种类已经增加和改进。 什么是信号发生器 信号发生器有多种形式,能够为不同的测试应用产生各种波形。这些测试仪器中的一些用于射频测试领域,而另一些则用于音频测试,

[测试测量]

MSP430时钟系统三

上一篇最后的部分我们用一个例程来对时钟系统的设置有了个正面的认识,只给出了程序没有仿真图示,原因是我所使用的仿真环境下对时钟系统的设置是无效的,选择时钟源没有效果,设置通过指定的引脚同步输出波形也没有效果,只有在通过外部时钟源输入时钟信号才可以设置,这个的使用我们将在定时器的说明时给出。其实还是用块板子比较踏实,仿真和实际有时候真是搞笑,那天他们用单片机做个东西,仿真可以过的在板子上就没反应。倒是仿真没反应的到了板子上竟然很随意的样子,搞不懂。 寄存器 符号 寄存器类型 地址 初始化状态 DCO控制寄存器 DCOCTL 读/写 056H 带PUC的060H 基础时钟系统控制寄存器1 BCSCTL1 读/写 057H 带POR的

[单片机]

s3c2440系统时钟详解

一、S3C2440系统时钟体系 S3C2440的时钟控制逻辑可以外接晶振,然后通过内部电路产生时钟源;也可以直接使用内部提供的时钟源,他们通过引脚的设置来选择。时钟逻辑给整个芯片提供了3中时钟:FCLK用于CPU核、HCLK用于AHB总线上设备,比如CPU核、存储器控制器、中断控制器、LCD控制器、DMA控制器和USB主机模块等;PCLK用于用于APB总线上的设备,比如看门狗、IIS、I2C、PWM定时器、MMC接口、ADC、UART、GPIO、RTC和SPI等。 AHB(Advanced High performance Bus)系统总线总线主要用于高性能模块(如CPU、DMA和DSP等);APB(Advanced Periph

[单片机]

电力工程设计手册 24 电力系统规划设计

电力工程设计手册 24 电力系统规划设计

京公网安备 11010802033920号

京公网安备 11010802033920号