摘要:论述了粗粒度可配置计算结构的特点、发展现状和未来发展方向。

关键词:粗粒度 配置 并行计算

可配置计算又称为自适应计算。它是由多个具有可重配置功能的功能单元(PE)和可以配置不同数据传递方向的连续线路一起构成的计算机结构,如图1所示。现在,可重配置计算分为两类:细粒度配置和粗粒度配置。细粒度配置计算主要体现在FPGA(现场可编程逻辑阵列),它在数字逻辑芯片开发和系统设计等方面应用非常广泛,但由于细粒度的原因,其实际逻辑单元仅占实际芯片面积的10%,其余被开关、RAM、布线网络所占有,功耗和工作频率都不是非常理想,在处理一些规则运算,如乘法时效率不高。相对的,粗粒度配置计算的粒度一般为4、8、16、32位,非常适合进行算法级操作。试想一下,如果要处理10000%26;#215;20000像素的图片,用现在的计算机能够实时完成吗?但应用粗粒度可配置计算结构设计的计算机能够完成。在数字信号处理领域,算法一般都遵循90/10的规律。即在一个算法中,90%是重复单一或类似功能的规则操作,不规则的静态操作只占10%。如果针对算法中的规则操作设计处理单元(PE),并通过多个处理单元(PE)组成网络进行并行计算,在功耗比较小时,其计算能力或者说处理速度将非常快,能够完成大数据量、大运算量的算法。同时随着超大规模集成电路的发展,特别是SOC(单芯片系统集成)技术的兴起,在一个芯片中,可以很容易集成几百万门的电路,为粗粒度可配置计算的研究和应用提供了基础。

1 粗粒度可配置结构的数据处理

在可重配置计算中,一般提供了配置过程和计算过程。根据计算任务的不同,首先对处理单元和连接网络进行相应的配置,之后再对数据流进行计算。图2是传统的处理器与粗粒度可重配置结构数据处理流程的比较。从图2中可以看到,冯%26;#183;诺曼类型的指令流被配置流和数据流所代替。粗粒度可配置计算结构将软件的灵活与硬件的高速结合在一起,从崭新的角度设计数字信号处理器。与传统的处理器相比,具有以下特点:

(1)传统数据处理的指令流被配置流所代替,不再是单个指令的乘加或移位运算,而是不同功能如滤波、FFT、矩阵相乘等的顺序执行。

(2)各单元功能可以配置,与传统的处理器指令不同,设计全新的配置指令。通过配置为不同功能单元的组合,完成相应的功能。由于是用硬件实现各功能,功耗低。

1 粗粒度可配置结构的数据处理

在可重配置计算中,一般提供了配置过程和计算过程。根据计算任务的不同,首先对处理单元和连接网络进行相应的配置,之后再对数据流进行计算。图2是传统的处理器与粗粒度可重配置结构数据处理流程的比较。从图2中可以看到,冯%26;#183;诺曼类型的指令流被配置流和数据流所代替。粗粒度可配置计算结构将软件的灵活与硬件的高速结合在一起,从崭新的角度设计数字信号处理器。与传统的处理器相比,具有以下特点:

(1)传统数据处理的指令流被配置流所代替,不再是单个指令的乘加或移位运算,而是不同功能如滤波、FFT、矩阵相乘等的顺序执行。

(2)各单元功能可以配置,与传统的处理器指令不同,设计全新的配置指令。通过配置为不同功能单元的组合,完成相应的功能。由于是用硬件实现各功能,功耗低。

(3)不存在传统处理器从RAM中读取指令问题,且结构中有多个RAM区和I/O可用,可有效解决冯%26;#183;诺曼瓶颈,加快数据处理速度。

(4)多个单元的网络结构,链路可配,具有极强的并行处理能力。将编译之后的算子网表与实际结构中的处理单元一一对应的过程是映射与路径寻优的过程,主要指map(映射)、place(放置)、route(路由)三步。涉及的优化算法主要有:模拟退火算法、遗传算法、谈判拥塞算法等。

2 发现现状

粗粒度重配置计算最早见于20世纪60年代,是Gerald Estrin教授提出的“固定加可变结构计算机”,但因为受当时芯片制造水平的限制,只是一个概念而已。进入90年代,随着VLSI(超大规模集成电路)技术的发展,以“可编程开关(programswitch)”为基础的粗粒度可配置计算结构不断被开发出来,并在图像滤波、特征提取、目标识别与跟踪、通讯算法等方面展示出了非凡的性能与潜力。表1列出的是国外部分粗粒度计算项目,国内此项研究尚未见报道。在商业应用中,做得比较好的是PACT极端并行处理公司,其包含64个PE的XPP64A1在主频200MHz时MAC(乘加)运算已经达到了12.8GigaMACs/秒。

(3)不存在传统处理器从RAM中读取指令问题,且结构中有多个RAM区和I/O可用,可有效解决冯%26;#183;诺曼瓶颈,加快数据处理速度。

(4)多个单元的网络结构,链路可配,具有极强的并行处理能力。将编译之后的算子网表与实际结构中的处理单元一一对应的过程是映射与路径寻优的过程,主要指map(映射)、place(放置)、route(路由)三步。涉及的优化算法主要有:模拟退火算法、遗传算法、谈判拥塞算法等。

2 发现现状

粗粒度重配置计算最早见于20世纪60年代,是Gerald Estrin教授提出的“固定加可变结构计算机”,但因为受当时芯片制造水平的限制,只是一个概念而已。进入90年代,随着VLSI(超大规模集成电路)技术的发展,以“可编程开关(programswitch)”为基础的粗粒度可配置计算结构不断被开发出来,并在图像滤波、特征提取、目标识别与跟踪、通讯算法等方面展示出了非凡的性能与潜力。表1列出的是国外部分粗粒度计算项目,国内此项研究尚未见报道。在商业应用中,做得比较好的是PACT极端并行处理公司,其包含64个PE的XPP64A1在主频200MHz时MAC(乘加)运算已经达到了12.8GigaMACs/秒。

从表1可以发现,现有粗粒度可重配置计算都有其相应的应用领域,没有形成一个统一固定的模式,系统结构、组织方式、粒度大小及编译环境各不相同。开发高效通用的粗粒度计算结构仍有一定的难度,这也是可配置计算结构的重要研究方向。

表1 粗粒度结构技术总结

项目名称

结构

粒度

组织

映射方法

应用目标

PADDI

交叉条

16位

中央交叉条

选通

DSP

DFFC

3维阵列

8,16位

直接与可配连接

协同编译

图像处理

PADDI-2

交叉条

16位

多交叉条

选通

DSP

DP-FPGA

2维阵列

1%26;amp;4位,多粒度

不均一布线通道

天关箱选通

规则路径

KressArray

2维阵列

可选路径宽度

NN%26;amp;总线分段

协同编译

自适应

Colt

2维阵列

1%26;amp;16位,不均一

实时配置

高动态可配

RaPID

1维阵列

16位

可分段总线

通道选通

流水线

ACM

2维阵列

32位,多粒度

矩阵连接

协同编译

普通

Lirmm

环形

16位

主次数据流

协同编译

运动估计等

Matrix

2维网格

8位,多粒度

8NN,全局线

多级长度

普通

RAW

2维网格

8位,多粒度

8NN,开关连接

开关箱选通

普通

Pleiades

网格/交叉条

多粒度

可分段的交叉条

开关箱选通

多媒体

PipeRench

1维阵列

128位

调度

流水线

REMARC

2维阵列

16位

NN,全长度总线

多媒体

MorphoSys

2维网格

16位

NN,长度2%26;amp;3线段

手动Place%26;amp;route

CHESS

六角形网格

4位,多粒度

8NN,总线

JHDL编译

多媒体

DreAM

2维阵列

8%26;amp;16位

NN,分段总线

协同编译

下一代无线

CS2000

2维阵列

16%26;amp;32位

不均一阵列

协同编译

通讯

XPP64A1

2维阵列

24位

NN,分段配置总线

协同编译

图像处理

3 未来的发展

粗粒度可配置计算将软件的灵活与硬件的高效、低功耗结合在一起,利用硬件来实现软件算法。虽然灵活性上要比DSP和计算机差一些,但计算效率和处理能力上却有很大的提高。图3是数字信号处理领域目前各类器件性能的简单比较。

此结构芯片非常适合图像数据处理,同时另一应用方面——软件无线电的硬件平台,也正促进其发展。

从表1可以发现,现有粗粒度可重配置计算都有其相应的应用领域,没有形成一个统一固定的模式,系统结构、组织方式、粒度大小及编译环境各不相同。开发高效通用的粗粒度计算结构仍有一定的难度,这也是可配置计算结构的重要研究方向。

表1 粗粒度结构技术总结

项目名称

结构

粒度

组织

映射方法

应用目标

PADDI

交叉条

16位

中央交叉条

选通

DSP

DFFC

3维阵列

8,16位

直接与可配连接

协同编译

图像处理

PADDI-2

交叉条

16位

多交叉条

选通

DSP

DP-FPGA

2维阵列

1%26;amp;4位,多粒度

不均一布线通道

天关箱选通

规则路径

KressArray

2维阵列

可选路径宽度

NN%26;amp;总线分段

协同编译

自适应

Colt

2维阵列

1%26;amp;16位,不均一

实时配置

高动态可配

RaPID

1维阵列

16位

可分段总线

通道选通

流水线

ACM

2维阵列

32位,多粒度

矩阵连接

协同编译

普通

Lirmm

环形

16位

主次数据流

协同编译

运动估计等

Matrix

2维网格

8位,多粒度

8NN,全局线

多级长度

普通

RAW

2维网格

8位,多粒度

8NN,开关连接

开关箱选通

普通

Pleiades

网格/交叉条

多粒度

可分段的交叉条

开关箱选通

多媒体

PipeRench

1维阵列

128位

调度

流水线

REMARC

2维阵列

16位

NN,全长度总线

多媒体

MorphoSys

2维网格

16位

NN,长度2%26;amp;3线段

手动Place%26;amp;route

CHESS

六角形网格

4位,多粒度

8NN,总线

JHDL编译

多媒体

DreAM

2维阵列

8%26;amp;16位

NN,分段总线

协同编译

下一代无线

CS2000

2维阵列

16%26;amp;32位

不均一阵列

协同编译

通讯

XPP64A1

2维阵列

24位

NN,分段配置总线

协同编译

图像处理

3 未来的发展

粗粒度可配置计算将软件的灵活与硬件的高效、低功耗结合在一起,利用硬件来实现软件算法。虽然灵活性上要比DSP和计算机差一些,但计算效率和处理能力上却有很大的提高。图3是数字信号处理领域目前各类器件性能的简单比较。

此结构芯片非常适合图像数据处理,同时另一应用方面——软件无线电的硬件平台,也正促进其发展。

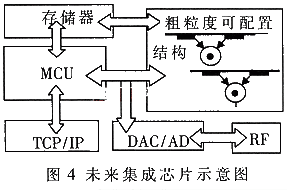

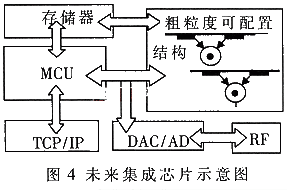

现在,软件无线电的研究在我国正不断深入。其目标之一是将不同制式、不同频段的信号利用单一器件进行接收和发送,并且越早地将射频信号变为数字信号进行处理越好。这一方面促进了智能天线和软件接口协议的研究,另一方面也要求有高速低功耗、功能可变的硬件相配合。现阶段国内应用的硬件主要是DSP和计算机,它们在功耗和速度方面都不及粗粒度可配置计算。粗粒度可配置计算结构,通过处理单元的配置、数据路径的配置,使数据在流动中完成运算。在接近ASIC(专用集成电路)性能的同时,又具有一定的灵活性。应用可配置计算系统,既可以更早地将模拟信号转变为数字信号进行处理,利于系统性能的提高,又可以进一步将其包装为IP(知识产权)核,与目前微电子正在兴起的系统集成技术(SOC)相结合,形成单一系统芯片,适应并促进我国无线通讯设备的改进,如图4所示。

这是新的计算机结构,克服了传统计算机的冯%26;#183;诺曼瓶颈,结构中固有的并行处理能力,使其具有非常好的性能。微电子技术的发展、芯片集成度的提高,为此结构计算机的实现提供了可能。因此研究这种计算机结构,对计算机科学的发展是有价值的。

现在,软件无线电的研究在我国正不断深入。其目标之一是将不同制式、不同频段的信号利用单一器件进行接收和发送,并且越早地将射频信号变为数字信号进行处理越好。这一方面促进了智能天线和软件接口协议的研究,另一方面也要求有高速低功耗、功能可变的硬件相配合。现阶段国内应用的硬件主要是DSP和计算机,它们在功耗和速度方面都不及粗粒度可配置计算。粗粒度可配置计算结构,通过处理单元的配置、数据路径的配置,使数据在流动中完成运算。在接近ASIC(专用集成电路)性能的同时,又具有一定的灵活性。应用可配置计算系统,既可以更早地将模拟信号转变为数字信号进行处理,利于系统性能的提高,又可以进一步将其包装为IP(知识产权)核,与目前微电子正在兴起的系统集成技术(SOC)相结合,形成单一系统芯片,适应并促进我国无线通讯设备的改进,如图4所示。

这是新的计算机结构,克服了传统计算机的冯%26;#183;诺曼瓶颈,结构中固有的并行处理能力,使其具有非常好的性能。微电子技术的发展、芯片集成度的提高,为此结构计算机的实现提供了可能。因此研究这种计算机结构,对计算机科学的发展是有价值的。

引用地址:粗粒度可配置计算结构的研究与发展

1 粗粒度可配置结构的数据处理

在可重配置计算中,一般提供了配置过程和计算过程。根据计算任务的不同,首先对处理单元和连接网络进行相应的配置,之后再对数据流进行计算。图2是传统的处理器与粗粒度可重配置结构数据处理流程的比较。从图2中可以看到,冯%26;#183;诺曼类型的指令流被配置流和数据流所代替。粗粒度可配置计算结构将软件的灵活与硬件的高速结合在一起,从崭新的角度设计数字信号处理器。与传统的处理器相比,具有以下特点:

(1)传统数据处理的指令流被配置流所代替,不再是单个指令的乘加或移位运算,而是不同功能如滤波、FFT、矩阵相乘等的顺序执行。

(2)各单元功能可以配置,与传统的处理器指令不同,设计全新的配置指令。通过配置为不同功能单元的组合,完成相应的功能。由于是用硬件实现各功能,功耗低。

1 粗粒度可配置结构的数据处理

在可重配置计算中,一般提供了配置过程和计算过程。根据计算任务的不同,首先对处理单元和连接网络进行相应的配置,之后再对数据流进行计算。图2是传统的处理器与粗粒度可重配置结构数据处理流程的比较。从图2中可以看到,冯%26;#183;诺曼类型的指令流被配置流和数据流所代替。粗粒度可配置计算结构将软件的灵活与硬件的高速结合在一起,从崭新的角度设计数字信号处理器。与传统的处理器相比,具有以下特点:

(1)传统数据处理的指令流被配置流所代替,不再是单个指令的乘加或移位运算,而是不同功能如滤波、FFT、矩阵相乘等的顺序执行。

(2)各单元功能可以配置,与传统的处理器指令不同,设计全新的配置指令。通过配置为不同功能单元的组合,完成相应的功能。由于是用硬件实现各功能,功耗低。

(3)不存在传统处理器从RAM中读取指令问题,且结构中有多个RAM区和I/O可用,可有效解决冯%26;#183;诺曼瓶颈,加快数据处理速度。

(4)多个单元的网络结构,链路可配,具有极强的并行处理能力。将编译之后的算子网表与实际结构中的处理单元一一对应的过程是映射与路径寻优的过程,主要指map(映射)、place(放置)、route(路由)三步。涉及的优化算法主要有:模拟退火算法、遗传算法、谈判拥塞算法等。

2 发现现状

粗粒度重配置计算最早见于20世纪60年代,是Gerald Estrin教授提出的“固定加可变结构计算机”,但因为受当时芯片制造水平的限制,只是一个概念而已。进入90年代,随着VLSI(超大规模集成电路)技术的发展,以“可编程开关(programswitch)”为基础的粗粒度可配置计算结构不断被开发出来,并在图像滤波、特征提取、目标识别与跟踪、通讯算法等方面展示出了非凡的性能与潜力。表1列出的是国外部分粗粒度计算项目,国内此项研究尚未见报道。在商业应用中,做得比较好的是PACT极端并行处理公司,其包含64个PE的XPP64A1在主频200MHz时MAC(乘加)运算已经达到了12.8GigaMACs/秒。

(3)不存在传统处理器从RAM中读取指令问题,且结构中有多个RAM区和I/O可用,可有效解决冯%26;#183;诺曼瓶颈,加快数据处理速度。

(4)多个单元的网络结构,链路可配,具有极强的并行处理能力。将编译之后的算子网表与实际结构中的处理单元一一对应的过程是映射与路径寻优的过程,主要指map(映射)、place(放置)、route(路由)三步。涉及的优化算法主要有:模拟退火算法、遗传算法、谈判拥塞算法等。

2 发现现状

粗粒度重配置计算最早见于20世纪60年代,是Gerald Estrin教授提出的“固定加可变结构计算机”,但因为受当时芯片制造水平的限制,只是一个概念而已。进入90年代,随着VLSI(超大规模集成电路)技术的发展,以“可编程开关(programswitch)”为基础的粗粒度可配置计算结构不断被开发出来,并在图像滤波、特征提取、目标识别与跟踪、通讯算法等方面展示出了非凡的性能与潜力。表1列出的是国外部分粗粒度计算项目,国内此项研究尚未见报道。在商业应用中,做得比较好的是PACT极端并行处理公司,其包含64个PE的XPP64A1在主频200MHz时MAC(乘加)运算已经达到了12.8GigaMACs/秒。

从表1可以发现,现有粗粒度可重配置计算都有其相应的应用领域,没有形成一个统一固定的模式,系统结构、组织方式、粒度大小及编译环境各不相同。开发高效通用的粗粒度计算结构仍有一定的难度,这也是可配置计算结构的重要研究方向。

表1 粗粒度结构技术总结

项目名称

结构

粒度

组织

映射方法

应用目标

PADDI

交叉条

16位

中央交叉条

选通

DSP

DFFC

3维阵列

8,16位

直接与可配连接

协同编译

图像处理

PADDI-2

交叉条

16位

多交叉条

选通

DSP

DP-FPGA

2维阵列

1%26;amp;4位,多粒度

不均一布线通道

天关箱选通

规则路径

KressArray

2维阵列

可选路径宽度

NN%26;amp;总线分段

协同编译

自适应

Colt

2维阵列

1%26;amp;16位,不均一

实时配置

高动态可配

RaPID

1维阵列

16位

可分段总线

通道选通

流水线

ACM

2维阵列

32位,多粒度

矩阵连接

协同编译

普通

Lirmm

环形

16位

主次数据流

协同编译

运动估计等

Matrix

2维网格

8位,多粒度

8NN,全局线

多级长度

普通

RAW

2维网格

8位,多粒度

8NN,开关连接

开关箱选通

普通

Pleiades

网格/交叉条

多粒度

可分段的交叉条

开关箱选通

多媒体

PipeRench

1维阵列

128位

调度

流水线

REMARC

2维阵列

16位

NN,全长度总线

多媒体

MorphoSys

2维网格

16位

NN,长度2%26;amp;3线段

手动Place%26;amp;route

CHESS

六角形网格

4位,多粒度

8NN,总线

JHDL编译

多媒体

DreAM

2维阵列

8%26;amp;16位

NN,分段总线

协同编译

下一代无线

CS2000

2维阵列

16%26;amp;32位

不均一阵列

协同编译

通讯

XPP64A1

2维阵列

24位

NN,分段配置总线

协同编译

图像处理

3 未来的发展

粗粒度可配置计算将软件的灵活与硬件的高效、低功耗结合在一起,利用硬件来实现软件算法。虽然灵活性上要比DSP和计算机差一些,但计算效率和处理能力上却有很大的提高。图3是数字信号处理领域目前各类器件性能的简单比较。

此结构芯片非常适合图像数据处理,同时另一应用方面——软件无线电的硬件平台,也正促进其发展。

从表1可以发现,现有粗粒度可重配置计算都有其相应的应用领域,没有形成一个统一固定的模式,系统结构、组织方式、粒度大小及编译环境各不相同。开发高效通用的粗粒度计算结构仍有一定的难度,这也是可配置计算结构的重要研究方向。

表1 粗粒度结构技术总结

项目名称

结构

粒度

组织

映射方法

应用目标

PADDI

交叉条

16位

中央交叉条

选通

DSP

DFFC

3维阵列

8,16位

直接与可配连接

协同编译

图像处理

PADDI-2

交叉条

16位

多交叉条

选通

DSP

DP-FPGA

2维阵列

1%26;amp;4位,多粒度

不均一布线通道

天关箱选通

规则路径

KressArray

2维阵列

可选路径宽度

NN%26;amp;总线分段

协同编译

自适应

Colt

2维阵列

1%26;amp;16位,不均一

实时配置

高动态可配

RaPID

1维阵列

16位

可分段总线

通道选通

流水线

ACM

2维阵列

32位,多粒度

矩阵连接

协同编译

普通

Lirmm

环形

16位

主次数据流

协同编译

运动估计等

Matrix

2维网格

8位,多粒度

8NN,全局线

多级长度

普通

RAW

2维网格

8位,多粒度

8NN,开关连接

开关箱选通

普通

Pleiades

网格/交叉条

多粒度

可分段的交叉条

开关箱选通

多媒体

PipeRench

1维阵列

128位

调度

流水线

REMARC

2维阵列

16位

NN,全长度总线

多媒体

MorphoSys

2维网格

16位

NN,长度2%26;amp;3线段

手动Place%26;amp;route

CHESS

六角形网格

4位,多粒度

8NN,总线

JHDL编译

多媒体

DreAM

2维阵列

8%26;amp;16位

NN,分段总线

协同编译

下一代无线

CS2000

2维阵列

16%26;amp;32位

不均一阵列

协同编译

通讯

XPP64A1

2维阵列

24位

NN,分段配置总线

协同编译

图像处理

3 未来的发展

粗粒度可配置计算将软件的灵活与硬件的高效、低功耗结合在一起,利用硬件来实现软件算法。虽然灵活性上要比DSP和计算机差一些,但计算效率和处理能力上却有很大的提高。图3是数字信号处理领域目前各类器件性能的简单比较。

此结构芯片非常适合图像数据处理,同时另一应用方面——软件无线电的硬件平台,也正促进其发展。

现在,软件无线电的研究在我国正不断深入。其目标之一是将不同制式、不同频段的信号利用单一器件进行接收和发送,并且越早地将射频信号变为数字信号进行处理越好。这一方面促进了智能天线和软件接口协议的研究,另一方面也要求有高速低功耗、功能可变的硬件相配合。现阶段国内应用的硬件主要是DSP和计算机,它们在功耗和速度方面都不及粗粒度可配置计算。粗粒度可配置计算结构,通过处理单元的配置、数据路径的配置,使数据在流动中完成运算。在接近ASIC(专用集成电路)性能的同时,又具有一定的灵活性。应用可配置计算系统,既可以更早地将模拟信号转变为数字信号进行处理,利于系统性能的提高,又可以进一步将其包装为IP(知识产权)核,与目前微电子正在兴起的系统集成技术(SOC)相结合,形成单一系统芯片,适应并促进我国无线通讯设备的改进,如图4所示。

这是新的计算机结构,克服了传统计算机的冯%26;#183;诺曼瓶颈,结构中固有的并行处理能力,使其具有非常好的性能。微电子技术的发展、芯片集成度的提高,为此结构计算机的实现提供了可能。因此研究这种计算机结构,对计算机科学的发展是有价值的。

现在,软件无线电的研究在我国正不断深入。其目标之一是将不同制式、不同频段的信号利用单一器件进行接收和发送,并且越早地将射频信号变为数字信号进行处理越好。这一方面促进了智能天线和软件接口协议的研究,另一方面也要求有高速低功耗、功能可变的硬件相配合。现阶段国内应用的硬件主要是DSP和计算机,它们在功耗和速度方面都不及粗粒度可配置计算。粗粒度可配置计算结构,通过处理单元的配置、数据路径的配置,使数据在流动中完成运算。在接近ASIC(专用集成电路)性能的同时,又具有一定的灵活性。应用可配置计算系统,既可以更早地将模拟信号转变为数字信号进行处理,利于系统性能的提高,又可以进一步将其包装为IP(知识产权)核,与目前微电子正在兴起的系统集成技术(SOC)相结合,形成单一系统芯片,适应并促进我国无线通讯设备的改进,如图4所示。

这是新的计算机结构,克服了传统计算机的冯%26;#183;诺曼瓶颈,结构中固有的并行处理能力,使其具有非常好的性能。微电子技术的发展、芯片集成度的提高,为此结构计算机的实现提供了可能。因此研究这种计算机结构,对计算机科学的发展是有价值的。

嵌入式网络那些事:LwIP协议深度剖析与实战演练

嵌入式网络那些事:LwIP协议深度剖析与实战演练 INA126E-2500

INA126E-2500

京公网安备 11010802033920号

京公网安备 11010802033920号