摘要: 本文介绍了MVB总线帧结构,并完成了用于网络连接的MVB总线访问IP核的设计。基于SOPC的设计思想,本文通过Quarters II软件平台的SOPC Builder设计工具,集成NiosII软核处理器与总线访问IP核,实现了满足MVB协议的I类网卡设计。

关键词: 列车通信网络(TCN);MVB;总线访问IP核(BAP);SOPC;NiosII

国内外车载网络技术的发展是随着现场总线网络技术的发展而发展起来的,先后产生了RS485、Lonworks、WorldFIP等多种总线网络形式。1999年,国际电工委员会(IEC)颁布了IEC-61375标准,该标准中将车载网络分为两级总线的层次结构,即用于连接各节可动态编组的车辆间的绞线式列车总线WTB(Wire Train Bus)和用于连接车辆(或固定编组的车辆单元)内部各种设备的多功能车辆总线MVB(Multifunction Vehicle Bus),它们之间的列车总线节点起着网关的作用,其中MVB网络由于较低的要求和其易用性高的特点,在实际中运用很广泛。本文通过深入研究几种列车通信网络产品底层协议,特别是TCN 的底层协议及关键技术,基于SOPC的设计思想,设计出符合IEC-61375 标准的MVB总线访问IP(Intellectual Property)内核和网卡。

[b]系统体系结构

[/b]

本设计正是基于SOPC的思想,开发实现自主知识产权的MVB收发控制器IP核,借助于Quarters II开发工具,集成至Altera FPGA器件内部,构建SOC片上系统实现MVB网卡基本功能,相比传统国外的MVB网卡,大大简化了系统的结构,降低了开发难度。

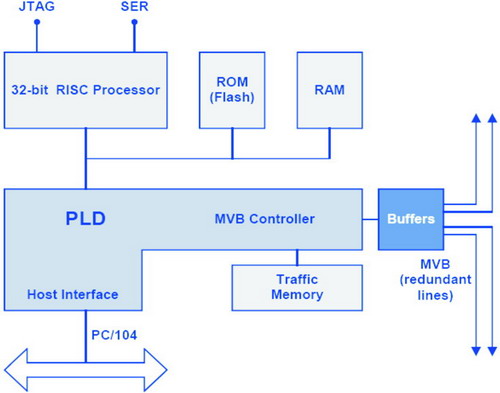

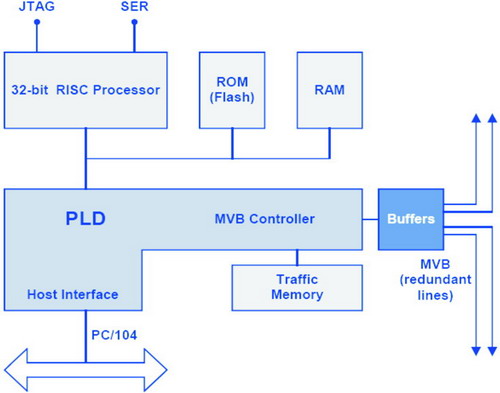

传统MVB网卡的硬件结构比较复杂,设计实现上有较大的难度。如图1所示,是Duagon公司的一款典型的MVB网卡d113的硬件结构。其硬件主要有以下几个部分构成:中央控制器采用高性能的32位ARM处理器,存储系统由非易失性程序存储器(ROM)Flash,以及数据存储器RAM组成,可编程器件上实现MVB收发器以及外部PC/104总线接口。

图1 d113硬件框图

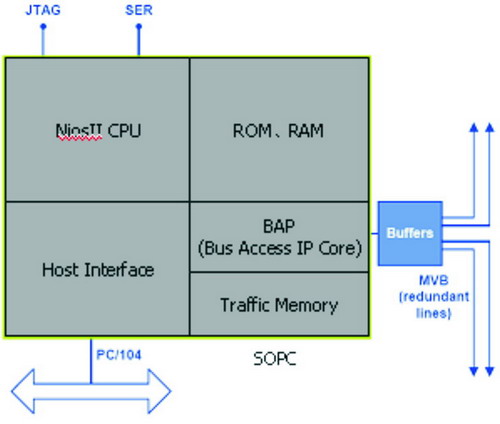

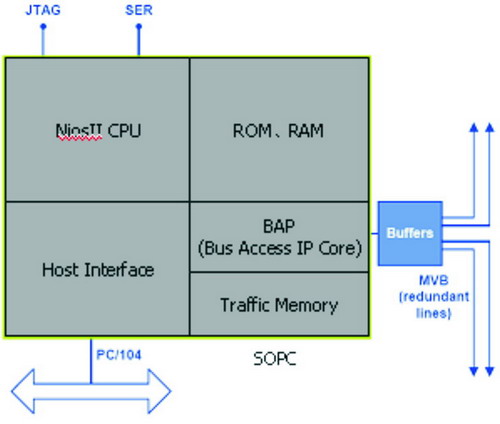

本设计在一片FPGA上,采用SOPC技术实现的MVB网卡:由Altera 公司提供的32位高性能软核处理器NiosII取代ARM处理器,ROM,RAM及Traffic Memory均可以在FPGA片内由SOPC Builder工具实现,再集成MVB总线访问IP核便可以构成MVB网卡,实现了真正的片上系统。其硬件框图如图2所示。

图1 d113硬件框图

本设计在一片FPGA上,采用SOPC技术实现的MVB网卡:由Altera 公司提供的32位高性能软核处理器NiosII取代ARM处理器,ROM,RAM及Traffic Memory均可以在FPGA片内由SOPC Builder工具实现,再集成MVB总线访问IP核便可以构成MVB网卡,实现了真正的片上系统。其硬件框图如图2所示。

图2 网卡结构框图

总线访问IP核的实现

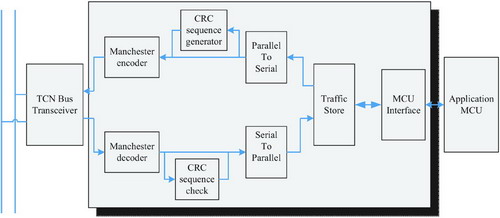

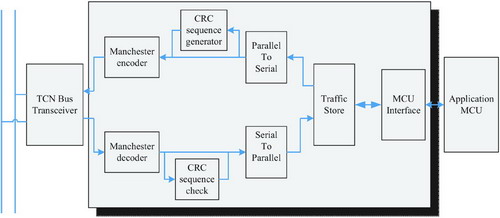

总线访问IP 核是实现WTB和MVB的总线访问处理器(BAP)的核心内容。由此IP 核结合物理层的总线收发器完成总线访问。总线访问IP核可分为物理层、数据链路层与应用层的接口三大部分。1)在物理层实现基带曼彻斯特Biphase-L编解码,介质冗余处理,介质安装单元接口;用于输入解码的数字锁相环的设计。2)链路层包括寻址方式,F-code(功能代码)的生成,主从设备帧内容的填充,介质访问控制(MAC)等。3)与应用层的接口通常采用共享存储器的方法,需要完成端口的定义与维护,通信存储器的控制等。其逻辑框图如图3。

图2 网卡结构框图

总线访问IP核的实现

总线访问IP 核是实现WTB和MVB的总线访问处理器(BAP)的核心内容。由此IP 核结合物理层的总线收发器完成总线访问。总线访问IP核可分为物理层、数据链路层与应用层的接口三大部分。1)在物理层实现基带曼彻斯特Biphase-L编解码,介质冗余处理,介质安装单元接口;用于输入解码的数字锁相环的设计。2)链路层包括寻址方式,F-code(功能代码)的生成,主从设备帧内容的填充,介质访问控制(MAC)等。3)与应用层的接口通常采用共享存储器的方法,需要完成端口的定义与维护,通信存储器的控制等。其逻辑框图如图3。

图3 网卡结构框图

MVB帧结构

在MVB中有两种帧格式,一种是只能由总线主设备发送的主设备帧,简称主帧,一种是为响应主帧而由从设备发送的从设备帧,简称从帧。 一个帧以9位定界符开始,主设备帧分界符和从设备帧分界符对防止同步失败是不相同的。

MVB编码器

MVB总线数据以帧为基本单位,数据帧采用了曼彻斯特码传输,编码和解码器不只是进行曼彻斯特编解码,帧头帧尾的特殊编解码也需要在这里进行,采用传统的曼彻斯特编解码器将无法完成此项工作。在本设计中,采用了结合收发器的状态机具体状态进行编解码的设计方法解决这一问题。MVB帧发送器通过控制逻辑模块调用曼彻斯特编码与CRC校验模块、通信存储单元模块完成缓冲区数据的发送。

MVB帧接收器

接收器实现的关键是有效数据帧的识别,实现思路类似于发送器,根据编码校验可以实现。另一个问题是与总线的接口方式,该设计采用了8位并行数据宽度输出,加序号标识的方法可以接收任意给定长度的有效数据。

数据校验

帧数据用一个或更多的8位校验序列来保护,数据的内容应处理成64位的代码字(对小一些的数据用16或32位),不包括起始分界符和终止分界符。这个代码字和随后的校验序列应作为最高有效的数据位首先发送。

校验序列按被其保护的16,32或64位数据的循环冗余校验(CRC)计算。校验序列按多项式计算,7位运算结果用一个偶校验位进行扩展。所有的8位数据取反发送。

通信存储单元模块

通信存储器(Traffic Store)作为MVB标准中的一个重要实现手段,是MVB接口网卡中的重要组成部分。通信存储器容量的大小依据具体应用而定。在MVB网络中通常所需要的通信存储器容量为32或64个端口即可,每个端口需要占用的空间最大为256位,这样通信存储器所需要的空间为8kbits或16kbits。开辟FPGA中的DRAM作为通信存储单元,完成数据交互功能。用来存储经由MVB总线传输的数据,是控制逻辑模块与编码校验单元之间的共享单元。控制逻辑模块依据通信存储模块端口地址的起始地址,以及其数据长度,来读取相应的过程数据和消息数据等。

Avolon总线接口设计

MVB总线处理IP核与NiosII的接口设计的实现是通过Traffic Store(共享RAM)来实现的。使用Quarters Ⅱ中的MegaWizard plug-in Manager工具来产生一个双口RAM模块,其设置如表1所示。

该通信存储器与Nios II处理器通过Avalon总线接口。

SOPC片上系统MVB网卡的实现

总线访问IP核与Nios II的系统集成

利用Quarters II的SOPC Builder工具我们集成了NiosII 软核处理器、4k的片内RAM、MVB总线访问IP核(包括编码器和解码器)以及LCD控制模块,构成了一个能实现MVB一类网卡功能的片上系统。

软件设计

基于以上所述的SOPC系统,我们设计了一个基本的MVB节点以实现过程数据传输。本节点将0x14地址设置为源端口,当主帧轮询0x14地址时,本节点将此端口里的数据打包成从帧发送到总线上面,以刷新0x14地址的宿端口。

altera_avalon_mvb.h的设计,包括总线访问IP核寄存器读写的宏定义。

#define IORD_ALTERA_AVALON_ MVB_SENDREG(base) IORD(base, 0)

#define IOWR_ALTERA_AVALON_ MVB_SENDREG(base, data) IOWR(base, 0, data)

在主函数里置MVB总线接收允许位,循环等待接收MVB主控制器发过来的主帧。节点在接收到主帧之后,程序进入中断处理程序。在中断程序里提取接收到的主帧里的端口地址,并与自身预设的端口地址码进行比较,如果地址码相符,则节点将本端口的数据通过MVB发送器发到总线上,实现端口数据刷新操作。

[b]仿真及实现

[/b]

仿真波形

在本实验中,对实验室设计的MVB板卡进行了功能仿真和FPGA验证,通过对过程数据的发送与接收验证了所搭建的MVB系统。

实测波形

在编好程序后,再编译一遍QuartersII工程文件,将得到的.pof文件下载至FPGA内,上电后用示波器测输出管脚,便可观察到MVB帧波形。对照IEC-61375协议标准,可以判断出该波形为符合标准的正确波形,并且源端口节点上收到了正确的数据,从而证明该过程数据端口的成功刷新。

结语

目前国内的列车网络及控制技术是在技术引进的基础上发展起来的,国外厂商只愿提供产品而不转让关键技术。由于难以单独购买网络专用芯片等种种原因,目前仍是直接采用国外产品,或用国外(设计)的网卡(万元以上的高价)等进行系统集成,以此构成列车通信网络(即国产化)。本论文围绕MVB总线底层协议展开研究,基于SOPC设计思想,对利用FPGA实现IEC61375协议进行了尝试,初步完成了MVB网络I类板卡的设计。目前,对该网络协议的实现方面还仅限于初期阶段,只实现了MVB总线基本的过程数据的收发。该系统的后续还需加入消息监督数据等的通信。在实际的节点应用中,也可能出现各种各样的问题需要加以改进。

参考文献:

1. IEC61375-1-1999, Part 1:“Train Communication Network”

2. zur Bonsen, The Multifunction Vehicle Bus (MVB), Factory Communication Systems, 1995

3. Jaime Jim%26;#233;nez, Jos%26;#233; L.Martin, Carlos Cuadrado, Jagoba Arias and Jes%26;#250;s L%26;#225;zaro, “A Top-down Design for the Train Communication Network”,2003 IEEE

4. Alberto Chavarr%26;#237;a, Joseba L%26;#243;pez de Arroyabe, Aitzol Zuloaga, " Slave node architecture for train communications networks" , 2000 IEEE

5. 张大波、王建,《MVB总线实时协议实现及其实验研究》

6. 侯宁,丁荣军,王永翔,王立德,《MVB网卡的帧收发器设计》

图3 网卡结构框图

MVB帧结构

在MVB中有两种帧格式,一种是只能由总线主设备发送的主设备帧,简称主帧,一种是为响应主帧而由从设备发送的从设备帧,简称从帧。 一个帧以9位定界符开始,主设备帧分界符和从设备帧分界符对防止同步失败是不相同的。

MVB编码器

MVB总线数据以帧为基本单位,数据帧采用了曼彻斯特码传输,编码和解码器不只是进行曼彻斯特编解码,帧头帧尾的特殊编解码也需要在这里进行,采用传统的曼彻斯特编解码器将无法完成此项工作。在本设计中,采用了结合收发器的状态机具体状态进行编解码的设计方法解决这一问题。MVB帧发送器通过控制逻辑模块调用曼彻斯特编码与CRC校验模块、通信存储单元模块完成缓冲区数据的发送。

MVB帧接收器

接收器实现的关键是有效数据帧的识别,实现思路类似于发送器,根据编码校验可以实现。另一个问题是与总线的接口方式,该设计采用了8位并行数据宽度输出,加序号标识的方法可以接收任意给定长度的有效数据。

数据校验

帧数据用一个或更多的8位校验序列来保护,数据的内容应处理成64位的代码字(对小一些的数据用16或32位),不包括起始分界符和终止分界符。这个代码字和随后的校验序列应作为最高有效的数据位首先发送。

校验序列按被其保护的16,32或64位数据的循环冗余校验(CRC)计算。校验序列按多项式计算,7位运算结果用一个偶校验位进行扩展。所有的8位数据取反发送。

通信存储单元模块

通信存储器(Traffic Store)作为MVB标准中的一个重要实现手段,是MVB接口网卡中的重要组成部分。通信存储器容量的大小依据具体应用而定。在MVB网络中通常所需要的通信存储器容量为32或64个端口即可,每个端口需要占用的空间最大为256位,这样通信存储器所需要的空间为8kbits或16kbits。开辟FPGA中的DRAM作为通信存储单元,完成数据交互功能。用来存储经由MVB总线传输的数据,是控制逻辑模块与编码校验单元之间的共享单元。控制逻辑模块依据通信存储模块端口地址的起始地址,以及其数据长度,来读取相应的过程数据和消息数据等。

Avolon总线接口设计

MVB总线处理IP核与NiosII的接口设计的实现是通过Traffic Store(共享RAM)来实现的。使用Quarters Ⅱ中的MegaWizard plug-in Manager工具来产生一个双口RAM模块,其设置如表1所示。

该通信存储器与Nios II处理器通过Avalon总线接口。

SOPC片上系统MVB网卡的实现

总线访问IP核与Nios II的系统集成

利用Quarters II的SOPC Builder工具我们集成了NiosII 软核处理器、4k的片内RAM、MVB总线访问IP核(包括编码器和解码器)以及LCD控制模块,构成了一个能实现MVB一类网卡功能的片上系统。

软件设计

基于以上所述的SOPC系统,我们设计了一个基本的MVB节点以实现过程数据传输。本节点将0x14地址设置为源端口,当主帧轮询0x14地址时,本节点将此端口里的数据打包成从帧发送到总线上面,以刷新0x14地址的宿端口。

altera_avalon_mvb.h的设计,包括总线访问IP核寄存器读写的宏定义。

#define IORD_ALTERA_AVALON_ MVB_SENDREG(base) IORD(base, 0)

#define IOWR_ALTERA_AVALON_ MVB_SENDREG(base, data) IOWR(base, 0, data)

在主函数里置MVB总线接收允许位,循环等待接收MVB主控制器发过来的主帧。节点在接收到主帧之后,程序进入中断处理程序。在中断程序里提取接收到的主帧里的端口地址,并与自身预设的端口地址码进行比较,如果地址码相符,则节点将本端口的数据通过MVB发送器发到总线上,实现端口数据刷新操作。

[b]仿真及实现

[/b]

仿真波形

在本实验中,对实验室设计的MVB板卡进行了功能仿真和FPGA验证,通过对过程数据的发送与接收验证了所搭建的MVB系统。

实测波形

在编好程序后,再编译一遍QuartersII工程文件,将得到的.pof文件下载至FPGA内,上电后用示波器测输出管脚,便可观察到MVB帧波形。对照IEC-61375协议标准,可以判断出该波形为符合标准的正确波形,并且源端口节点上收到了正确的数据,从而证明该过程数据端口的成功刷新。

结语

目前国内的列车网络及控制技术是在技术引进的基础上发展起来的,国外厂商只愿提供产品而不转让关键技术。由于难以单独购买网络专用芯片等种种原因,目前仍是直接采用国外产品,或用国外(设计)的网卡(万元以上的高价)等进行系统集成,以此构成列车通信网络(即国产化)。本论文围绕MVB总线底层协议展开研究,基于SOPC设计思想,对利用FPGA实现IEC61375协议进行了尝试,初步完成了MVB网络I类板卡的设计。目前,对该网络协议的实现方面还仅限于初期阶段,只实现了MVB总线基本的过程数据的收发。该系统的后续还需加入消息监督数据等的通信。在实际的节点应用中,也可能出现各种各样的问题需要加以改进。

参考文献:

1. IEC61375-1-1999, Part 1:“Train Communication Network”

2. zur Bonsen, The Multifunction Vehicle Bus (MVB), Factory Communication Systems, 1995

3. Jaime Jim%26;#233;nez, Jos%26;#233; L.Martin, Carlos Cuadrado, Jagoba Arias and Jes%26;#250;s L%26;#225;zaro, “A Top-down Design for the Train Communication Network”,2003 IEEE

4. Alberto Chavarr%26;#237;a, Joseba L%26;#243;pez de Arroyabe, Aitzol Zuloaga, " Slave node architecture for train communications networks" , 2000 IEEE

5. 张大波、王建,《MVB总线实时协议实现及其实验研究》

6. 侯宁,丁荣军,王永翔,王立德,《MVB网卡的帧收发器设计》

引用地址:基于SOPC的列车通信网卡的设计

图1 d113硬件框图

本设计在一片FPGA上,采用SOPC技术实现的MVB网卡:由Altera 公司提供的32位高性能软核处理器NiosII取代ARM处理器,ROM,RAM及Traffic Memory均可以在FPGA片内由SOPC Builder工具实现,再集成MVB总线访问IP核便可以构成MVB网卡,实现了真正的片上系统。其硬件框图如图2所示。

图1 d113硬件框图

本设计在一片FPGA上,采用SOPC技术实现的MVB网卡:由Altera 公司提供的32位高性能软核处理器NiosII取代ARM处理器,ROM,RAM及Traffic Memory均可以在FPGA片内由SOPC Builder工具实现,再集成MVB总线访问IP核便可以构成MVB网卡,实现了真正的片上系统。其硬件框图如图2所示。

图2 网卡结构框图

总线访问IP核的实现

总线访问IP 核是实现WTB和MVB的总线访问处理器(BAP)的核心内容。由此IP 核结合物理层的总线收发器完成总线访问。总线访问IP核可分为物理层、数据链路层与应用层的接口三大部分。1)在物理层实现基带曼彻斯特Biphase-L编解码,介质冗余处理,介质安装单元接口;用于输入解码的数字锁相环的设计。2)链路层包括寻址方式,F-code(功能代码)的生成,主从设备帧内容的填充,介质访问控制(MAC)等。3)与应用层的接口通常采用共享存储器的方法,需要完成端口的定义与维护,通信存储器的控制等。其逻辑框图如图3。

图2 网卡结构框图

总线访问IP核的实现

总线访问IP 核是实现WTB和MVB的总线访问处理器(BAP)的核心内容。由此IP 核结合物理层的总线收发器完成总线访问。总线访问IP核可分为物理层、数据链路层与应用层的接口三大部分。1)在物理层实现基带曼彻斯特Biphase-L编解码,介质冗余处理,介质安装单元接口;用于输入解码的数字锁相环的设计。2)链路层包括寻址方式,F-code(功能代码)的生成,主从设备帧内容的填充,介质访问控制(MAC)等。3)与应用层的接口通常采用共享存储器的方法,需要完成端口的定义与维护,通信存储器的控制等。其逻辑框图如图3。

图3 网卡结构框图

MVB帧结构

在MVB中有两种帧格式,一种是只能由总线主设备发送的主设备帧,简称主帧,一种是为响应主帧而由从设备发送的从设备帧,简称从帧。 一个帧以9位定界符开始,主设备帧分界符和从设备帧分界符对防止同步失败是不相同的。

MVB编码器

MVB总线数据以帧为基本单位,数据帧采用了曼彻斯特码传输,编码和解码器不只是进行曼彻斯特编解码,帧头帧尾的特殊编解码也需要在这里进行,采用传统的曼彻斯特编解码器将无法完成此项工作。在本设计中,采用了结合收发器的状态机具体状态进行编解码的设计方法解决这一问题。MVB帧发送器通过控制逻辑模块调用曼彻斯特编码与CRC校验模块、通信存储单元模块完成缓冲区数据的发送。

MVB帧接收器

接收器实现的关键是有效数据帧的识别,实现思路类似于发送器,根据编码校验可以实现。另一个问题是与总线的接口方式,该设计采用了8位并行数据宽度输出,加序号标识的方法可以接收任意给定长度的有效数据。

数据校验

帧数据用一个或更多的8位校验序列来保护,数据的内容应处理成64位的代码字(对小一些的数据用16或32位),不包括起始分界符和终止分界符。这个代码字和随后的校验序列应作为最高有效的数据位首先发送。

校验序列按被其保护的16,32或64位数据的循环冗余校验(CRC)计算。校验序列按多项式计算,7位运算结果用一个偶校验位进行扩展。所有的8位数据取反发送。

通信存储单元模块

通信存储器(Traffic Store)作为MVB标准中的一个重要实现手段,是MVB接口网卡中的重要组成部分。通信存储器容量的大小依据具体应用而定。在MVB网络中通常所需要的通信存储器容量为32或64个端口即可,每个端口需要占用的空间最大为256位,这样通信存储器所需要的空间为8kbits或16kbits。开辟FPGA中的DRAM作为通信存储单元,完成数据交互功能。用来存储经由MVB总线传输的数据,是控制逻辑模块与编码校验单元之间的共享单元。控制逻辑模块依据通信存储模块端口地址的起始地址,以及其数据长度,来读取相应的过程数据和消息数据等。

Avolon总线接口设计

MVB总线处理IP核与NiosII的接口设计的实现是通过Traffic Store(共享RAM)来实现的。使用Quarters Ⅱ中的MegaWizard plug-in Manager工具来产生一个双口RAM模块,其设置如表1所示。

该通信存储器与Nios II处理器通过Avalon总线接口。

SOPC片上系统MVB网卡的实现

总线访问IP核与Nios II的系统集成

利用Quarters II的SOPC Builder工具我们集成了NiosII 软核处理器、4k的片内RAM、MVB总线访问IP核(包括编码器和解码器)以及LCD控制模块,构成了一个能实现MVB一类网卡功能的片上系统。

软件设计

基于以上所述的SOPC系统,我们设计了一个基本的MVB节点以实现过程数据传输。本节点将0x14地址设置为源端口,当主帧轮询0x14地址时,本节点将此端口里的数据打包成从帧发送到总线上面,以刷新0x14地址的宿端口。

altera_avalon_mvb.h的设计,包括总线访问IP核寄存器读写的宏定义。

#define IORD_ALTERA_AVALON_ MVB_SENDREG(base) IORD(base, 0)

#define IOWR_ALTERA_AVALON_ MVB_SENDREG(base, data) IOWR(base, 0, data)

在主函数里置MVB总线接收允许位,循环等待接收MVB主控制器发过来的主帧。节点在接收到主帧之后,程序进入中断处理程序。在中断程序里提取接收到的主帧里的端口地址,并与自身预设的端口地址码进行比较,如果地址码相符,则节点将本端口的数据通过MVB发送器发到总线上,实现端口数据刷新操作。

[b]仿真及实现

[/b]

仿真波形

在本实验中,对实验室设计的MVB板卡进行了功能仿真和FPGA验证,通过对过程数据的发送与接收验证了所搭建的MVB系统。

实测波形

在编好程序后,再编译一遍QuartersII工程文件,将得到的.pof文件下载至FPGA内,上电后用示波器测输出管脚,便可观察到MVB帧波形。对照IEC-61375协议标准,可以判断出该波形为符合标准的正确波形,并且源端口节点上收到了正确的数据,从而证明该过程数据端口的成功刷新。

结语

目前国内的列车网络及控制技术是在技术引进的基础上发展起来的,国外厂商只愿提供产品而不转让关键技术。由于难以单独购买网络专用芯片等种种原因,目前仍是直接采用国外产品,或用国外(设计)的网卡(万元以上的高价)等进行系统集成,以此构成列车通信网络(即国产化)。本论文围绕MVB总线底层协议展开研究,基于SOPC设计思想,对利用FPGA实现IEC61375协议进行了尝试,初步完成了MVB网络I类板卡的设计。目前,对该网络协议的实现方面还仅限于初期阶段,只实现了MVB总线基本的过程数据的收发。该系统的后续还需加入消息监督数据等的通信。在实际的节点应用中,也可能出现各种各样的问题需要加以改进。

参考文献:

1. IEC61375-1-1999, Part 1:“Train Communication Network”

2. zur Bonsen, The Multifunction Vehicle Bus (MVB), Factory Communication Systems, 1995

3. Jaime Jim%26;#233;nez, Jos%26;#233; L.Martin, Carlos Cuadrado, Jagoba Arias and Jes%26;#250;s L%26;#225;zaro, “A Top-down Design for the Train Communication Network”,2003 IEEE

4. Alberto Chavarr%26;#237;a, Joseba L%26;#243;pez de Arroyabe, Aitzol Zuloaga, " Slave node architecture for train communications networks" , 2000 IEEE

5. 张大波、王建,《MVB总线实时协议实现及其实验研究》

6. 侯宁,丁荣军,王永翔,王立德,《MVB网卡的帧收发器设计》

图3 网卡结构框图

MVB帧结构

在MVB中有两种帧格式,一种是只能由总线主设备发送的主设备帧,简称主帧,一种是为响应主帧而由从设备发送的从设备帧,简称从帧。 一个帧以9位定界符开始,主设备帧分界符和从设备帧分界符对防止同步失败是不相同的。

MVB编码器

MVB总线数据以帧为基本单位,数据帧采用了曼彻斯特码传输,编码和解码器不只是进行曼彻斯特编解码,帧头帧尾的特殊编解码也需要在这里进行,采用传统的曼彻斯特编解码器将无法完成此项工作。在本设计中,采用了结合收发器的状态机具体状态进行编解码的设计方法解决这一问题。MVB帧发送器通过控制逻辑模块调用曼彻斯特编码与CRC校验模块、通信存储单元模块完成缓冲区数据的发送。

MVB帧接收器

接收器实现的关键是有效数据帧的识别,实现思路类似于发送器,根据编码校验可以实现。另一个问题是与总线的接口方式,该设计采用了8位并行数据宽度输出,加序号标识的方法可以接收任意给定长度的有效数据。

数据校验

帧数据用一个或更多的8位校验序列来保护,数据的内容应处理成64位的代码字(对小一些的数据用16或32位),不包括起始分界符和终止分界符。这个代码字和随后的校验序列应作为最高有效的数据位首先发送。

校验序列按被其保护的16,32或64位数据的循环冗余校验(CRC)计算。校验序列按多项式计算,7位运算结果用一个偶校验位进行扩展。所有的8位数据取反发送。

通信存储单元模块

通信存储器(Traffic Store)作为MVB标准中的一个重要实现手段,是MVB接口网卡中的重要组成部分。通信存储器容量的大小依据具体应用而定。在MVB网络中通常所需要的通信存储器容量为32或64个端口即可,每个端口需要占用的空间最大为256位,这样通信存储器所需要的空间为8kbits或16kbits。开辟FPGA中的DRAM作为通信存储单元,完成数据交互功能。用来存储经由MVB总线传输的数据,是控制逻辑模块与编码校验单元之间的共享单元。控制逻辑模块依据通信存储模块端口地址的起始地址,以及其数据长度,来读取相应的过程数据和消息数据等。

Avolon总线接口设计

MVB总线处理IP核与NiosII的接口设计的实现是通过Traffic Store(共享RAM)来实现的。使用Quarters Ⅱ中的MegaWizard plug-in Manager工具来产生一个双口RAM模块,其设置如表1所示。

该通信存储器与Nios II处理器通过Avalon总线接口。

SOPC片上系统MVB网卡的实现

总线访问IP核与Nios II的系统集成

利用Quarters II的SOPC Builder工具我们集成了NiosII 软核处理器、4k的片内RAM、MVB总线访问IP核(包括编码器和解码器)以及LCD控制模块,构成了一个能实现MVB一类网卡功能的片上系统。

软件设计

基于以上所述的SOPC系统,我们设计了一个基本的MVB节点以实现过程数据传输。本节点将0x14地址设置为源端口,当主帧轮询0x14地址时,本节点将此端口里的数据打包成从帧发送到总线上面,以刷新0x14地址的宿端口。

altera_avalon_mvb.h的设计,包括总线访问IP核寄存器读写的宏定义。

#define IORD_ALTERA_AVALON_ MVB_SENDREG(base) IORD(base, 0)

#define IOWR_ALTERA_AVALON_ MVB_SENDREG(base, data) IOWR(base, 0, data)

在主函数里置MVB总线接收允许位,循环等待接收MVB主控制器发过来的主帧。节点在接收到主帧之后,程序进入中断处理程序。在中断程序里提取接收到的主帧里的端口地址,并与自身预设的端口地址码进行比较,如果地址码相符,则节点将本端口的数据通过MVB发送器发到总线上,实现端口数据刷新操作。

[b]仿真及实现

[/b]

仿真波形

在本实验中,对实验室设计的MVB板卡进行了功能仿真和FPGA验证,通过对过程数据的发送与接收验证了所搭建的MVB系统。

实测波形

在编好程序后,再编译一遍QuartersII工程文件,将得到的.pof文件下载至FPGA内,上电后用示波器测输出管脚,便可观察到MVB帧波形。对照IEC-61375协议标准,可以判断出该波形为符合标准的正确波形,并且源端口节点上收到了正确的数据,从而证明该过程数据端口的成功刷新。

结语

目前国内的列车网络及控制技术是在技术引进的基础上发展起来的,国外厂商只愿提供产品而不转让关键技术。由于难以单独购买网络专用芯片等种种原因,目前仍是直接采用国外产品,或用国外(设计)的网卡(万元以上的高价)等进行系统集成,以此构成列车通信网络(即国产化)。本论文围绕MVB总线底层协议展开研究,基于SOPC设计思想,对利用FPGA实现IEC61375协议进行了尝试,初步完成了MVB网络I类板卡的设计。目前,对该网络协议的实现方面还仅限于初期阶段,只实现了MVB总线基本的过程数据的收发。该系统的后续还需加入消息监督数据等的通信。在实际的节点应用中,也可能出现各种各样的问题需要加以改进。

参考文献:

1. IEC61375-1-1999, Part 1:“Train Communication Network”

2. zur Bonsen, The Multifunction Vehicle Bus (MVB), Factory Communication Systems, 1995

3. Jaime Jim%26;#233;nez, Jos%26;#233; L.Martin, Carlos Cuadrado, Jagoba Arias and Jes%26;#250;s L%26;#225;zaro, “A Top-down Design for the Train Communication Network”,2003 IEEE

4. Alberto Chavarr%26;#237;a, Joseba L%26;#243;pez de Arroyabe, Aitzol Zuloaga, " Slave node architecture for train communications networks" , 2000 IEEE

5. 张大波、王建,《MVB总线实时协议实现及其实验研究》

6. 侯宁,丁荣军,王永翔,王立德,《MVB网卡的帧收发器设计》

上一篇:多USB接口的局域网接入技术的实现

下一篇:基于 DSP 的网络通信程序设计

- 热门资源推荐

- 热门放大器推荐

小广播

热门活动

换一批

更多

最新网络通信文章

- 带硬件同步功能的以太网 PHY 扩大了汽车雷达的覆盖范围

- 芯原推出新一代高性能Vitality架构GPU IP系列 支持DirectX 12和先进的计算能力

- 应对 AI 时代的云工作负载,开发者正加速向 Arm 架构迁移

- NVIDIA 推出高性价比的生成式 AI 超级计算机

- Gartner发布2025年影响基础设施和运营的重要趋势

- 智谱清言英特尔酷睿Ultra专享版发布,离线模型玩转AIPC

- Quobly与意法半导体建立战略合作, 加快量子处理器制造进程,实现大型量子计算解决方

- RTI Connext Drive参展CES 2025,以领先通信框架加速SDV开发

- 黑莓 1.6 亿美元甩卖网络安全业务 Cylance,远低于其 14 亿美元的收购价

更多精选电路图

更多热门文章

更多每日新闻

更多往期活动

厂商技术中心

Verilog HDL数字集成电路设计原理与应用

Verilog HDL数字集成电路设计原理与应用 LM2903ITLEP

LM2903ITLEP

京公网安备 11010802033920号

京公网安备 11010802033920号