嵌入式系统广泛应用在工业测控、智能仪表、智能家庭等很多领域。随着嵌入式系统应用范围的不断扩展及网络应用的日益普及,使得越来越多的嵌入式系统需要网络功能。三星公司S3C2440A是国内应用较多的嵌入式微处理器之一,在S3C2440A应用系统中,目前只支持10/100M的网络接口,有很大的实用价值,既可以拓展S3C2440A的应用领域,也可以给其它嵌入式系统高速接入网络提供一种简单易行的参考。

设计方案

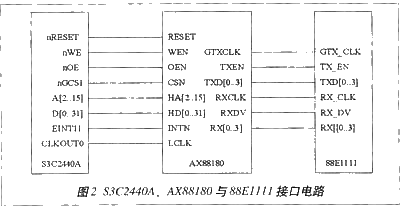

本系统主要由S3C2440A、存储器、AX88180、千兆PHY芯片88E1111、嵌入式Linux、网络驱动程序等组成(见图1)。嵌入式Linux内核负责系统任务的管理并集成TCP/IP协议,方便实现网络功能控制。S3C2440A负责整个系统的控制,它与AX88180以总线方式连接,是通信控制的主体。S3C2440A通过网络驱动程序实现对AX88180内部寄存器编程,实现对以太网数据的发送和接收,从而完成网络与系统之间的数据传输。AX88180与88E1111之间采用RGMII接口方式互连,负责数据传送底层协议的实现。

这里简要介绍一下S3C2440A与AX88180器件,这两个器件是通信控制的主体。

S3C2440A是基于ARM920T核的16/32位RISC微处理器,运行频率高达500MHz,主要面向手持设备以及高性价比、低功耗的应用,适用于开发各类高端手持、小型终端以及网络应用产品,具有非常丰富的片上资源,比如LCD、SDRAM、NAND FLASH、DMA、AD、PWM控制器,以及UART、USB、摄像头、触摸屏、IIC、IIS、SPI、SD、MMC、AC97等接口。

AX88180是台湾亚信公司推出的一款Non-PCI千兆以太网控制芯片,内置1000Mbps以太网媒体存取控制器(MAC);有40KBytes SRAM网络封包缓存器;硬件支持IP/TCP/UDP checksum offloads。它可以十分方便地实现与一般16/32位微处理器连接,可以象SRAM一样被访问。它符合IEEE 802.3/lEEE 802.3u/IEEE 802.3ab协议,适用于串流媒体、多媒体网络、高频宽传输等领域,如数字媒体、家用网关及IP电视等。

硬件设计

由于硬件电路比较复杂,这里只给出核心电路连接,如图2所示。S3C2440A与AX88180之间采用总线方式相连,地址总线A2-A15、数据总线D0-D31、读写信号等可以直接连接,AX88180的40M~100M时钟信号由S3C2440A提供,AX88180中断信号与S3C2440A EINT11相连,整个接口电路无需外加电路;AX88180与PHY芯片之间采用简化的千兆比特媒体独立接口RGMII接口,信号一一对应直接相连即可。

软件设计

从整体角度考虑,Linux网络系统可以分为硬件层、设备驱动层、网络协议层和应用层。在S3C2440A系统上移植有嵌入式Linux、集成TCP/IP等协议栈,应用层的程序可以自己编写也可以移植,这里我们主要分析一下设备驱动程序的实现。

在嵌入式Linux中,整个网络驱动程序的框架可分为四层,分别为协议接口层、网络设备接口层、设备驱动功能层、网络设备和网络媒介层,这个框架在内核网络模块中已经搭建完成,在设计驱动程序的时候,要做的主要工作就是根据上层网络设备接口层定义的device结构和底层具体的硬件特性,来完成设备驱动的功能。驱动程序主要由初始化、打开、关闭、数据接收及发送等函数组成。

初始化函数

初始化函数完成网络设备的初始化,由数据结构device中的init函数指针来调用,加载AX88180驱动模块后,就会调用初始化过程。该首先通过检测物理设备的硬件特征来检测网络物理设备是否存在,之后配置设备所需要的资源,比如中断等。这些过程完成后,就要构造设备设备数据结构,用检测到的数据初始化其相关变量,最后向Linux内核注册设备并申请内存空间。

打开函数

打开函数在网络设备驱动程序中是在网络设备状态由down状态转为up状态时,即被激活的时候被调用,有很多AX88180及88E1111的初始化工作可以放在这里做。在驱动程序作为一个模块被装入时,打开函数还要防止模块卸载时设备处于打开状态。

关闭函数

关闭函数和打开函数做相反的工作,是在设备状态由up转为down时被调用的,作用是释放资源以减少系统负担。在驱动程序作为模块装入时,关闭函数还要减少没备被引用的次数,以便卸载驱动程序。

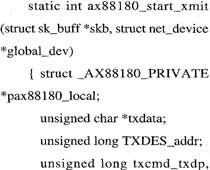

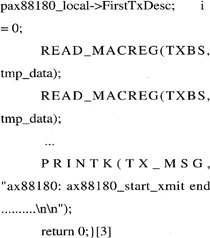

发送函数

发送函数是网络驱动程序的关键过程之一,它与dev->hard_start_xmit连接,在内核通过设备向外发送数据时调用它。系统给AX88180分配一块64K的地址空间,其中8000H-FBFFH作为发送缓冲区地址,在系统调用驱动程序的xmit时,发送的数据放在一个sk_buff结构中,发送到数据缓冲区地址,再由AX88180发送到网络上。如果发送成功,hard_start_xmit释放sk_buff,返回0;如果设备暂时无法处理,则返回1。硬件在发送结束后产生中断。

中断和接收函数

中断和接收函数也是驱动程序的关键过程之一,如果有数据收到,AX88180会产生一个中断通知系统,在中断处理程序中驱动程序申请一块sk_buff(),从AX88180读出数据并放置到接收缓冲区地址0000H~7000H里,然后来填充sk_buff中的一些信息,由skb->dev=dev判断收到帧的协泌类型,填入skb->protocol,再把指针skb->mac.raw指向硬件数据,然后丢弃帧头。之后还要设置skb->pkt_type,标明链路层数据类型,最后调用netif_rX()把数据传送给协议层。

下面是发送函数部分代码:

结语

本文介绍的千兆网络接口在S3C2440A系统中的应用方案已经得以实现,1000 Full-duplex模式下,数据传输速率可以达到200Mbp,在使用FTP下载数据时,速度可以达到4Mbps以上,是使用100M网络接口的5~6倍。如果使用其它更高速度的微处理器,网络接口的速度会更高。

上一篇:ActiveX技术在B/S模式监控系统中的应用

下一篇:基于RTP协议的IP电话QoS监测及提高策略

推荐阅读最新更新时间:2024-05-07 15:59

- 热门资源推荐

- 热门放大器推荐

- Wi-Fi 8规范已在路上:2.4/5/6GHz三频工作

- 治理混合多云环境的三大举措

- Microchip借助NVIDIA Holoscan平台加速实时边缘AI部署

- 是德科技 FieldFox 手持式分析仪配合 VDI 扩频模块,实现毫米波分析功能

- 高通推出其首款 RISC-V 架构可编程连接模组 QCC74xM,支持 Wi-Fi 6 等协议

- Microchip推出广泛的IGBT 7 功率器件组合,专为可持续发展、电动出行和数据中心应用而设计

- 英飞凌推出新型高性能微控制器AURIX™ TC4Dx

- Rambus宣布推出业界首款HBM4控制器IP,加速下一代AI工作负载

- 恩智浦FRDM平台助力无线连接

- 东芝推出TXZ+TM族高级系列基于Arm® Cortex®-M4的新款M4G组MCU

- 51单片机-AD与DA合成文件

- V1 芯片加持 vivo X70 Pro或将手机摄影带入硬件级算法时代

- IC分销商:8英寸产能吃紧将继续推升明年Q1的芯片价格

- Syndion® GP:赋能先进功率器件的未来

- 长江存储发布PCle4.0固态硬盘致态TiPro7000 顺序读取速度740MB/s

- UBOOT-1.1.6在S3C2410上的移植(基于GEC2410)

- ROHM的SiC MOSFET和SiC SBD成功应用于Apex Microtechnology的工业设备功率模块系列

- 基于恩智浦MPC5744P的SAE J1939协议栈开发

- Allegro MicroSystems 在 2024 年德国慕尼黑电子展上推出先进的磁性和电感式位置感测解决方案

- 左手车钥匙,右手活体检测雷达,UWB上车势在必行!

- 狂飙十年,国产CIS挤上牌桌

- 神盾短刀电池+雷神EM-i超级电混,吉利新能源甩出了两张“王炸”

- 浅谈功能安全之故障(fault),错误(error),失效(failure)

- 智能汽车2.0周期,这几大核心产业链迎来重大机会!

- 美日研发新型电池,宁德时代面临挑战?中国新能源电池产业如何应对?

- Rambus推出业界首款HBM 4控制器IP:背后有哪些技术细节?

- 村田推出高精度汽车用6轴惯性传感器

- 福特获得预充电报警专利 有助于节约成本和应对紧急情况

人工智能算法(卷2)-受大自然启发的算法

人工智能算法(卷2)-受大自然启发的算法 21年电赛题目合集

21年电赛题目合集

京公网安备 11010802033920号

京公网安备 11010802033920号