摘要:SAA7185是PHILIPS公司推出的内含10-bit DACs的数字视频编码器。它集D/A和编码于一身,并可以对输入的16比特YUV方式、CCIR656格式和MPEG格式等数据进行编码及D/A转换数字到模拟的转换,以输出PAL制式、NTSC制式的复合视频信号(CVBS)或S-Video方式的Y/C分量信号和复合全电视信号。因此,SAA7185可广泛应用于VCD小影碟机、放映机和数字电视等许多系统中。文中详细介绍了它的结构特点、引脚功能和工作原理,给出了它的典型应用电路。

关键词:数字视频编码器;SAA7185;D/A转换

1 概述

SAA7185是PHILIPS公司的多功能数字视频编码器。它能接收16/8bit 的4:2:2 的YUV格式、CCIR656 格式或8bit MPEG格式的视频数据,并将其编码成PAL制式、NTSC制式的复合视频信号(CVBS)或S-Video方式的Y/C分量信号和复合全电视信号。SAA7185先进高度的灵活性和多种方式的输入和输出接口特性使其能够完成多种转换,从而使得SAA7185可以广泛应用于VCD小影碟机、放映机和数字电视等许多系统中。它的主要特点有:

● 是一种数字PAL/NTSC电视制式编码器;

● 具有8bit MPEG和16bit YUV输入端口;

● 可选择I2C总线或MPU并行两种控制方式;

● 编码器有主、从两种工作方式;

● 输入行、场同步和输出行同步相位可编程;

● 可对输出同步信号和消隐信号的上升/下降时间进行控制;

● 可以同时输出复合视频信号(CVBS)和S-Video方式的Y/C分量信号和复合全电视信号。

2 引脚功能

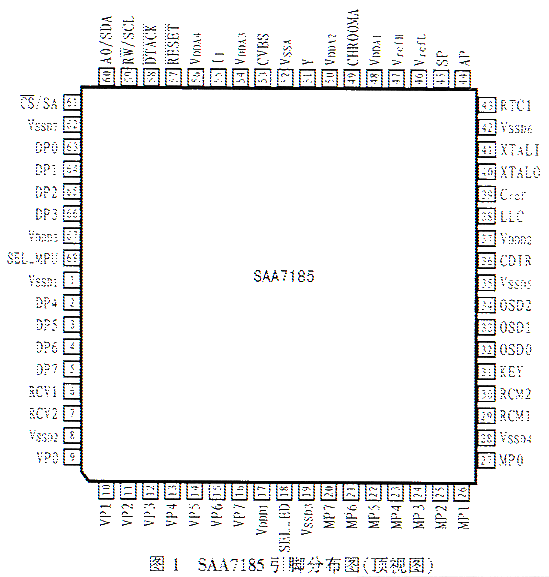

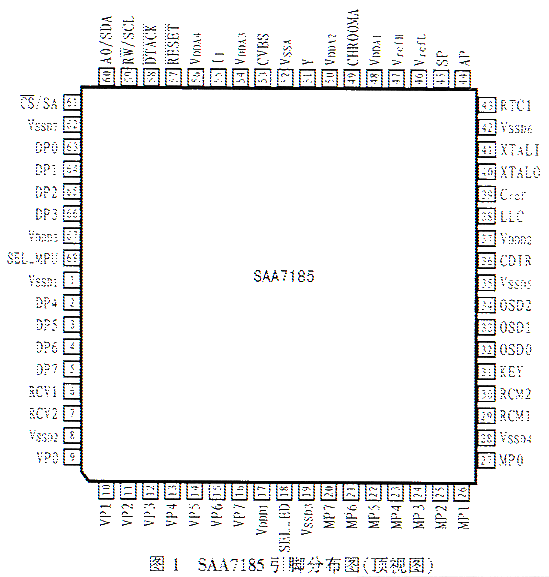

SAA7185的引脚排列如图1(顶视图)所示。它采用PLCC68封装。各引脚的功能及说明如表1所列。

表1 SAA7185的引脚功能描述

管 脚

名 称

I/O/P/G

功 能 描 述

1,8,19,28,35,42,62

VSSD1-7

G

数字地

2~5

DP4~7

I/O

数据口的高4位。如果管脚68(SEL-MPU)为高电平,这些端口就是并行MPU数据总线接口;否则,就是视频数据的UV数据端口

6

RCV1

I/O

视频光栅控制端口1。取决于同步模式,该管脚接收或提供一个VS/FS/FSEQ信号

7

RCV2

I/O

视频光栅控制端口2。取决于同步模式,该管脚接收或提供一个VS/HREF/CBL信号

9~16

VP0~VP7

O

视频端口。兼容CCIR 656格式的输入视频数据,如果输入的是16比特的DIG-TV2格式的数据,则它们就是Y数据输入端口

17,37,67

VDDD1-3

P

数字供电

18

SEL-ED

I

选择解码器的输入数据,来自于MPEG端口或视频端口

20~27

MP7~MP0

I

MPEG端口。是一个支持CCIR 656格式的复用的YUV数据输入端口

17,37,67

VDDD1-3

P

数据供电

18

SEL-ED

I

选择解码器的输入数据,来自于MPEG端口或视频端口

2027

MP7MP0

I

MPEG端口。是一个支持CCIR 656格式的复用的YUV数据输入端口

29

RCM1

I

MPEG光栅控制端口1。该管脚提供一个VS/FS/FSEQ信号

30

RCM2

I

MPEG光栅控制端口2。该管脚提供一个HS信号

31

KEY

I

OSD的关键信号。高有效

3234

OSD0-2

O

内部OSD查询表的索引

36

CDIR

I

时钟方向。如果CDIR为高电平,电路接收时钟信号,否则,LLC和CREF信号都由内部晶振产生

38

LLC

I/O

行锁定时钟

39

CREF

I/O

时钟参考信号

40

XTALO

O

晶振输出

41

XYALI

I

晶振输入。如果不用,该管脚应接地

43

RTCI

I

实时控制输入

44,45

AP,SP

I

测试管脚

46,47

VREFL,VREFH

P

DAC的低参考电压输入和高参考电压输入

48,50,54,56

VDDA1-4

P

模拟供电

49

CHROMA

O

色度信号的模拟输出

51

Y

O

亮度信号的模拟输出

52

VSSA

G

DAC和输出放大器的模拟地

53

CVBS

O

CVBS信号的模拟输出

55

II

I

输出放大器的电流输入

57

RESET

I

复位输入

58

DTACK

O

并行MPU接口的数据应答输出。低有效;否则,为高阻

59

RW/SDA

I/O

如果管脚68(SEL-MPU)为高电平,该管脚为MPU接口的地址信号;否则,为I2C总线的串行数据输入/输出

60

A0/SDA

I/O

如果管脚68(SEL-MPU)为高电平,该管脚为MPU接口的地址信号;否则,为I2C总线的串行数据输入/输出

61

CS/SA

I/O

如果管脚68(SEL-MPU)为高电平,该管脚为MPU接口的片选信号;否则,为I2C总线的子地址选择管脚

63~66

DP0~DP3

I

如果管脚68(SEL-MPU)为高电平,这是并行MPU接口的数据总线的低4比特;否则,为视频数据的UV数据

68

SEL-MPU

I

如果为高电平,则并行MPU接口有效;否则,I2C总线接口有效

3 工作原理

SAA7185的内部功能框图如图2所示,下面介绍其工作原理。

3.1 数据的输入

兼容MPEG的SAA7185数字视频解码器可以将数字亮度和色度信号编码成模拟CVBS(复合视频信号),同时也可以将其编码成S-Video信号(Y/C分离的分量信号和复合全电视信号)。器件中的数模转换器(DAC)具有10-bit的分辨率,编码器提供有3路8-bit宽度的数据端口,以满足不同的应用。MPEG端口(MP)和视频端口(VP)均可接收复合的YcrCb数据。视频端口(VP)也可以处理兼容DIG-TV2系列的16-bit YUV信号,此时数据口(VP)用于U/V信号。另外,数据口也可以作为8-bit数据宽度的微处理器接口。

3.2 输出接口

在输出接口上,被编码的Y和C信号以10-bit的分辨率从数字信号转化为模拟信号,同时Y和C信号也被合成为10-bit CVBS信号。在合成前,亮度信号被送到更深一级的滤波器,以抑制信号中的副载波。这样可减小色失真,这对具有标准CVBS信号输入的电视机来说是非常有益的。同步脉冲的斜度不受任何有效色失真的影响。而输出的CVBS信号和Y、C信号具有同样的处理延时。数模转换器(DAC)的输出电压可通过软件设置到最小的输出电压,以满足特殊的需求。

图2

3.3 同步

该编码器可以工作于主、从两种模式。

在从模式下,电路在双向端口RCV1接收同步脉冲。与VP(和DP)的视频信号有关的定时和触发特性可以通过对RCV1的极性和片上延时进行编程来加以改变。如果水平相位不受RCV1的影响,那么可通过RCV2管脚来提供水平相位,而定时和触发特性也可以通过RCV2来改变。如果垂直和水平脉冲来自于RCV1,则RCV2可以用于水平或复合消隐的输入或输出。

在主模式下,电路的时基可以连续地自由运行。在RCV1端口,IC可输出具有2.5或3行时延的场同步信号(VS)、奇/偶场信号(ODD/EVEN)、或场序列信号(FSEQ);而在RCV2端口,IC可以提供可编程的开始和结束水平相位。RCV1或RCV2端口的输出脉冲相位与VP端口有关,两种信号的极性都是可选择的。

3.4 控制接口

SAA7185有两种控制接口:I2C总线接口和8-bit并行微处理器接口。I2C总线接口是一个标准的从收发器,支持7-bit从地址和100kbits/s 的发送速率,它有一个带自动增量功能的8-bit的子地址。除了一个可读的状态字外,其它所有的寄存器只可进行写操作。

2 引脚功能

SAA7185的引脚排列如图1(顶视图)所示。它采用PLCC68封装。各引脚的功能及说明如表1所列。

表1 SAA7185的引脚功能描述

管 脚

名 称

I/O/P/G

功 能 描 述

1,8,19,28,35,42,62

VSSD1-7

G

数字地

2~5

DP4~7

I/O

数据口的高4位。如果管脚68(SEL-MPU)为高电平,这些端口就是并行MPU数据总线接口;否则,就是视频数据的UV数据端口

6

RCV1

I/O

视频光栅控制端口1。取决于同步模式,该管脚接收或提供一个VS/FS/FSEQ信号

7

RCV2

I/O

视频光栅控制端口2。取决于同步模式,该管脚接收或提供一个VS/HREF/CBL信号

9~16

VP0~VP7

O

视频端口。兼容CCIR 656格式的输入视频数据,如果输入的是16比特的DIG-TV2格式的数据,则它们就是Y数据输入端口

17,37,67

VDDD1-3

P

数字供电

18

SEL-ED

I

选择解码器的输入数据,来自于MPEG端口或视频端口

20~27

MP7~MP0

I

MPEG端口。是一个支持CCIR 656格式的复用的YUV数据输入端口

17,37,67

VDDD1-3

P

数据供电

18

SEL-ED

I

选择解码器的输入数据,来自于MPEG端口或视频端口

2027

MP7MP0

I

MPEG端口。是一个支持CCIR 656格式的复用的YUV数据输入端口

29

RCM1

I

MPEG光栅控制端口1。该管脚提供一个VS/FS/FSEQ信号

30

RCM2

I

MPEG光栅控制端口2。该管脚提供一个HS信号

31

KEY

I

OSD的关键信号。高有效

3234

OSD0-2

O

内部OSD查询表的索引

36

CDIR

I

时钟方向。如果CDIR为高电平,电路接收时钟信号,否则,LLC和CREF信号都由内部晶振产生

38

LLC

I/O

行锁定时钟

39

CREF

I/O

时钟参考信号

40

XTALO

O

晶振输出

41

XYALI

I

晶振输入。如果不用,该管脚应接地

43

RTCI

I

实时控制输入

44,45

AP,SP

I

测试管脚

46,47

VREFL,VREFH

P

DAC的低参考电压输入和高参考电压输入

48,50,54,56

VDDA1-4

P

模拟供电

49

CHROMA

O

色度信号的模拟输出

51

Y

O

亮度信号的模拟输出

52

VSSA

G

DAC和输出放大器的模拟地

53

CVBS

O

CVBS信号的模拟输出

55

II

I

输出放大器的电流输入

57

RESET

I

复位输入

58

DTACK

O

并行MPU接口的数据应答输出。低有效;否则,为高阻

59

RW/SDA

I/O

如果管脚68(SEL-MPU)为高电平,该管脚为MPU接口的地址信号;否则,为I2C总线的串行数据输入/输出

60

A0/SDA

I/O

如果管脚68(SEL-MPU)为高电平,该管脚为MPU接口的地址信号;否则,为I2C总线的串行数据输入/输出

61

CS/SA

I/O

如果管脚68(SEL-MPU)为高电平,该管脚为MPU接口的片选信号;否则,为I2C总线的子地址选择管脚

63~66

DP0~DP3

I

如果管脚68(SEL-MPU)为高电平,这是并行MPU接口的数据总线的低4比特;否则,为视频数据的UV数据

68

SEL-MPU

I

如果为高电平,则并行MPU接口有效;否则,I2C总线接口有效

3 工作原理

SAA7185的内部功能框图如图2所示,下面介绍其工作原理。

3.1 数据的输入

兼容MPEG的SAA7185数字视频解码器可以将数字亮度和色度信号编码成模拟CVBS(复合视频信号),同时也可以将其编码成S-Video信号(Y/C分离的分量信号和复合全电视信号)。器件中的数模转换器(DAC)具有10-bit的分辨率,编码器提供有3路8-bit宽度的数据端口,以满足不同的应用。MPEG端口(MP)和视频端口(VP)均可接收复合的YcrCb数据。视频端口(VP)也可以处理兼容DIG-TV2系列的16-bit YUV信号,此时数据口(VP)用于U/V信号。另外,数据口也可以作为8-bit数据宽度的微处理器接口。

3.2 输出接口

在输出接口上,被编码的Y和C信号以10-bit的分辨率从数字信号转化为模拟信号,同时Y和C信号也被合成为10-bit CVBS信号。在合成前,亮度信号被送到更深一级的滤波器,以抑制信号中的副载波。这样可减小色失真,这对具有标准CVBS信号输入的电视机来说是非常有益的。同步脉冲的斜度不受任何有效色失真的影响。而输出的CVBS信号和Y、C信号具有同样的处理延时。数模转换器(DAC)的输出电压可通过软件设置到最小的输出电压,以满足特殊的需求。

图2

3.3 同步

该编码器可以工作于主、从两种模式。

在从模式下,电路在双向端口RCV1接收同步脉冲。与VP(和DP)的视频信号有关的定时和触发特性可以通过对RCV1的极性和片上延时进行编程来加以改变。如果水平相位不受RCV1的影响,那么可通过RCV2管脚来提供水平相位,而定时和触发特性也可以通过RCV2来改变。如果垂直和水平脉冲来自于RCV1,则RCV2可以用于水平或复合消隐的输入或输出。

在主模式下,电路的时基可以连续地自由运行。在RCV1端口,IC可输出具有2.5或3行时延的场同步信号(VS)、奇/偶场信号(ODD/EVEN)、或场序列信号(FSEQ);而在RCV2端口,IC可以提供可编程的开始和结束水平相位。RCV1或RCV2端口的输出脉冲相位与VP端口有关,两种信号的极性都是可选择的。

3.4 控制接口

SAA7185有两种控制接口:I2C总线接口和8-bit并行微处理器接口。I2C总线接口是一个标准的从收发器,支持7-bit从地址和100kbits/s 的发送速率,它有一个带自动增量功能的8-bit的子地址。除了一个可读的状态字外,其它所有的寄存器只可进行写操作。

并行接口包括两个寄存器,一个具有自增量功能,它包含有控制寄存器当前的地址。另一个包含有实际的数据。当前的地址寄存器可以映射到相应的控制寄存器。状态字只能通过一个通往地址寄存器的读通道随意读出,没有提供其它的读通道。

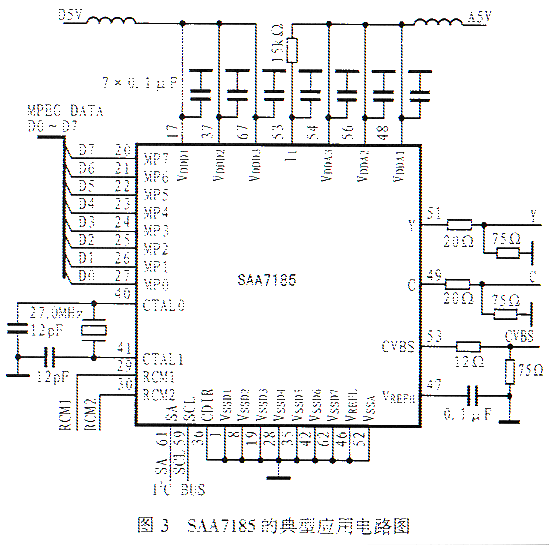

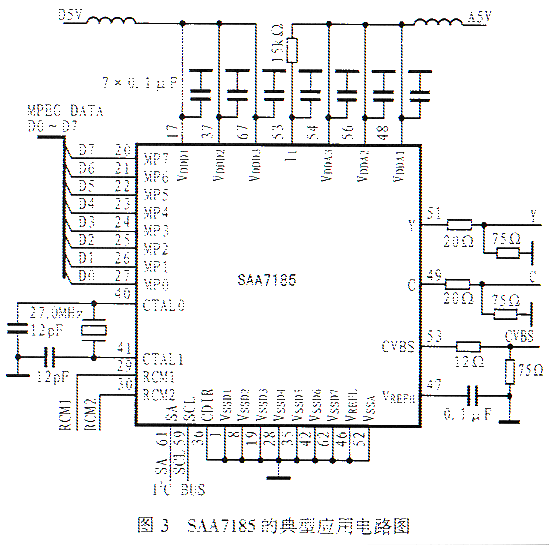

4 典型应用

图3是SAA7185的一个应用电路。其中电路的模拟和数字电源均为5V。该电路为 VCD小影碟机和多媒体电影解压卡中常用的数字编码电路,系统中的输入数据可以是16比特YUV方式,也可是CCIR656格式。图中输入的是8比特MPEG-1数据,采用与CCIR656兼容的方式。在该系统中,SAA7185编码器工作于主模式。

并行接口包括两个寄存器,一个具有自增量功能,它包含有控制寄存器当前的地址。另一个包含有实际的数据。当前的地址寄存器可以映射到相应的控制寄存器。状态字只能通过一个通往地址寄存器的读通道随意读出,没有提供其它的读通道。

4 典型应用

图3是SAA7185的一个应用电路。其中电路的模拟和数字电源均为5V。该电路为 VCD小影碟机和多媒体电影解压卡中常用的数字编码电路,系统中的输入数据可以是16比特YUV方式,也可是CCIR656格式。图中输入的是8比特MPEG-1数据,采用与CCIR656兼容的方式。在该系统中,SAA7185编码器工作于主模式。

引用地址:单片集成编码器SAA7185及其应用

2 引脚功能

SAA7185的引脚排列如图1(顶视图)所示。它采用PLCC68封装。各引脚的功能及说明如表1所列。

表1 SAA7185的引脚功能描述

管 脚

名 称

I/O/P/G

功 能 描 述

1,8,19,28,35,42,62

VSSD1-7

G

数字地

2~5

DP4~7

I/O

数据口的高4位。如果管脚68(SEL-MPU)为高电平,这些端口就是并行MPU数据总线接口;否则,就是视频数据的UV数据端口

6

RCV1

I/O

视频光栅控制端口1。取决于同步模式,该管脚接收或提供一个VS/FS/FSEQ信号

7

RCV2

I/O

视频光栅控制端口2。取决于同步模式,该管脚接收或提供一个VS/HREF/CBL信号

9~16

VP0~VP7

O

视频端口。兼容CCIR 656格式的输入视频数据,如果输入的是16比特的DIG-TV2格式的数据,则它们就是Y数据输入端口

17,37,67

VDDD1-3

P

数字供电

18

SEL-ED

I

选择解码器的输入数据,来自于MPEG端口或视频端口

20~27

MP7~MP0

I

MPEG端口。是一个支持CCIR 656格式的复用的YUV数据输入端口

17,37,67

VDDD1-3

P

数据供电

18

SEL-ED

I

选择解码器的输入数据,来自于MPEG端口或视频端口

2027

MP7MP0

I

MPEG端口。是一个支持CCIR 656格式的复用的YUV数据输入端口

29

RCM1

I

MPEG光栅控制端口1。该管脚提供一个VS/FS/FSEQ信号

30

RCM2

I

MPEG光栅控制端口2。该管脚提供一个HS信号

31

KEY

I

OSD的关键信号。高有效

3234

OSD0-2

O

内部OSD查询表的索引

36

CDIR

I

时钟方向。如果CDIR为高电平,电路接收时钟信号,否则,LLC和CREF信号都由内部晶振产生

38

LLC

I/O

行锁定时钟

39

CREF

I/O

时钟参考信号

40

XTALO

O

晶振输出

41

XYALI

I

晶振输入。如果不用,该管脚应接地

43

RTCI

I

实时控制输入

44,45

AP,SP

I

测试管脚

46,47

VREFL,VREFH

P

DAC的低参考电压输入和高参考电压输入

48,50,54,56

VDDA1-4

P

模拟供电

49

CHROMA

O

色度信号的模拟输出

51

Y

O

亮度信号的模拟输出

52

VSSA

G

DAC和输出放大器的模拟地

53

CVBS

O

CVBS信号的模拟输出

55

II

I

输出放大器的电流输入

57

RESET

I

复位输入

58

DTACK

O

并行MPU接口的数据应答输出。低有效;否则,为高阻

59

RW/SDA

I/O

如果管脚68(SEL-MPU)为高电平,该管脚为MPU接口的地址信号;否则,为I2C总线的串行数据输入/输出

60

A0/SDA

I/O

如果管脚68(SEL-MPU)为高电平,该管脚为MPU接口的地址信号;否则,为I2C总线的串行数据输入/输出

61

CS/SA

I/O

如果管脚68(SEL-MPU)为高电平,该管脚为MPU接口的片选信号;否则,为I2C总线的子地址选择管脚

63~66

DP0~DP3

I

如果管脚68(SEL-MPU)为高电平,这是并行MPU接口的数据总线的低4比特;否则,为视频数据的UV数据

68

SEL-MPU

I

如果为高电平,则并行MPU接口有效;否则,I2C总线接口有效

3 工作原理

SAA7185的内部功能框图如图2所示,下面介绍其工作原理。

3.1 数据的输入

兼容MPEG的SAA7185数字视频解码器可以将数字亮度和色度信号编码成模拟CVBS(复合视频信号),同时也可以将其编码成S-Video信号(Y/C分离的分量信号和复合全电视信号)。器件中的数模转换器(DAC)具有10-bit的分辨率,编码器提供有3路8-bit宽度的数据端口,以满足不同的应用。MPEG端口(MP)和视频端口(VP)均可接收复合的YcrCb数据。视频端口(VP)也可以处理兼容DIG-TV2系列的16-bit YUV信号,此时数据口(VP)用于U/V信号。另外,数据口也可以作为8-bit数据宽度的微处理器接口。

3.2 输出接口

在输出接口上,被编码的Y和C信号以10-bit的分辨率从数字信号转化为模拟信号,同时Y和C信号也被合成为10-bit CVBS信号。在合成前,亮度信号被送到更深一级的滤波器,以抑制信号中的副载波。这样可减小色失真,这对具有标准CVBS信号输入的电视机来说是非常有益的。同步脉冲的斜度不受任何有效色失真的影响。而输出的CVBS信号和Y、C信号具有同样的处理延时。数模转换器(DAC)的输出电压可通过软件设置到最小的输出电压,以满足特殊的需求。

图2

3.3 同步

该编码器可以工作于主、从两种模式。

在从模式下,电路在双向端口RCV1接收同步脉冲。与VP(和DP)的视频信号有关的定时和触发特性可以通过对RCV1的极性和片上延时进行编程来加以改变。如果水平相位不受RCV1的影响,那么可通过RCV2管脚来提供水平相位,而定时和触发特性也可以通过RCV2来改变。如果垂直和水平脉冲来自于RCV1,则RCV2可以用于水平或复合消隐的输入或输出。

在主模式下,电路的时基可以连续地自由运行。在RCV1端口,IC可输出具有2.5或3行时延的场同步信号(VS)、奇/偶场信号(ODD/EVEN)、或场序列信号(FSEQ);而在RCV2端口,IC可以提供可编程的开始和结束水平相位。RCV1或RCV2端口的输出脉冲相位与VP端口有关,两种信号的极性都是可选择的。

3.4 控制接口

SAA7185有两种控制接口:I2C总线接口和8-bit并行微处理器接口。I2C总线接口是一个标准的从收发器,支持7-bit从地址和100kbits/s 的发送速率,它有一个带自动增量功能的8-bit的子地址。除了一个可读的状态字外,其它所有的寄存器只可进行写操作。

2 引脚功能

SAA7185的引脚排列如图1(顶视图)所示。它采用PLCC68封装。各引脚的功能及说明如表1所列。

表1 SAA7185的引脚功能描述

管 脚

名 称

I/O/P/G

功 能 描 述

1,8,19,28,35,42,62

VSSD1-7

G

数字地

2~5

DP4~7

I/O

数据口的高4位。如果管脚68(SEL-MPU)为高电平,这些端口就是并行MPU数据总线接口;否则,就是视频数据的UV数据端口

6

RCV1

I/O

视频光栅控制端口1。取决于同步模式,该管脚接收或提供一个VS/FS/FSEQ信号

7

RCV2

I/O

视频光栅控制端口2。取决于同步模式,该管脚接收或提供一个VS/HREF/CBL信号

9~16

VP0~VP7

O

视频端口。兼容CCIR 656格式的输入视频数据,如果输入的是16比特的DIG-TV2格式的数据,则它们就是Y数据输入端口

17,37,67

VDDD1-3

P

数字供电

18

SEL-ED

I

选择解码器的输入数据,来自于MPEG端口或视频端口

20~27

MP7~MP0

I

MPEG端口。是一个支持CCIR 656格式的复用的YUV数据输入端口

17,37,67

VDDD1-3

P

数据供电

18

SEL-ED

I

选择解码器的输入数据,来自于MPEG端口或视频端口

2027

MP7MP0

I

MPEG端口。是一个支持CCIR 656格式的复用的YUV数据输入端口

29

RCM1

I

MPEG光栅控制端口1。该管脚提供一个VS/FS/FSEQ信号

30

RCM2

I

MPEG光栅控制端口2。该管脚提供一个HS信号

31

KEY

I

OSD的关键信号。高有效

3234

OSD0-2

O

内部OSD查询表的索引

36

CDIR

I

时钟方向。如果CDIR为高电平,电路接收时钟信号,否则,LLC和CREF信号都由内部晶振产生

38

LLC

I/O

行锁定时钟

39

CREF

I/O

时钟参考信号

40

XTALO

O

晶振输出

41

XYALI

I

晶振输入。如果不用,该管脚应接地

43

RTCI

I

实时控制输入

44,45

AP,SP

I

测试管脚

46,47

VREFL,VREFH

P

DAC的低参考电压输入和高参考电压输入

48,50,54,56

VDDA1-4

P

模拟供电

49

CHROMA

O

色度信号的模拟输出

51

Y

O

亮度信号的模拟输出

52

VSSA

G

DAC和输出放大器的模拟地

53

CVBS

O

CVBS信号的模拟输出

55

II

I

输出放大器的电流输入

57

RESET

I

复位输入

58

DTACK

O

并行MPU接口的数据应答输出。低有效;否则,为高阻

59

RW/SDA

I/O

如果管脚68(SEL-MPU)为高电平,该管脚为MPU接口的地址信号;否则,为I2C总线的串行数据输入/输出

60

A0/SDA

I/O

如果管脚68(SEL-MPU)为高电平,该管脚为MPU接口的地址信号;否则,为I2C总线的串行数据输入/输出

61

CS/SA

I/O

如果管脚68(SEL-MPU)为高电平,该管脚为MPU接口的片选信号;否则,为I2C总线的子地址选择管脚

63~66

DP0~DP3

I

如果管脚68(SEL-MPU)为高电平,这是并行MPU接口的数据总线的低4比特;否则,为视频数据的UV数据

68

SEL-MPU

I

如果为高电平,则并行MPU接口有效;否则,I2C总线接口有效

3 工作原理

SAA7185的内部功能框图如图2所示,下面介绍其工作原理。

3.1 数据的输入

兼容MPEG的SAA7185数字视频解码器可以将数字亮度和色度信号编码成模拟CVBS(复合视频信号),同时也可以将其编码成S-Video信号(Y/C分离的分量信号和复合全电视信号)。器件中的数模转换器(DAC)具有10-bit的分辨率,编码器提供有3路8-bit宽度的数据端口,以满足不同的应用。MPEG端口(MP)和视频端口(VP)均可接收复合的YcrCb数据。视频端口(VP)也可以处理兼容DIG-TV2系列的16-bit YUV信号,此时数据口(VP)用于U/V信号。另外,数据口也可以作为8-bit数据宽度的微处理器接口。

3.2 输出接口

在输出接口上,被编码的Y和C信号以10-bit的分辨率从数字信号转化为模拟信号,同时Y和C信号也被合成为10-bit CVBS信号。在合成前,亮度信号被送到更深一级的滤波器,以抑制信号中的副载波。这样可减小色失真,这对具有标准CVBS信号输入的电视机来说是非常有益的。同步脉冲的斜度不受任何有效色失真的影响。而输出的CVBS信号和Y、C信号具有同样的处理延时。数模转换器(DAC)的输出电压可通过软件设置到最小的输出电压,以满足特殊的需求。

图2

3.3 同步

该编码器可以工作于主、从两种模式。

在从模式下,电路在双向端口RCV1接收同步脉冲。与VP(和DP)的视频信号有关的定时和触发特性可以通过对RCV1的极性和片上延时进行编程来加以改变。如果水平相位不受RCV1的影响,那么可通过RCV2管脚来提供水平相位,而定时和触发特性也可以通过RCV2来改变。如果垂直和水平脉冲来自于RCV1,则RCV2可以用于水平或复合消隐的输入或输出。

在主模式下,电路的时基可以连续地自由运行。在RCV1端口,IC可输出具有2.5或3行时延的场同步信号(VS)、奇/偶场信号(ODD/EVEN)、或场序列信号(FSEQ);而在RCV2端口,IC可以提供可编程的开始和结束水平相位。RCV1或RCV2端口的输出脉冲相位与VP端口有关,两种信号的极性都是可选择的。

3.4 控制接口

SAA7185有两种控制接口:I2C总线接口和8-bit并行微处理器接口。I2C总线接口是一个标准的从收发器,支持7-bit从地址和100kbits/s 的发送速率,它有一个带自动增量功能的8-bit的子地址。除了一个可读的状态字外,其它所有的寄存器只可进行写操作。

并行接口包括两个寄存器,一个具有自增量功能,它包含有控制寄存器当前的地址。另一个包含有实际的数据。当前的地址寄存器可以映射到相应的控制寄存器。状态字只能通过一个通往地址寄存器的读通道随意读出,没有提供其它的读通道。

4 典型应用

图3是SAA7185的一个应用电路。其中电路的模拟和数字电源均为5V。该电路为 VCD小影碟机和多媒体电影解压卡中常用的数字编码电路,系统中的输入数据可以是16比特YUV方式,也可是CCIR656格式。图中输入的是8比特MPEG-1数据,采用与CCIR656兼容的方式。在该系统中,SAA7185编码器工作于主模式。

并行接口包括两个寄存器,一个具有自增量功能,它包含有控制寄存器当前的地址。另一个包含有实际的数据。当前的地址寄存器可以映射到相应的控制寄存器。状态字只能通过一个通往地址寄存器的读通道随意读出,没有提供其它的读通道。

4 典型应用

图3是SAA7185的一个应用电路。其中电路的模拟和数字电源均为5V。该电路为 VCD小影碟机和多媒体电影解压卡中常用的数字编码电路,系统中的输入数据可以是16比特YUV方式,也可是CCIR656格式。图中输入的是8比特MPEG-1数据,采用与CCIR656兼容的方式。在该系统中,SAA7185编码器工作于主模式。

上一篇:16/20位立体声音频编解码器PCM3002

下一篇:霍夫曼解码器的设计及在MP3解码中的应用

- 热门资源推荐

- 热门放大器推荐

小广播

热门活动

换一批

更多

最新手机便携文章

- 美光推出速率与能效领先的 60TB SSD

- 古尔曼称苹果明年推出 AirTag 2 追踪器:升级 UWB 超宽带芯片,精确定位范围提升 3 倍

- 消息称苹果自研再下一城:蓝牙+Wi-Fi芯片 2025年iPhone 17系列首发

- 苹果从iPhone 18 Pro开始将弃用高通5G芯片

- 印尼投资部长确认:苹果计划在当地投资10亿美元建造零部件工厂

- 消息称苹果有望2026下半年推出折叠iPhone,并重振折叠屏手机市场

- 华为麒麟9020/9030/9040处理器曝光:小步快跑 四大方面升级

- 汇顶超声波指纹方案助力iQOO Neo10流畅解锁体验

- 曝苹果自研5G基带性能弱于高通:iPhone信号问题无解

更多开源项目推荐

更多精选电路图

更多热门文章

更多每日新闻

更多往期活动

厂商技术中心

Verilog HDL数字集成电路设计原理与应用

Verilog HDL数字集成电路设计原理与应用 TTLM4250CJ

TTLM4250CJ

京公网安备 11010802033920号

京公网安备 11010802033920号