摘要:MSM9841是日本OKI(冲)电气半导体公司研制的单声道/立体声语音控制处理大规模集成芯片。文中介绍了该芯片的结构、特点、工作原理及其在数字语音录放机中的应用。

关键词:录放机 MSM9841 FIFO

1 引言

MSM9841是日本OKI(冲)电气半导体公司研制的带有1kbitFIFO(先进先出)存储器的单声道/立体声语音控制处理大规模集成芯片。它可以很方便的同外部系统或非半导体存储器进行接口,且具有多种录放模式。由于该芯片采用了较新的ADPCM2算法,因而可以保证非常高的语音回放质量。MSM9841的录音和回放功能可以由微处理器通过8/16bit的总线接口来进行控制。MSM9841采用56脚QFP封装,电源电压为2.7V~5.5V,振荡频率为4.096MHz时的代样频率有以下值可供选择:4.0 kHz、6.4 kHz、8.0 kHz、12.8 kHz、16.0 kHz、32.0 kHz(仅用于回放);振荡频率为5.6448 MHz时,采样频率可以选择22.05 kHz或44.1 kHz(仅用于回放)。MSM9841具有8/16bit总线接口和DMA接口且内含低通滤波器、14bitA/D和D/A转换器,采样频率为16 kHz或更低;具有由用户定义(256/512/1024bit)的FIFO存储功能(当使用8 kHz采样频率,4bitADPCM2/ADPCM算法,非立体声模式时,其缓冲时间为32ms);支持4种录放压缩算法,即4/5/6/7/8bit ADPCM2算法、4bit ADPCM算法、16 bit PCM算法和8bit非线性PCM算法;通过控制命令可实现8级音量控制(0dB~21dB)。

2 引脚排列及功能

MSM9841的引脚排列如图1所示,各引脚的功能如下:

D15~D8:对于8 bit总线接口,这些管脚可以通过命令被定义到外部存储器的输入输出接口。否则,这些管脚只能定义为输入管脚。对于16 bit总线接口,这些管脚可用作外部存储器或微处理器的双向数据总线。

D7~D0:到外部存储器或微处理器的双向数据总线。

WR:写允许,低有效。

RD:读允许,低有效。

CS:读写功能允许,低有效(低电平时,允许读写功能操作)。

D/C:当该管脚为高电平时,语音数据可以从D0~D15引脚输入或输出。当该管脚为低电平时,D0~D7引脚用于输入控制命令或输出状态。

BUSY:当处于录音、回放、暂停状态时,该管脚输出低电平。

图2

EMP:当FIFO存储器中无数据时该管脚输出高电平,通过命令可使该管脚由高电平变为低电平。

MID:当FIFO中的数据超过FIFO存储空间的一半时,该管脚输出高电平。在回放期间,MID为高电平时开始语音合成。通过命令可使MID由高电平变成低电平。当不使用FIFO时,该管脚可为语音的输入/输出提供一个同步信号。

FUL/DREQR:当FIFO存储空间已满时,该管脚输出高电平。在回放期间,该管脚为高电平,FIFO中不能写入数据。FUL/DREQR输出的高电平可由命令输入来将其改变成低电平。当选择DMA转换和立体声回放时,DREQR输出高电平信号表示需要DMA转换。DREQR输出的高电平亦可由命令输入平将其改变成低电平。

CH/DACKR:当选择立体声回放且CH为高电平时,EMP、MID或FUL管脚输出右移FIFO的状态。当CH为低电平时,EMP、MID或FUL管脚输出左移FIFO的状态。在录音和单声道回放时需将该管脚设置为低电平。当选择DMA转换和立体声回放时,该管脚为DACKR功能。在这种情况下,输入DMA转换应答信号到DACKR。当DACKR为低电平时,IOW信号被接受。DACKR输出的低电平可由命令输入来将其改变成高电平。

DREQL:当选择DMA转换和立体声回放时,DREQL输出高电平表示需要DMA转换。DREQL输出的高电平可由命令输入来将其改变成低电平。

DACKL:当DMA控制器允许DMA转换时,可输入一个信号到DACKL端。如果DACKL为低电平,IOW和IOR信号将被接受。当选择立体声回放时,可给DACKL端输入左移FIFO的DMA转换应答信号。DACKL端的低电平可由命令输入将其改变成高电平。如果不使用DMA转换,应将该脚置为高电平。

IOW:在DMA转换时,该管脚为将外部数据写入MSM9841的写脉冲输入管脚。如果不使用DMA转换,将该引脚置为高电平。

IOR:在DMA转换时,该管脚可作为MSM9841的读脉冲输入管脚。如果不使用DMA转换,应将该引脚置为高电平。

图3

ADSD:当使用外部ADC时,该管脚为16bit串行数据输入管脚,如果不使用外部ADC,则应将该引脚置为低电平。

DASD:当使用外部DAC时,该管脚为16 bit串行数据输出管脚。

SIOCK:当使用外部ADC或DAC时,该管脚为16 bit串行数据输入/输出的同步时钟管脚。

XT,XT:外部振荡器连接管脚,当使用外部时钟时,可将外部时钟输入到该管脚。

VCK:录音和回放时的输出采样频率。当用外部ADC或DAC时,VCK管脚的信号被用作同步信号。

RESET:复位管脚,低有效。

TESTO、TESTI:测试管脚,将该引脚置为低电平。

SG:模拟地输出管脚。

MIN,LIN:内部OP放大器的反相输入端,同相输入端内部已连到信号地。

MOUT,LOUT:MOUT为内部放大器到MIN的输出端,LOUT为内部放大器到LIN的输出端。

AOUTL:内部LPF(低通滤波器)左路模拟信号输出端。它是回放信号波形输出端,将该管脚连到放大器后可驱动扬声器。

AOUTR:内部LPF(低通滤波器)右路模拟信号输出端。它是回放信号波形输出端,将该管脚连到放大器后可驱动扬声器。

DVDD:数字电源。在该管脚和数字地之间应接一个0.1μF电容。

DGND,AGND:数字地和模拟地。

AVDD:模拟电源。在该管脚和模拟地之间应接一个0.1μF电容。

2 引脚排列及功能

MSM9841的引脚排列如图1所示,各引脚的功能如下:

D15~D8:对于8 bit总线接口,这些管脚可以通过命令被定义到外部存储器的输入输出接口。否则,这些管脚只能定义为输入管脚。对于16 bit总线接口,这些管脚可用作外部存储器或微处理器的双向数据总线。

D7~D0:到外部存储器或微处理器的双向数据总线。

WR:写允许,低有效。

RD:读允许,低有效。

CS:读写功能允许,低有效(低电平时,允许读写功能操作)。

D/C:当该管脚为高电平时,语音数据可以从D0~D15引脚输入或输出。当该管脚为低电平时,D0~D7引脚用于输入控制命令或输出状态。

BUSY:当处于录音、回放、暂停状态时,该管脚输出低电平。

图2

EMP:当FIFO存储器中无数据时该管脚输出高电平,通过命令可使该管脚由高电平变为低电平。

MID:当FIFO中的数据超过FIFO存储空间的一半时,该管脚输出高电平。在回放期间,MID为高电平时开始语音合成。通过命令可使MID由高电平变成低电平。当不使用FIFO时,该管脚可为语音的输入/输出提供一个同步信号。

FUL/DREQR:当FIFO存储空间已满时,该管脚输出高电平。在回放期间,该管脚为高电平,FIFO中不能写入数据。FUL/DREQR输出的高电平可由命令输入来将其改变成低电平。当选择DMA转换和立体声回放时,DREQR输出高电平信号表示需要DMA转换。DREQR输出的高电平亦可由命令输入平将其改变成低电平。

CH/DACKR:当选择立体声回放且CH为高电平时,EMP、MID或FUL管脚输出右移FIFO的状态。当CH为低电平时,EMP、MID或FUL管脚输出左移FIFO的状态。在录音和单声道回放时需将该管脚设置为低电平。当选择DMA转换和立体声回放时,该管脚为DACKR功能。在这种情况下,输入DMA转换应答信号到DACKR。当DACKR为低电平时,IOW信号被接受。DACKR输出的低电平可由命令输入来将其改变成高电平。

DREQL:当选择DMA转换和立体声回放时,DREQL输出高电平表示需要DMA转换。DREQL输出的高电平可由命令输入来将其改变成低电平。

DACKL:当DMA控制器允许DMA转换时,可输入一个信号到DACKL端。如果DACKL为低电平,IOW和IOR信号将被接受。当选择立体声回放时,可给DACKL端输入左移FIFO的DMA转换应答信号。DACKL端的低电平可由命令输入将其改变成高电平。如果不使用DMA转换,应将该脚置为高电平。

IOW:在DMA转换时,该管脚为将外部数据写入MSM9841的写脉冲输入管脚。如果不使用DMA转换,将该引脚置为高电平。

IOR:在DMA转换时,该管脚可作为MSM9841的读脉冲输入管脚。如果不使用DMA转换,应将该引脚置为高电平。

图3

ADSD:当使用外部ADC时,该管脚为16bit串行数据输入管脚,如果不使用外部ADC,则应将该引脚置为低电平。

DASD:当使用外部DAC时,该管脚为16 bit串行数据输出管脚。

SIOCK:当使用外部ADC或DAC时,该管脚为16 bit串行数据输入/输出的同步时钟管脚。

XT,XT:外部振荡器连接管脚,当使用外部时钟时,可将外部时钟输入到该管脚。

VCK:录音和回放时的输出采样频率。当用外部ADC或DAC时,VCK管脚的信号被用作同步信号。

RESET:复位管脚,低有效。

TESTO、TESTI:测试管脚,将该引脚置为低电平。

SG:模拟地输出管脚。

MIN,LIN:内部OP放大器的反相输入端,同相输入端内部已连到信号地。

MOUT,LOUT:MOUT为内部放大器到MIN的输出端,LOUT为内部放大器到LIN的输出端。

AOUTL:内部LPF(低通滤波器)左路模拟信号输出端。它是回放信号波形输出端,将该管脚连到放大器后可驱动扬声器。

AOUTR:内部LPF(低通滤波器)右路模拟信号输出端。它是回放信号波形输出端,将该管脚连到放大器后可驱动扬声器。

DVDD:数字电源。在该管脚和数字地之间应接一个0.1μF电容。

DGND,AGND:数字地和模拟地。

AVDD:模拟电源。在该管脚和模拟地之间应接一个0.1μF电容。

3 内部结构及工作原理

MSM9841的内部结构如图2所示,它主要由微处理器、定时控制器、音量控制器、ADPCM2/ADPCM/PCM分析器、ADPCM2/ADPCM/PCM/非线性PCM合成器、直接存储器访问接口、FIFO、ADC、DAC、LPF等部件构成。

对MSM9841可采用二进制编码命令进行控制,从而完成录音、回放、停止、暂停、音量调节、DMA转换、设置使用内部或外部D/A、A/D、信号输出模式选择等功能。该控制命令的长度为8bit。

4 以MSM9841为核心的录放机

基于MSM9841的录放机电路如图3所示,该录放机采用双CPU模式,以单片机AT89C52作为录放音模块的主控单元。键盘和液晶显示模块以AT89C2051作为主控单元,通过串口与录放音模块变换指令与数据。由于本录放机未采用DMA方式,故MSM9841的DMA控制管脚均接高电平。MSM9841中D/C管脚的电平高低可决定数据总线上的数据类型。当D/C为低电平时,数据总线上的信号为系统控制命令;当D/C为高电平时,总线上的信号为语音数据。由于AT89C52是8位单片机,而MSM9841支持16位或8位数据总线,所以,在系统工作时,首先要利用MSM9841的控制命令将其设置为8位数据总线模式。

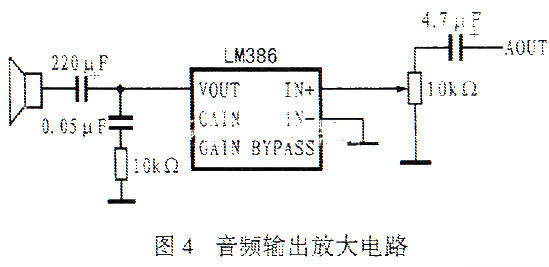

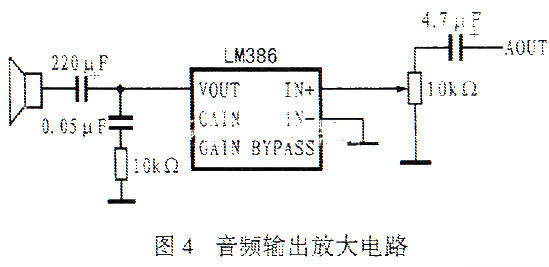

录放机音频输出端采用音频功率放大器LM386,其电路连接如图4所示。当电源电压为+5V时,LM386输出功率为300mW左右。MSM9841内部有2个运算放大器,可用于放大麦克风的语音信号,每个运算放大器对外提供反向输入端和输出端,而同向输入端则在芯片内部与模拟地相连。两个运算放大器可以级连,通过调节外部电阻阻值即可获得所需的放大倍数。通过下式可调节VLO,以使其处于LOUT管脚所允许的电压范围内:

VLO=(R4/R3)VMO=(R2R4/R1R3)VIN(V)

当供电电压为5V时,LOUT引脚所允许的电压范围为1~4V.LOUT管脚在芯片内部与输入低通滤波器相连,可用于去掉超过1/2采样频率的输入频率分量。这样,就可满足数据采样系统所适用的奈奎斯特定理,然后送ADC进行数据采样。放大电路通过隔直电容与麦克风相连,隔直电容主要用于去掉低电平交流信号(约2~20mV)中的直流信号。整个音频输入电路如图5所示。

整个刻录机系统采用4片2M%26;#215;8 bit的DRAM MSM5116800作为语音存储介质,在较高质量的8kbps的采样速率下,若采用4 bit的ADPCM2算法,4片MSM5116800能够记录的语音长度大约是4%26;#215;1.024%26;#215;2000%26;#215;8/(8%26;#215;4)=2048s。2M%26;#215;8 bit的DRAM的地址总线共20位,分为高位地址(即A0~A8和A9R~A11R共12位构成行地址Row address)和低位地址(即A0~A8共9位构成的列地址Column address),两者通过分时复用共用9根地址线A0~A8,每片DRAM的寻址范围为000000H~7FFFFFH,各片DRAM通过不同的CAS信号线来区别。DRAM有多种不同的读写模式和存储单元数据刷新模式,在本系统中,由于所需要的数据率非常低,所以可采用最基本的读写模式,即先发送完整的地址信号(包括行地址和列地址),然后读写;而刷新模式则采用cas-before-ras方式,并将刷新脉冲穿插到读写时序中间。

该系统通过接收键盘指令来完成录放音的操作。录音时,首先利用二进制命令对MSM9841进行初始化,具体内容包括:设置语音合成方式为4 bit的ADPCM2算法;选择采用内部ADC;设置总线宽度为8位;不采用DMA方式;配置FIFO的大小,FIFO最大可配置为1024 bit;设置输出数据的模式;设定采样频率为8.0 kHz。此采样频率可使语音音质大大优于电话的音质。提高采样频率还可使音质进一步得到改善,但录音时间也就相应缩短;反之,较低的采样频率会增加录音时间,但会降低音质。

3 内部结构及工作原理

MSM9841的内部结构如图2所示,它主要由微处理器、定时控制器、音量控制器、ADPCM2/ADPCM/PCM分析器、ADPCM2/ADPCM/PCM/非线性PCM合成器、直接存储器访问接口、FIFO、ADC、DAC、LPF等部件构成。

对MSM9841可采用二进制编码命令进行控制,从而完成录音、回放、停止、暂停、音量调节、DMA转换、设置使用内部或外部D/A、A/D、信号输出模式选择等功能。该控制命令的长度为8bit。

4 以MSM9841为核心的录放机

基于MSM9841的录放机电路如图3所示,该录放机采用双CPU模式,以单片机AT89C52作为录放音模块的主控单元。键盘和液晶显示模块以AT89C2051作为主控单元,通过串口与录放音模块变换指令与数据。由于本录放机未采用DMA方式,故MSM9841的DMA控制管脚均接高电平。MSM9841中D/C管脚的电平高低可决定数据总线上的数据类型。当D/C为低电平时,数据总线上的信号为系统控制命令;当D/C为高电平时,总线上的信号为语音数据。由于AT89C52是8位单片机,而MSM9841支持16位或8位数据总线,所以,在系统工作时,首先要利用MSM9841的控制命令将其设置为8位数据总线模式。

录放机音频输出端采用音频功率放大器LM386,其电路连接如图4所示。当电源电压为+5V时,LM386输出功率为300mW左右。MSM9841内部有2个运算放大器,可用于放大麦克风的语音信号,每个运算放大器对外提供反向输入端和输出端,而同向输入端则在芯片内部与模拟地相连。两个运算放大器可以级连,通过调节外部电阻阻值即可获得所需的放大倍数。通过下式可调节VLO,以使其处于LOUT管脚所允许的电压范围内:

VLO=(R4/R3)VMO=(R2R4/R1R3)VIN(V)

当供电电压为5V时,LOUT引脚所允许的电压范围为1~4V.LOUT管脚在芯片内部与输入低通滤波器相连,可用于去掉超过1/2采样频率的输入频率分量。这样,就可满足数据采样系统所适用的奈奎斯特定理,然后送ADC进行数据采样。放大电路通过隔直电容与麦克风相连,隔直电容主要用于去掉低电平交流信号(约2~20mV)中的直流信号。整个音频输入电路如图5所示。

整个刻录机系统采用4片2M%26;#215;8 bit的DRAM MSM5116800作为语音存储介质,在较高质量的8kbps的采样速率下,若采用4 bit的ADPCM2算法,4片MSM5116800能够记录的语音长度大约是4%26;#215;1.024%26;#215;2000%26;#215;8/(8%26;#215;4)=2048s。2M%26;#215;8 bit的DRAM的地址总线共20位,分为高位地址(即A0~A8和A9R~A11R共12位构成行地址Row address)和低位地址(即A0~A8共9位构成的列地址Column address),两者通过分时复用共用9根地址线A0~A8,每片DRAM的寻址范围为000000H~7FFFFFH,各片DRAM通过不同的CAS信号线来区别。DRAM有多种不同的读写模式和存储单元数据刷新模式,在本系统中,由于所需要的数据率非常低,所以可采用最基本的读写模式,即先发送完整的地址信号(包括行地址和列地址),然后读写;而刷新模式则采用cas-before-ras方式,并将刷新脉冲穿插到读写时序中间。

该系统通过接收键盘指令来完成录放音的操作。录音时,首先利用二进制命令对MSM9841进行初始化,具体内容包括:设置语音合成方式为4 bit的ADPCM2算法;选择采用内部ADC;设置总线宽度为8位;不采用DMA方式;配置FIFO的大小,FIFO最大可配置为1024 bit;设置输出数据的模式;设定采样频率为8.0 kHz。此采样频率可使语音音质大大优于电话的音质。提高采样频率还可使音质进一步得到改善,但录音时间也就相应缩短;反之,较低的采样频率会增加录音时间,但会降低音质。

初始化完成之后即可发出控制命令10H(采样频率为8.0 kHz)来启动录音操作。在录音的过程中当FIFO中的语音数据超过FIFO存储空间一半时,MID引脚将变为高电平,并产生外部中断信号送至MCU(微处理器)的INT1端以使MCU产生中断响应,此时,MCU开始读取FIFO中的语音数据,然后转存到DRAM之中,读取过程中还要查询EMP端的状态,以免FIFO读空。

与录音相同,放音时首先进行同样的初始化,然后发控制命令20H(采样频率为8.0 kHz)启动放音操作。MCU开始从DRAM中读取要播放的语音数据并写入FIFO中,当FIFO中的语音数据装满时,FUL引脚将变为高电平,并产生外部中断信号送至MCU的INTO端以使MCU产生中断响应,此时应停止向FIFO写入数据。

在MCU录、放音的过程中,可根据键盘指令向MSM9841发出暂停或停止命令,以暂停或结束录、放音操作。同时利用液晶显示器来显示当前正在执行的操作及操作结果。通过键盘和液晶进行人机交流可方便的实现多段语音的录放操作以及音量调节等功能。

5 结束语

基于MSM9841的录放机在使用较为满意8kbps的比特率时,其录放音时间大约为34分钟。若需延长录放音时间,可对存储部分进行扩展。系统使用廉价的DRAM作为语音存储介质,因此成本较低。整机具有结构简单、性能可靠、人机交互界面友好、使用方便等一系列优点,因而具有较好的应用前景。如果将存储部分的DRAM换成FLASH或铁电存储器,该机还可被广泛地应用于公交车报站系统、录音电话、自动语音服务台等领域。

初始化完成之后即可发出控制命令10H(采样频率为8.0 kHz)来启动录音操作。在录音的过程中当FIFO中的语音数据超过FIFO存储空间一半时,MID引脚将变为高电平,并产生外部中断信号送至MCU(微处理器)的INT1端以使MCU产生中断响应,此时,MCU开始读取FIFO中的语音数据,然后转存到DRAM之中,读取过程中还要查询EMP端的状态,以免FIFO读空。

与录音相同,放音时首先进行同样的初始化,然后发控制命令20H(采样频率为8.0 kHz)启动放音操作。MCU开始从DRAM中读取要播放的语音数据并写入FIFO中,当FIFO中的语音数据装满时,FUL引脚将变为高电平,并产生外部中断信号送至MCU的INTO端以使MCU产生中断响应,此时应停止向FIFO写入数据。

在MCU录、放音的过程中,可根据键盘指令向MSM9841发出暂停或停止命令,以暂停或结束录、放音操作。同时利用液晶显示器来显示当前正在执行的操作及操作结果。通过键盘和液晶进行人机交流可方便的实现多段语音的录放操作以及音量调节等功能。

5 结束语

基于MSM9841的录放机在使用较为满意8kbps的比特率时,其录放音时间大约为34分钟。若需延长录放音时间,可对存储部分进行扩展。系统使用廉价的DRAM作为语音存储介质,因此成本较低。整机具有结构简单、性能可靠、人机交互界面友好、使用方便等一系列优点,因而具有较好的应用前景。如果将存储部分的DRAM换成FLASH或铁电存储器,该机还可被广泛地应用于公交车报站系统、录音电话、自动语音服务台等领域。

引用地址:单声道/立体声录放芯片MSM9841及其在数字语音录放机中的应用

2 引脚排列及功能

MSM9841的引脚排列如图1所示,各引脚的功能如下:

D15~D8:对于8 bit总线接口,这些管脚可以通过命令被定义到外部存储器的输入输出接口。否则,这些管脚只能定义为输入管脚。对于16 bit总线接口,这些管脚可用作外部存储器或微处理器的双向数据总线。

D7~D0:到外部存储器或微处理器的双向数据总线。

WR:写允许,低有效。

RD:读允许,低有效。

CS:读写功能允许,低有效(低电平时,允许读写功能操作)。

D/C:当该管脚为高电平时,语音数据可以从D0~D15引脚输入或输出。当该管脚为低电平时,D0~D7引脚用于输入控制命令或输出状态。

BUSY:当处于录音、回放、暂停状态时,该管脚输出低电平。

图2

EMP:当FIFO存储器中无数据时该管脚输出高电平,通过命令可使该管脚由高电平变为低电平。

MID:当FIFO中的数据超过FIFO存储空间的一半时,该管脚输出高电平。在回放期间,MID为高电平时开始语音合成。通过命令可使MID由高电平变成低电平。当不使用FIFO时,该管脚可为语音的输入/输出提供一个同步信号。

FUL/DREQR:当FIFO存储空间已满时,该管脚输出高电平。在回放期间,该管脚为高电平,FIFO中不能写入数据。FUL/DREQR输出的高电平可由命令输入来将其改变成低电平。当选择DMA转换和立体声回放时,DREQR输出高电平信号表示需要DMA转换。DREQR输出的高电平亦可由命令输入平将其改变成低电平。

CH/DACKR:当选择立体声回放且CH为高电平时,EMP、MID或FUL管脚输出右移FIFO的状态。当CH为低电平时,EMP、MID或FUL管脚输出左移FIFO的状态。在录音和单声道回放时需将该管脚设置为低电平。当选择DMA转换和立体声回放时,该管脚为DACKR功能。在这种情况下,输入DMA转换应答信号到DACKR。当DACKR为低电平时,IOW信号被接受。DACKR输出的低电平可由命令输入来将其改变成高电平。

DREQL:当选择DMA转换和立体声回放时,DREQL输出高电平表示需要DMA转换。DREQL输出的高电平可由命令输入来将其改变成低电平。

DACKL:当DMA控制器允许DMA转换时,可输入一个信号到DACKL端。如果DACKL为低电平,IOW和IOR信号将被接受。当选择立体声回放时,可给DACKL端输入左移FIFO的DMA转换应答信号。DACKL端的低电平可由命令输入将其改变成高电平。如果不使用DMA转换,应将该脚置为高电平。

IOW:在DMA转换时,该管脚为将外部数据写入MSM9841的写脉冲输入管脚。如果不使用DMA转换,将该引脚置为高电平。

IOR:在DMA转换时,该管脚可作为MSM9841的读脉冲输入管脚。如果不使用DMA转换,应将该引脚置为高电平。

图3

ADSD:当使用外部ADC时,该管脚为16bit串行数据输入管脚,如果不使用外部ADC,则应将该引脚置为低电平。

DASD:当使用外部DAC时,该管脚为16 bit串行数据输出管脚。

SIOCK:当使用外部ADC或DAC时,该管脚为16 bit串行数据输入/输出的同步时钟管脚。

XT,XT:外部振荡器连接管脚,当使用外部时钟时,可将外部时钟输入到该管脚。

VCK:录音和回放时的输出采样频率。当用外部ADC或DAC时,VCK管脚的信号被用作同步信号。

RESET:复位管脚,低有效。

TESTO、TESTI:测试管脚,将该引脚置为低电平。

SG:模拟地输出管脚。

MIN,LIN:内部OP放大器的反相输入端,同相输入端内部已连到信号地。

MOUT,LOUT:MOUT为内部放大器到MIN的输出端,LOUT为内部放大器到LIN的输出端。

AOUTL:内部LPF(低通滤波器)左路模拟信号输出端。它是回放信号波形输出端,将该管脚连到放大器后可驱动扬声器。

AOUTR:内部LPF(低通滤波器)右路模拟信号输出端。它是回放信号波形输出端,将该管脚连到放大器后可驱动扬声器。

DVDD:数字电源。在该管脚和数字地之间应接一个0.1μF电容。

DGND,AGND:数字地和模拟地。

AVDD:模拟电源。在该管脚和模拟地之间应接一个0.1μF电容。

2 引脚排列及功能

MSM9841的引脚排列如图1所示,各引脚的功能如下:

D15~D8:对于8 bit总线接口,这些管脚可以通过命令被定义到外部存储器的输入输出接口。否则,这些管脚只能定义为输入管脚。对于16 bit总线接口,这些管脚可用作外部存储器或微处理器的双向数据总线。

D7~D0:到外部存储器或微处理器的双向数据总线。

WR:写允许,低有效。

RD:读允许,低有效。

CS:读写功能允许,低有效(低电平时,允许读写功能操作)。

D/C:当该管脚为高电平时,语音数据可以从D0~D15引脚输入或输出。当该管脚为低电平时,D0~D7引脚用于输入控制命令或输出状态。

BUSY:当处于录音、回放、暂停状态时,该管脚输出低电平。

图2

EMP:当FIFO存储器中无数据时该管脚输出高电平,通过命令可使该管脚由高电平变为低电平。

MID:当FIFO中的数据超过FIFO存储空间的一半时,该管脚输出高电平。在回放期间,MID为高电平时开始语音合成。通过命令可使MID由高电平变成低电平。当不使用FIFO时,该管脚可为语音的输入/输出提供一个同步信号。

FUL/DREQR:当FIFO存储空间已满时,该管脚输出高电平。在回放期间,该管脚为高电平,FIFO中不能写入数据。FUL/DREQR输出的高电平可由命令输入来将其改变成低电平。当选择DMA转换和立体声回放时,DREQR输出高电平信号表示需要DMA转换。DREQR输出的高电平亦可由命令输入平将其改变成低电平。

CH/DACKR:当选择立体声回放且CH为高电平时,EMP、MID或FUL管脚输出右移FIFO的状态。当CH为低电平时,EMP、MID或FUL管脚输出左移FIFO的状态。在录音和单声道回放时需将该管脚设置为低电平。当选择DMA转换和立体声回放时,该管脚为DACKR功能。在这种情况下,输入DMA转换应答信号到DACKR。当DACKR为低电平时,IOW信号被接受。DACKR输出的低电平可由命令输入来将其改变成高电平。

DREQL:当选择DMA转换和立体声回放时,DREQL输出高电平表示需要DMA转换。DREQL输出的高电平可由命令输入来将其改变成低电平。

DACKL:当DMA控制器允许DMA转换时,可输入一个信号到DACKL端。如果DACKL为低电平,IOW和IOR信号将被接受。当选择立体声回放时,可给DACKL端输入左移FIFO的DMA转换应答信号。DACKL端的低电平可由命令输入将其改变成高电平。如果不使用DMA转换,应将该脚置为高电平。

IOW:在DMA转换时,该管脚为将外部数据写入MSM9841的写脉冲输入管脚。如果不使用DMA转换,将该引脚置为高电平。

IOR:在DMA转换时,该管脚可作为MSM9841的读脉冲输入管脚。如果不使用DMA转换,应将该引脚置为高电平。

图3

ADSD:当使用外部ADC时,该管脚为16bit串行数据输入管脚,如果不使用外部ADC,则应将该引脚置为低电平。

DASD:当使用外部DAC时,该管脚为16 bit串行数据输出管脚。

SIOCK:当使用外部ADC或DAC时,该管脚为16 bit串行数据输入/输出的同步时钟管脚。

XT,XT:外部振荡器连接管脚,当使用外部时钟时,可将外部时钟输入到该管脚。

VCK:录音和回放时的输出采样频率。当用外部ADC或DAC时,VCK管脚的信号被用作同步信号。

RESET:复位管脚,低有效。

TESTO、TESTI:测试管脚,将该引脚置为低电平。

SG:模拟地输出管脚。

MIN,LIN:内部OP放大器的反相输入端,同相输入端内部已连到信号地。

MOUT,LOUT:MOUT为内部放大器到MIN的输出端,LOUT为内部放大器到LIN的输出端。

AOUTL:内部LPF(低通滤波器)左路模拟信号输出端。它是回放信号波形输出端,将该管脚连到放大器后可驱动扬声器。

AOUTR:内部LPF(低通滤波器)右路模拟信号输出端。它是回放信号波形输出端,将该管脚连到放大器后可驱动扬声器。

DVDD:数字电源。在该管脚和数字地之间应接一个0.1μF电容。

DGND,AGND:数字地和模拟地。

AVDD:模拟电源。在该管脚和模拟地之间应接一个0.1μF电容。

3 内部结构及工作原理

MSM9841的内部结构如图2所示,它主要由微处理器、定时控制器、音量控制器、ADPCM2/ADPCM/PCM分析器、ADPCM2/ADPCM/PCM/非线性PCM合成器、直接存储器访问接口、FIFO、ADC、DAC、LPF等部件构成。

对MSM9841可采用二进制编码命令进行控制,从而完成录音、回放、停止、暂停、音量调节、DMA转换、设置使用内部或外部D/A、A/D、信号输出模式选择等功能。该控制命令的长度为8bit。

4 以MSM9841为核心的录放机

基于MSM9841的录放机电路如图3所示,该录放机采用双CPU模式,以单片机AT89C52作为录放音模块的主控单元。键盘和液晶显示模块以AT89C2051作为主控单元,通过串口与录放音模块变换指令与数据。由于本录放机未采用DMA方式,故MSM9841的DMA控制管脚均接高电平。MSM9841中D/C管脚的电平高低可决定数据总线上的数据类型。当D/C为低电平时,数据总线上的信号为系统控制命令;当D/C为高电平时,总线上的信号为语音数据。由于AT89C52是8位单片机,而MSM9841支持16位或8位数据总线,所以,在系统工作时,首先要利用MSM9841的控制命令将其设置为8位数据总线模式。

录放机音频输出端采用音频功率放大器LM386,其电路连接如图4所示。当电源电压为+5V时,LM386输出功率为300mW左右。MSM9841内部有2个运算放大器,可用于放大麦克风的语音信号,每个运算放大器对外提供反向输入端和输出端,而同向输入端则在芯片内部与模拟地相连。两个运算放大器可以级连,通过调节外部电阻阻值即可获得所需的放大倍数。通过下式可调节VLO,以使其处于LOUT管脚所允许的电压范围内:

VLO=(R4/R3)VMO=(R2R4/R1R3)VIN(V)

当供电电压为5V时,LOUT引脚所允许的电压范围为1~4V.LOUT管脚在芯片内部与输入低通滤波器相连,可用于去掉超过1/2采样频率的输入频率分量。这样,就可满足数据采样系统所适用的奈奎斯特定理,然后送ADC进行数据采样。放大电路通过隔直电容与麦克风相连,隔直电容主要用于去掉低电平交流信号(约2~20mV)中的直流信号。整个音频输入电路如图5所示。

整个刻录机系统采用4片2M%26;#215;8 bit的DRAM MSM5116800作为语音存储介质,在较高质量的8kbps的采样速率下,若采用4 bit的ADPCM2算法,4片MSM5116800能够记录的语音长度大约是4%26;#215;1.024%26;#215;2000%26;#215;8/(8%26;#215;4)=2048s。2M%26;#215;8 bit的DRAM的地址总线共20位,分为高位地址(即A0~A8和A9R~A11R共12位构成行地址Row address)和低位地址(即A0~A8共9位构成的列地址Column address),两者通过分时复用共用9根地址线A0~A8,每片DRAM的寻址范围为000000H~7FFFFFH,各片DRAM通过不同的CAS信号线来区别。DRAM有多种不同的读写模式和存储单元数据刷新模式,在本系统中,由于所需要的数据率非常低,所以可采用最基本的读写模式,即先发送完整的地址信号(包括行地址和列地址),然后读写;而刷新模式则采用cas-before-ras方式,并将刷新脉冲穿插到读写时序中间。

该系统通过接收键盘指令来完成录放音的操作。录音时,首先利用二进制命令对MSM9841进行初始化,具体内容包括:设置语音合成方式为4 bit的ADPCM2算法;选择采用内部ADC;设置总线宽度为8位;不采用DMA方式;配置FIFO的大小,FIFO最大可配置为1024 bit;设置输出数据的模式;设定采样频率为8.0 kHz。此采样频率可使语音音质大大优于电话的音质。提高采样频率还可使音质进一步得到改善,但录音时间也就相应缩短;反之,较低的采样频率会增加录音时间,但会降低音质。

3 内部结构及工作原理

MSM9841的内部结构如图2所示,它主要由微处理器、定时控制器、音量控制器、ADPCM2/ADPCM/PCM分析器、ADPCM2/ADPCM/PCM/非线性PCM合成器、直接存储器访问接口、FIFO、ADC、DAC、LPF等部件构成。

对MSM9841可采用二进制编码命令进行控制,从而完成录音、回放、停止、暂停、音量调节、DMA转换、设置使用内部或外部D/A、A/D、信号输出模式选择等功能。该控制命令的长度为8bit。

4 以MSM9841为核心的录放机

基于MSM9841的录放机电路如图3所示,该录放机采用双CPU模式,以单片机AT89C52作为录放音模块的主控单元。键盘和液晶显示模块以AT89C2051作为主控单元,通过串口与录放音模块变换指令与数据。由于本录放机未采用DMA方式,故MSM9841的DMA控制管脚均接高电平。MSM9841中D/C管脚的电平高低可决定数据总线上的数据类型。当D/C为低电平时,数据总线上的信号为系统控制命令;当D/C为高电平时,总线上的信号为语音数据。由于AT89C52是8位单片机,而MSM9841支持16位或8位数据总线,所以,在系统工作时,首先要利用MSM9841的控制命令将其设置为8位数据总线模式。

录放机音频输出端采用音频功率放大器LM386,其电路连接如图4所示。当电源电压为+5V时,LM386输出功率为300mW左右。MSM9841内部有2个运算放大器,可用于放大麦克风的语音信号,每个运算放大器对外提供反向输入端和输出端,而同向输入端则在芯片内部与模拟地相连。两个运算放大器可以级连,通过调节外部电阻阻值即可获得所需的放大倍数。通过下式可调节VLO,以使其处于LOUT管脚所允许的电压范围内:

VLO=(R4/R3)VMO=(R2R4/R1R3)VIN(V)

当供电电压为5V时,LOUT引脚所允许的电压范围为1~4V.LOUT管脚在芯片内部与输入低通滤波器相连,可用于去掉超过1/2采样频率的输入频率分量。这样,就可满足数据采样系统所适用的奈奎斯特定理,然后送ADC进行数据采样。放大电路通过隔直电容与麦克风相连,隔直电容主要用于去掉低电平交流信号(约2~20mV)中的直流信号。整个音频输入电路如图5所示。

整个刻录机系统采用4片2M%26;#215;8 bit的DRAM MSM5116800作为语音存储介质,在较高质量的8kbps的采样速率下,若采用4 bit的ADPCM2算法,4片MSM5116800能够记录的语音长度大约是4%26;#215;1.024%26;#215;2000%26;#215;8/(8%26;#215;4)=2048s。2M%26;#215;8 bit的DRAM的地址总线共20位,分为高位地址(即A0~A8和A9R~A11R共12位构成行地址Row address)和低位地址(即A0~A8共9位构成的列地址Column address),两者通过分时复用共用9根地址线A0~A8,每片DRAM的寻址范围为000000H~7FFFFFH,各片DRAM通过不同的CAS信号线来区别。DRAM有多种不同的读写模式和存储单元数据刷新模式,在本系统中,由于所需要的数据率非常低,所以可采用最基本的读写模式,即先发送完整的地址信号(包括行地址和列地址),然后读写;而刷新模式则采用cas-before-ras方式,并将刷新脉冲穿插到读写时序中间。

该系统通过接收键盘指令来完成录放音的操作。录音时,首先利用二进制命令对MSM9841进行初始化,具体内容包括:设置语音合成方式为4 bit的ADPCM2算法;选择采用内部ADC;设置总线宽度为8位;不采用DMA方式;配置FIFO的大小,FIFO最大可配置为1024 bit;设置输出数据的模式;设定采样频率为8.0 kHz。此采样频率可使语音音质大大优于电话的音质。提高采样频率还可使音质进一步得到改善,但录音时间也就相应缩短;反之,较低的采样频率会增加录音时间,但会降低音质。

初始化完成之后即可发出控制命令10H(采样频率为8.0 kHz)来启动录音操作。在录音的过程中当FIFO中的语音数据超过FIFO存储空间一半时,MID引脚将变为高电平,并产生外部中断信号送至MCU(微处理器)的INT1端以使MCU产生中断响应,此时,MCU开始读取FIFO中的语音数据,然后转存到DRAM之中,读取过程中还要查询EMP端的状态,以免FIFO读空。

与录音相同,放音时首先进行同样的初始化,然后发控制命令20H(采样频率为8.0 kHz)启动放音操作。MCU开始从DRAM中读取要播放的语音数据并写入FIFO中,当FIFO中的语音数据装满时,FUL引脚将变为高电平,并产生外部中断信号送至MCU的INTO端以使MCU产生中断响应,此时应停止向FIFO写入数据。

在MCU录、放音的过程中,可根据键盘指令向MSM9841发出暂停或停止命令,以暂停或结束录、放音操作。同时利用液晶显示器来显示当前正在执行的操作及操作结果。通过键盘和液晶进行人机交流可方便的实现多段语音的录放操作以及音量调节等功能。

5 结束语

基于MSM9841的录放机在使用较为满意8kbps的比特率时,其录放音时间大约为34分钟。若需延长录放音时间,可对存储部分进行扩展。系统使用廉价的DRAM作为语音存储介质,因此成本较低。整机具有结构简单、性能可靠、人机交互界面友好、使用方便等一系列优点,因而具有较好的应用前景。如果将存储部分的DRAM换成FLASH或铁电存储器,该机还可被广泛地应用于公交车报站系统、录音电话、自动语音服务台等领域。

初始化完成之后即可发出控制命令10H(采样频率为8.0 kHz)来启动录音操作。在录音的过程中当FIFO中的语音数据超过FIFO存储空间一半时,MID引脚将变为高电平,并产生外部中断信号送至MCU(微处理器)的INT1端以使MCU产生中断响应,此时,MCU开始读取FIFO中的语音数据,然后转存到DRAM之中,读取过程中还要查询EMP端的状态,以免FIFO读空。

与录音相同,放音时首先进行同样的初始化,然后发控制命令20H(采样频率为8.0 kHz)启动放音操作。MCU开始从DRAM中读取要播放的语音数据并写入FIFO中,当FIFO中的语音数据装满时,FUL引脚将变为高电平,并产生外部中断信号送至MCU的INTO端以使MCU产生中断响应,此时应停止向FIFO写入数据。

在MCU录、放音的过程中,可根据键盘指令向MSM9841发出暂停或停止命令,以暂停或结束录、放音操作。同时利用液晶显示器来显示当前正在执行的操作及操作结果。通过键盘和液晶进行人机交流可方便的实现多段语音的录放操作以及音量调节等功能。

5 结束语

基于MSM9841的录放机在使用较为满意8kbps的比特率时,其录放音时间大约为34分钟。若需延长录放音时间,可对存储部分进行扩展。系统使用廉价的DRAM作为语音存储介质,因此成本较低。整机具有结构简单、性能可靠、人机交互界面友好、使用方便等一系列优点,因而具有较好的应用前景。如果将存储部分的DRAM换成FLASH或铁电存储器,该机还可被广泛地应用于公交车报站系统、录音电话、自动语音服务台等领域。

上一篇:说话时能播放背景音乐的语音合成芯片SC-691

下一篇:集成编解码和语音录/放芯片ISD5216的应用

- 热门资源推荐

- 热门放大器推荐

小广播

热门活动

换一批

更多

最新手机便携文章

- 曝iPhone SE 4首发苹果自研5G基带:明年3月登场

- 曝iPhone 17全系首发3nm A19系列芯片:无缘台积电2nm工艺制程

- 供应链称上游元器件要大降价:国产手机现涨价潮后会主动下调售价吗

- 消息称苹果将拿出近 1 亿美元用于解除印尼 iPhone 16 系列销售禁令

- 消息称塔塔公司收购和硕在印度的唯一一家iPhone工厂,深化与苹果合作

- 苹果遭4000万英国iCloud用户集体诉讼,面临276亿元索赔

- 消息称苹果、三星超薄高密度电池均开发失败,iPhone 17 Air、Galaxy S25 Slim手机“变厚”

- 美光亮相2024年进博会,持续深耕中国市场,引领可持续发展

- Qorvo:创新技术引领下一代移动产业

更多精选电路图

更多热门文章

更多每日新闻

- USB Type-C® 和 USB Power Delivery:专为扩展功率范围和电池供电型系统而设计

- 景昱医疗耿东:脑机接口DBS治疗技术已实现国产替代

- 首都医科大学王长明:针对癫痫的数字疗法已进入使用阶段

- 非常见问题解答第223期:如何在没有软启动方程的情况下测量和确定软启动时序?

- 兆易创新GD25/55全系列车规级SPI NOR Flash荣获ISO 26262 ASIL D功能安全认证证书

- 新型IsoVu™ 隔离电流探头:为电流测量带来全新维度

- 英飞凌推出简化电机控制开发的ModusToolbox™电机套件

- 意法半导体IO-Link执行器电路板为工业监控和设备厂商带来一站式参考设计

- Melexis采用无磁芯技术缩小电流感测装置尺寸

- 千丘智能侍淳博:用数字疗法,点亮“孤独症”儿童的光

更多往期活动

11月22日历史上的今天

厂商技术中心

LM1877M-9/NOPB

LM1877M-9/NOPB

京公网安备 11010802033920号

京公网安备 11010802033920号