摘要:介绍了一种基于FPCA技术的视频压缩IPcore(Intellectual Property core,智力产权)设计。设计中综合运用了分布式算法、并行运算和流水线单元,通过VerilogHDL(Veriog Hardware DescdPtionLanSuage)硬件描述语言描述运算单元及其结构配置。整个系统能在27MHz系统时钟下工作。

关键词:视频压缩 IPcore FPCA

现行的视频压缩标准有多种,但基本属于以下两大类:视频会议标准和多媒体标准。视频会议标准包括ITU(Intemational Telecommunication Union)的H.263/H.261等。这些标准主要采用了基于DCT(离散余弦变换)编码、运动补偿等技术,使视频流能以Nx64kbps(N=1~32)的速率传输。

多媒体压缩标准主要包括:MPEG-1、MPEG-2、MPEG-4等,由CCITT和ISO的动态图像专家组(MotionPicture Experts Group)制定。MPEG-1主要应用在以CD-ROM为介质的视频上,比特率为1.5Mbps。MPEG-2应用在NTSC/PAL和CCIR601中, 比特率为2~10Mbps。MPEG—1和MPEG—2的目的都是有效传输和存储音视频。而MPEG-4是为了提供更有效的视频压缩,基于内容提供广泛的接人方式。它既可以在5-64kbps的移动电话和公共交换网中应用,也可以在4Mbps带宽的电视中应用。

JPEG(Joint Photographic Experts Group)标准是一个适用范围广泛的通用标准,由联合图像专家小组制定。它不仅适用于静止图像的压缩,也适用于电视图像序列的帧内图像的压缩[1]。

近年来,随着FPGA技术的日益成熟,愈来愈多的曾使用软件或DSP实现的复杂数字算法开始使用PPCA完成。这当然是由于FPGA的特殊结构和特性,使它可以更加高速和高效地完成这些算法。IPcore技术可以把这些FPGA中的算法设计封装成包(模块)。这些包具有智力产权,可以被继承、共享或购买。

1 视频压缩原理和算法实现

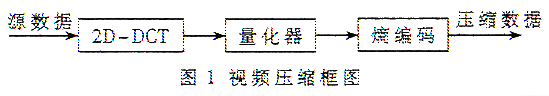

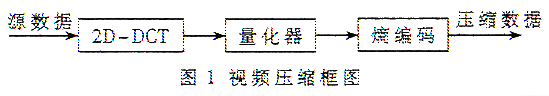

视频压缩技术主要利用图像信号的相关、冗余等特性,通过一些变换算法,保留对人眼视觉最重要的部分,进行编码传输。大部分视频压缩利用2D-DCT(二维离散余弦变换)和2D-IDCT(二维反离散余弦变换)变换得到图像的频谱,高精度保留对人眼重要的高频部分,低精度保留低频部分从而对视频流进行压缩[1]。其过程如图1所示。

JPEG(Joint Photographic Experts Group)标准是一个适用范围广泛的通用标准,由联合图像专家小组制定。它不仅适用于静止图像的压缩,也适用于电视图像序列的帧内图像的压缩[1]。

近年来,随着FPGA技术的日益成熟,愈来愈多的曾使用软件或DSP实现的复杂数字算法开始使用PPCA完成。这当然是由于FPGA的特殊结构和特性,使它可以更加高速和高效地完成这些算法。IPcore技术可以把这些FPGA中的算法设计封装成包(模块)。这些包具有智力产权,可以被继承、共享或购买。

1 视频压缩原理和算法实现

视频压缩技术主要利用图像信号的相关、冗余等特性,通过一些变换算法,保留对人眼视觉最重要的部分,进行编码传输。大部分视频压缩利用2D-DCT(二维离散余弦变换)和2D-IDCT(二维反离散余弦变换)变换得到图像的频谱,高精度保留对人眼重要的高频部分,低精度保留低频部分从而对视频流进行压缩[1]。其过程如图1所示。

1.1 DCT变换算法

2D-DCT变换是视频压缩中的常用变换[2]。在压缩过程中,将一幅图像分成许多8x8的小块进行变换。

8x8的2D-DCT变换如公式(1)所示:

1.1 DCT变换算法

2D-DCT变换是视频压缩中的常用变换[2]。在压缩过程中,将一幅图像分成许多8x8的小块进行变换。

8x8的2D-DCT变换如公式(1)所示:

如果直接使用公式(1)进行2D-DCT变换,运算量将会十分巨大,普通FPGA很难有效完成整个视频压缩运算。所以需要先把2D-DCT运算进行一些变换,简化计算,减少运算量。

如果直接使用公式(1)进行2D-DCT变换,运算量将会十分巨大,普通FPGA很难有效完成整个视频压缩运算。所以需要先把2D-DCT运算进行一些变换,简化计算,减少运算量。

2D-DCT具有正交可分解性闷,可以通过对输入的矩阵先做一维行变换,再做一维列变换实现。即将8x8数据先按行方向进行累加运算,产生中间矩阵,再对中间矩阵按列方向进行累加运算,最后得到变换结果。2D-DCT可以分解成两个1D-DCT运算,见公式(2)。

将公式(2)展开成矩阵形式,得到公式(3)。计算一个这样的单元需要64个乘法器和56个加法器,运算量还是很大。利用公式(3)的对称性进行变换,可以得到公式(4),使乘法器减少到32个,加法器减少到8个。

2D-DCT具有正交可分解性闷,可以通过对输入的矩阵先做一维行变换,再做一维列变换实现。即将8x8数据先按行方向进行累加运算,产生中间矩阵,再对中间矩阵按列方向进行累加运算,最后得到变换结果。2D-DCT可以分解成两个1D-DCT运算,见公式(2)。

将公式(2)展开成矩阵形式,得到公式(3)。计算一个这样的单元需要64个乘法器和56个加法器,运算量还是很大。利用公式(3)的对称性进行变换,可以得到公式(4),使乘法器减少到32个,加法器减少到8个。

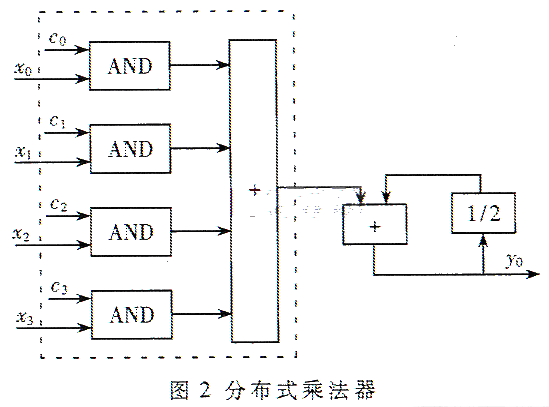

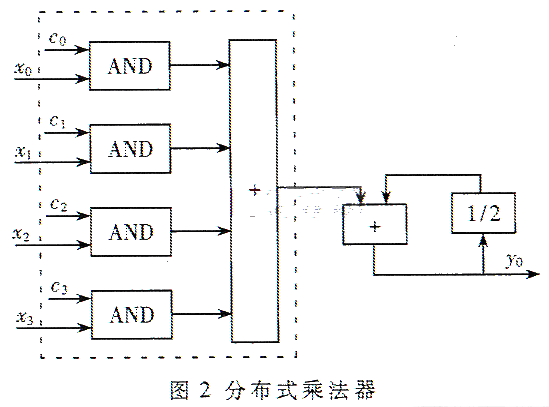

一个由公式(4)推演出的分布式乘法器如图2所示。4个乘数(x0…x3)同时与各自的系数(c0…c3)相与,然后相加得到一个和数,这个和数与除2器出来的数相加,得到一个新的累计数。这个新的累加数如果是最后的结果,则输出;如果不是,送入除2器,进行下一步累加。这样,分布式乘法器就可以完成系数yj的运算。

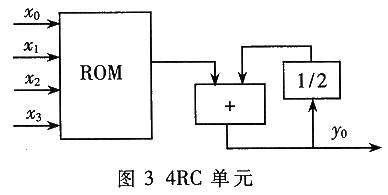

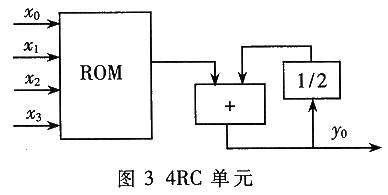

由于DCT运算中的系数Cm是常数,对于拥有RAM单元的FPGA,上述运算也可以使用查ROM表的方法实现。将图2中的虚线内部分,改换ROM单元,如图3所示。这时,(x0…x3)作为ROM表的地址位,通过查表的方式输出和数,进行累加运算。ROM表的地址位宽度为4,存储单元数量DW=24=16。一些生产商提供的综合软件带有IP库,可以调用这些IP库中的ROM模块实现ROM表。例如ALTERA公司的Megafunction Library中的LPM_ROM可以用以下的语句调用(VerilogHDL)[4]。用VC或MATLAB生成一个.mif的ROM表文件。

LPM_ROM U1(

.address(adr),

.inclock(clk),

.q(dat));

defparaln

lpm_rom_component.lpm_width=16,

lpm_rom_component.lpm_widthad=4,

lpm_rom_component.1pm_address_control

="REGISTERED",

lpm_rom_component.ipm_outdata

="UNREGISTERED",

lpm_rom_component.1pm_file="romtable.mif";

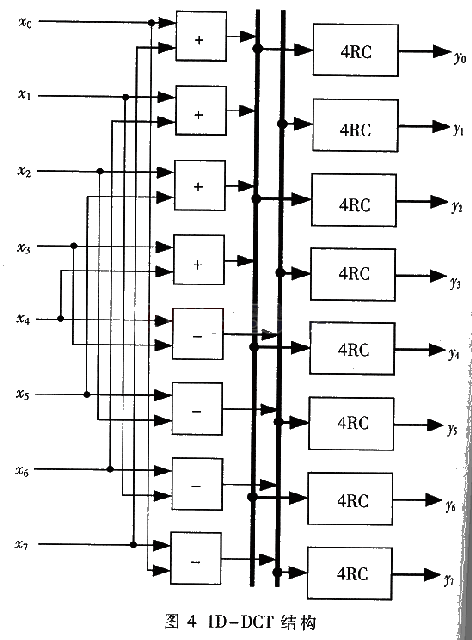

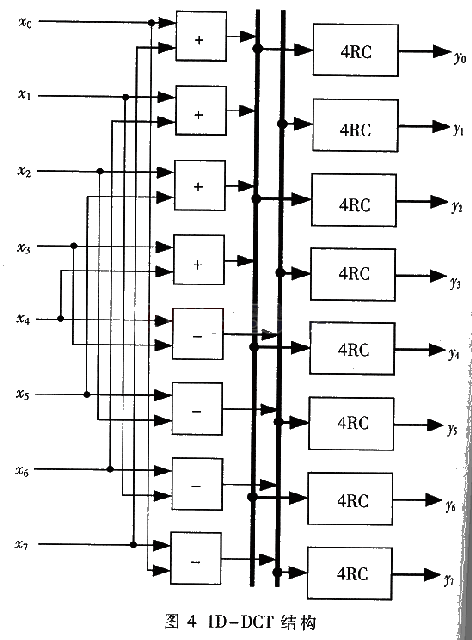

这样,可以得到由这些基本单元构成与矩阵公式(4)相对的1D-DCT的FPGA设计,如图4所示。其中4RC单元表示图3的结构。

一个由公式(4)推演出的分布式乘法器如图2所示。4个乘数(x0…x3)同时与各自的系数(c0…c3)相与,然后相加得到一个和数,这个和数与除2器出来的数相加,得到一个新的累计数。这个新的累加数如果是最后的结果,则输出;如果不是,送入除2器,进行下一步累加。这样,分布式乘法器就可以完成系数yj的运算。

由于DCT运算中的系数Cm是常数,对于拥有RAM单元的FPGA,上述运算也可以使用查ROM表的方法实现。将图2中的虚线内部分,改换ROM单元,如图3所示。这时,(x0…x3)作为ROM表的地址位,通过查表的方式输出和数,进行累加运算。ROM表的地址位宽度为4,存储单元数量DW=24=16。一些生产商提供的综合软件带有IP库,可以调用这些IP库中的ROM模块实现ROM表。例如ALTERA公司的Megafunction Library中的LPM_ROM可以用以下的语句调用(VerilogHDL)[4]。用VC或MATLAB生成一个.mif的ROM表文件。

LPM_ROM U1(

.address(adr),

.inclock(clk),

.q(dat));

defparaln

lpm_rom_component.lpm_width=16,

lpm_rom_component.lpm_widthad=4,

lpm_rom_component.1pm_address_control

="REGISTERED",

lpm_rom_component.ipm_outdata

="UNREGISTERED",

lpm_rom_component.1pm_file="romtable.mif";

这样,可以得到由这些基本单元构成与矩阵公式(4)相对的1D-DCT的FPGA设计,如图4所示。其中4RC单元表示图3的结构。

如前所述,2D-DCT需要两个1D-DCT共同完成,但是两个1D-DCT运算的中间变量并不是直接传递的,而需要一个矩阵转置模块进行耦合。

1.2 转置RAM

2D-DCT单元由两个相同的1D-DCT和转置RAM等组成,如图5所示。根据公式(2),可以知道1D-DCT先对8x8单元的行进行累加操作,把得到的结果暂存到RAM中,直到8行都运算完成。RAM中的临时8x8矩阵要先转置,把列数据变成行数据,经并串转换后输入到第2个1D-DCT进行行累加。

转置RAM是一个8x8的RAM阵列。当数据完成1D-DCT变换后,即由xij到zjl变换,按行顺序输入到转置RAM,在读出时按列顺序读出,这样完成zil到zli的变换;然后将z9并串转换,输入到第二个1D-DCT,由zli运算得到ylk。这样就完成了公式(1)的2D-DCT整个变换,如图6所示。

1.3 2D-IDCT

2D-IDCT变换如公式(5)所示。

如前所述,2D-DCT需要两个1D-DCT共同完成,但是两个1D-DCT运算的中间变量并不是直接传递的,而需要一个矩阵转置模块进行耦合。

1.2 转置RAM

2D-DCT单元由两个相同的1D-DCT和转置RAM等组成,如图5所示。根据公式(2),可以知道1D-DCT先对8x8单元的行进行累加操作,把得到的结果暂存到RAM中,直到8行都运算完成。RAM中的临时8x8矩阵要先转置,把列数据变成行数据,经并串转换后输入到第2个1D-DCT进行行累加。

转置RAM是一个8x8的RAM阵列。当数据完成1D-DCT变换后,即由xij到zjl变换,按行顺序输入到转置RAM,在读出时按列顺序读出,这样完成zil到zli的变换;然后将z9并串转换,输入到第二个1D-DCT,由zli运算得到ylk。这样就完成了公式(1)的2D-DCT整个变换,如图6所示。

1.3 2D-IDCT

2D-IDCT变换如公式(5)所示。

可见公式(5)与公式(1)相同,所以2D-IDCT可以用与2D-DCT的同样方法实现。

1.4 量化,编码

量化算法包括一张量化表,它因人眼对各种空间频率的灵敏度的不同而确定。在表中,较低空间频率的精度要高于较高频率的精度,这是由于人眼的低频分量比较敏感,而对高频分量不太敏感。

编码可以采用游程编码或熵编码。单元模块均可通过FPGA的片上RAM(满足双口RAM的特性)设计完成。

图6

2 结论

整个视频压缩IPcore设计可以在FPGA上实现,在27MHz的系统时钟下工作。根据具体芯片的不同,可以在更高的速率工作。压缩速率可以达到108Mbps。

实际应用中,数据字长对压缩效果和比率有较大影响,一般情况下系数Cm取12位,可以满足大部分的视频压缩要求。

整个视频压缩IPcore可以直接下载到FPGA上(例如EDIF格式),独立实现视频压缩功能,也可以通过软件设计与其他的IPcore协同工作。例如,在网络摄像机的应用上,可以把视频压缩IPcore、数字摄像头控制器、网络接口一起编译成新的核。这个核具有视频采

集、压缩、传输等一系列功能。把核的EDIF文件通过生产厂商的下载软件下载到FPGA上,就可以在一块芯片上实现所有网络摄像机的功能。实现了SoPC(System On a Programmable Chip)的目标。

可见公式(5)与公式(1)相同,所以2D-IDCT可以用与2D-DCT的同样方法实现。

1.4 量化,编码

量化算法包括一张量化表,它因人眼对各种空间频率的灵敏度的不同而确定。在表中,较低空间频率的精度要高于较高频率的精度,这是由于人眼的低频分量比较敏感,而对高频分量不太敏感。

编码可以采用游程编码或熵编码。单元模块均可通过FPGA的片上RAM(满足双口RAM的特性)设计完成。

图6

2 结论

整个视频压缩IPcore设计可以在FPGA上实现,在27MHz的系统时钟下工作。根据具体芯片的不同,可以在更高的速率工作。压缩速率可以达到108Mbps。

实际应用中,数据字长对压缩效果和比率有较大影响,一般情况下系数Cm取12位,可以满足大部分的视频压缩要求。

整个视频压缩IPcore可以直接下载到FPGA上(例如EDIF格式),独立实现视频压缩功能,也可以通过软件设计与其他的IPcore协同工作。例如,在网络摄像机的应用上,可以把视频压缩IPcore、数字摄像头控制器、网络接口一起编译成新的核。这个核具有视频采

集、压缩、传输等一系列功能。把核的EDIF文件通过生产厂商的下载软件下载到FPGA上,就可以在一块芯片上实现所有网络摄像机的功能。实现了SoPC(System On a Programmable Chip)的目标。

引用地址:视频压缩IPcore设计

JPEG(Joint Photographic Experts Group)标准是一个适用范围广泛的通用标准,由联合图像专家小组制定。它不仅适用于静止图像的压缩,也适用于电视图像序列的帧内图像的压缩[1]。

近年来,随着FPGA技术的日益成熟,愈来愈多的曾使用软件或DSP实现的复杂数字算法开始使用PPCA完成。这当然是由于FPGA的特殊结构和特性,使它可以更加高速和高效地完成这些算法。IPcore技术可以把这些FPGA中的算法设计封装成包(模块)。这些包具有智力产权,可以被继承、共享或购买。

1 视频压缩原理和算法实现

视频压缩技术主要利用图像信号的相关、冗余等特性,通过一些变换算法,保留对人眼视觉最重要的部分,进行编码传输。大部分视频压缩利用2D-DCT(二维离散余弦变换)和2D-IDCT(二维反离散余弦变换)变换得到图像的频谱,高精度保留对人眼重要的高频部分,低精度保留低频部分从而对视频流进行压缩[1]。其过程如图1所示。

JPEG(Joint Photographic Experts Group)标准是一个适用范围广泛的通用标准,由联合图像专家小组制定。它不仅适用于静止图像的压缩,也适用于电视图像序列的帧内图像的压缩[1]。

近年来,随着FPGA技术的日益成熟,愈来愈多的曾使用软件或DSP实现的复杂数字算法开始使用PPCA完成。这当然是由于FPGA的特殊结构和特性,使它可以更加高速和高效地完成这些算法。IPcore技术可以把这些FPGA中的算法设计封装成包(模块)。这些包具有智力产权,可以被继承、共享或购买。

1 视频压缩原理和算法实现

视频压缩技术主要利用图像信号的相关、冗余等特性,通过一些变换算法,保留对人眼视觉最重要的部分,进行编码传输。大部分视频压缩利用2D-DCT(二维离散余弦变换)和2D-IDCT(二维反离散余弦变换)变换得到图像的频谱,高精度保留对人眼重要的高频部分,低精度保留低频部分从而对视频流进行压缩[1]。其过程如图1所示。

1.1 DCT变换算法

2D-DCT变换是视频压缩中的常用变换[2]。在压缩过程中,将一幅图像分成许多8x8的小块进行变换。

8x8的2D-DCT变换如公式(1)所示:

1.1 DCT变换算法

2D-DCT变换是视频压缩中的常用变换[2]。在压缩过程中,将一幅图像分成许多8x8的小块进行变换。

8x8的2D-DCT变换如公式(1)所示:

如果直接使用公式(1)进行2D-DCT变换,运算量将会十分巨大,普通FPGA很难有效完成整个视频压缩运算。所以需要先把2D-DCT运算进行一些变换,简化计算,减少运算量。

如果直接使用公式(1)进行2D-DCT变换,运算量将会十分巨大,普通FPGA很难有效完成整个视频压缩运算。所以需要先把2D-DCT运算进行一些变换,简化计算,减少运算量。

2D-DCT具有正交可分解性闷,可以通过对输入的矩阵先做一维行变换,再做一维列变换实现。即将8x8数据先按行方向进行累加运算,产生中间矩阵,再对中间矩阵按列方向进行累加运算,最后得到变换结果。2D-DCT可以分解成两个1D-DCT运算,见公式(2)。

将公式(2)展开成矩阵形式,得到公式(3)。计算一个这样的单元需要64个乘法器和56个加法器,运算量还是很大。利用公式(3)的对称性进行变换,可以得到公式(4),使乘法器减少到32个,加法器减少到8个。

2D-DCT具有正交可分解性闷,可以通过对输入的矩阵先做一维行变换,再做一维列变换实现。即将8x8数据先按行方向进行累加运算,产生中间矩阵,再对中间矩阵按列方向进行累加运算,最后得到变换结果。2D-DCT可以分解成两个1D-DCT运算,见公式(2)。

将公式(2)展开成矩阵形式,得到公式(3)。计算一个这样的单元需要64个乘法器和56个加法器,运算量还是很大。利用公式(3)的对称性进行变换,可以得到公式(4),使乘法器减少到32个,加法器减少到8个。

一个由公式(4)推演出的分布式乘法器如图2所示。4个乘数(x0…x3)同时与各自的系数(c0…c3)相与,然后相加得到一个和数,这个和数与除2器出来的数相加,得到一个新的累计数。这个新的累加数如果是最后的结果,则输出;如果不是,送入除2器,进行下一步累加。这样,分布式乘法器就可以完成系数yj的运算。

由于DCT运算中的系数Cm是常数,对于拥有RAM单元的FPGA,上述运算也可以使用查ROM表的方法实现。将图2中的虚线内部分,改换ROM单元,如图3所示。这时,(x0…x3)作为ROM表的地址位,通过查表的方式输出和数,进行累加运算。ROM表的地址位宽度为4,存储单元数量DW=24=16。一些生产商提供的综合软件带有IP库,可以调用这些IP库中的ROM模块实现ROM表。例如ALTERA公司的Megafunction Library中的LPM_ROM可以用以下的语句调用(VerilogHDL)[4]。用VC或MATLAB生成一个.mif的ROM表文件。

LPM_ROM U1(

.address(adr),

.inclock(clk),

.q(dat));

defparaln

lpm_rom_component.lpm_width=16,

lpm_rom_component.lpm_widthad=4,

lpm_rom_component.1pm_address_control

="REGISTERED",

lpm_rom_component.ipm_outdata

="UNREGISTERED",

lpm_rom_component.1pm_file="romtable.mif";

这样,可以得到由这些基本单元构成与矩阵公式(4)相对的1D-DCT的FPGA设计,如图4所示。其中4RC单元表示图3的结构。

一个由公式(4)推演出的分布式乘法器如图2所示。4个乘数(x0…x3)同时与各自的系数(c0…c3)相与,然后相加得到一个和数,这个和数与除2器出来的数相加,得到一个新的累计数。这个新的累加数如果是最后的结果,则输出;如果不是,送入除2器,进行下一步累加。这样,分布式乘法器就可以完成系数yj的运算。

由于DCT运算中的系数Cm是常数,对于拥有RAM单元的FPGA,上述运算也可以使用查ROM表的方法实现。将图2中的虚线内部分,改换ROM单元,如图3所示。这时,(x0…x3)作为ROM表的地址位,通过查表的方式输出和数,进行累加运算。ROM表的地址位宽度为4,存储单元数量DW=24=16。一些生产商提供的综合软件带有IP库,可以调用这些IP库中的ROM模块实现ROM表。例如ALTERA公司的Megafunction Library中的LPM_ROM可以用以下的语句调用(VerilogHDL)[4]。用VC或MATLAB生成一个.mif的ROM表文件。

LPM_ROM U1(

.address(adr),

.inclock(clk),

.q(dat));

defparaln

lpm_rom_component.lpm_width=16,

lpm_rom_component.lpm_widthad=4,

lpm_rom_component.1pm_address_control

="REGISTERED",

lpm_rom_component.ipm_outdata

="UNREGISTERED",

lpm_rom_component.1pm_file="romtable.mif";

这样,可以得到由这些基本单元构成与矩阵公式(4)相对的1D-DCT的FPGA设计,如图4所示。其中4RC单元表示图3的结构。

如前所述,2D-DCT需要两个1D-DCT共同完成,但是两个1D-DCT运算的中间变量并不是直接传递的,而需要一个矩阵转置模块进行耦合。

1.2 转置RAM

2D-DCT单元由两个相同的1D-DCT和转置RAM等组成,如图5所示。根据公式(2),可以知道1D-DCT先对8x8单元的行进行累加操作,把得到的结果暂存到RAM中,直到8行都运算完成。RAM中的临时8x8矩阵要先转置,把列数据变成行数据,经并串转换后输入到第2个1D-DCT进行行累加。

转置RAM是一个8x8的RAM阵列。当数据完成1D-DCT变换后,即由xij到zjl变换,按行顺序输入到转置RAM,在读出时按列顺序读出,这样完成zil到zli的变换;然后将z9并串转换,输入到第二个1D-DCT,由zli运算得到ylk。这样就完成了公式(1)的2D-DCT整个变换,如图6所示。

1.3 2D-IDCT

2D-IDCT变换如公式(5)所示。

如前所述,2D-DCT需要两个1D-DCT共同完成,但是两个1D-DCT运算的中间变量并不是直接传递的,而需要一个矩阵转置模块进行耦合。

1.2 转置RAM

2D-DCT单元由两个相同的1D-DCT和转置RAM等组成,如图5所示。根据公式(2),可以知道1D-DCT先对8x8单元的行进行累加操作,把得到的结果暂存到RAM中,直到8行都运算完成。RAM中的临时8x8矩阵要先转置,把列数据变成行数据,经并串转换后输入到第2个1D-DCT进行行累加。

转置RAM是一个8x8的RAM阵列。当数据完成1D-DCT变换后,即由xij到zjl变换,按行顺序输入到转置RAM,在读出时按列顺序读出,这样完成zil到zli的变换;然后将z9并串转换,输入到第二个1D-DCT,由zli运算得到ylk。这样就完成了公式(1)的2D-DCT整个变换,如图6所示。

1.3 2D-IDCT

2D-IDCT变换如公式(5)所示。

可见公式(5)与公式(1)相同,所以2D-IDCT可以用与2D-DCT的同样方法实现。

1.4 量化,编码

量化算法包括一张量化表,它因人眼对各种空间频率的灵敏度的不同而确定。在表中,较低空间频率的精度要高于较高频率的精度,这是由于人眼的低频分量比较敏感,而对高频分量不太敏感。

编码可以采用游程编码或熵编码。单元模块均可通过FPGA的片上RAM(满足双口RAM的特性)设计完成。

图6

2 结论

整个视频压缩IPcore设计可以在FPGA上实现,在27MHz的系统时钟下工作。根据具体芯片的不同,可以在更高的速率工作。压缩速率可以达到108Mbps。

实际应用中,数据字长对压缩效果和比率有较大影响,一般情况下系数Cm取12位,可以满足大部分的视频压缩要求。

整个视频压缩IPcore可以直接下载到FPGA上(例如EDIF格式),独立实现视频压缩功能,也可以通过软件设计与其他的IPcore协同工作。例如,在网络摄像机的应用上,可以把视频压缩IPcore、数字摄像头控制器、网络接口一起编译成新的核。这个核具有视频采

集、压缩、传输等一系列功能。把核的EDIF文件通过生产厂商的下载软件下载到FPGA上,就可以在一块芯片上实现所有网络摄像机的功能。实现了SoPC(System On a Programmable Chip)的目标。

可见公式(5)与公式(1)相同,所以2D-IDCT可以用与2D-DCT的同样方法实现。

1.4 量化,编码

量化算法包括一张量化表,它因人眼对各种空间频率的灵敏度的不同而确定。在表中,较低空间频率的精度要高于较高频率的精度,这是由于人眼的低频分量比较敏感,而对高频分量不太敏感。

编码可以采用游程编码或熵编码。单元模块均可通过FPGA的片上RAM(满足双口RAM的特性)设计完成。

图6

2 结论

整个视频压缩IPcore设计可以在FPGA上实现,在27MHz的系统时钟下工作。根据具体芯片的不同,可以在更高的速率工作。压缩速率可以达到108Mbps。

实际应用中,数据字长对压缩效果和比率有较大影响,一般情况下系数Cm取12位,可以满足大部分的视频压缩要求。

整个视频压缩IPcore可以直接下载到FPGA上(例如EDIF格式),独立实现视频压缩功能,也可以通过软件设计与其他的IPcore协同工作。例如,在网络摄像机的应用上,可以把视频压缩IPcore、数字摄像头控制器、网络接口一起编译成新的核。这个核具有视频采

集、压缩、传输等一系列功能。把核的EDIF文件通过生产厂商的下载软件下载到FPGA上,就可以在一块芯片上实现所有网络摄像机的功能。实现了SoPC(System On a Programmable Chip)的目标。

上一篇:视频解码芯片CXA2075M

下一篇:ISD2560语音芯片在排队机系统中的应用

- 热门资源推荐

- 热门放大器推荐

小广播

热门活动

换一批

更多

最新手机便携文章

- 古尔曼称苹果明年推出 AirTag 2 追踪器:升级 UWB 超宽带芯片,精确定位范围提升 3 倍

- 消息称苹果自研再下一城:蓝牙+Wi-Fi芯片 2025年iPhone 17系列首发

- 苹果从iPhone 18 Pro开始将弃用高通5G芯片

- 印尼投资部长确认:苹果计划在当地投资10亿美元建造零部件工厂

- 消息称苹果有望2026下半年推出折叠iPhone,并重振折叠屏手机市场

- 华为麒麟9020/9030/9040处理器曝光:小步快跑 四大方面升级

- 汇顶超声波指纹方案助力iQOO Neo10流畅解锁体验

- 曝苹果自研5G基带性能弱于高通:iPhone信号问题无解

- 消息称 AMD 将入局手机芯片领域,采用台积电 3nm 工艺

更多开源项目推荐

- AD5933、12位、1 MSPS ADC,用于汽车传感器

- EVAL-SSM3582Z,用于评估 SSM3582/SSM3582A 2x、31.76 W、数字输入、无滤波器立体声 D 类音频放大器的评估套件

- LTC3409 的典型应用 - 采用 3mm-3mm DFN 的 600mA 低 VIN 降压稳压器

- NCP380HMU05AGEVB,笔记本USB开关评估板

- STEVAL-IKR002V4、SPIRIT1 868-MHz 低数据速率收发器开发套件

- 基于VIPer06XN的12V、140mA、30kHz非隔离降压拓扑稳压器

- LT1086CT 受保护的大电流灯驱动器的典型应用

- DIY点锡膏机

- LT3013B 的典型应用 - 具有 PWRGD 的 250mA、4V 至 80V 低压差微功率线性稳压器

- AD8627ARZ-REEL单极输出精密放大器典型应用电路

更多精选电路图

更多热门文章

更多每日新闻

- 微软领先科技巨头,成为英伟达Hopper芯片最大买家

- 芯启源(上海)将持续发力,“做深做精”EDA及IP产品

- 本田严厉警告日产:若与鸿海合作,那么本田与日产的合作将终止

- Microchip推出新款交钥匙电容式触摸控制器产品 MTCH2120

- Matter对AIoT的意义:连接AIoT设备开发人员指南

- 我国科学家建立生成式模型为医学AI训练提供技术支持

- Diodes 推出符合车用标准的电流分流监测器,通过高精度电压感测快速检测系统故障

- Power Integrations面向800V汽车应用推出新型宽爬电距离开关IC

- 打破台积电垄断!联电夺下高通先进封装订单

- Ampere 年度展望:2025年重塑IT格局的四大关键趋势

更多往期活动

厂商技术中心

Verilog HDL数字集成电路设计原理与应用

Verilog HDL数字集成电路设计原理与应用 TTLM4250CJ

TTLM4250CJ

京公网安备 11010802033920号

京公网安备 11010802033920号