为何采用视频滤波器?

视频频段中的任何干扰信号都将产生一些肉眼可见的显示失真问题,而采用视频滤波器就可以消除这些失真。信号混叠是采样视频系统中的一个明显失真。当超出视频频段范围的高频信号(例如外部无线发射信号或本地时钟信号)通过模数转换器的采样过程混叠回视频频段时,就会产生混叠现象。在模数转换器之前放置一个抗混叠滤波器就可防止这种失真。当利用数模转换器重建数字化的视频信号时,将导致视频信号在较高频率上被复制,从而也会引起图像失真。这类失真信号可通过在数模转换器之后加入一个视频滤波器来消除。

为何采用有源视频滤波器?

采用运算放大器实现的有源滤波器将比采用电感实现的无源滤波器频率响应更好、带宽更平坦,且通道间更匹配。无源滤波器的带宽和频率响应特征取决于组成它的电感和电容值的精度。而有源滤波器采用运算放大器和电阻器来替代电感器,由于有源滤波器的精度取决于电阻和电容值的精度,而不再取决于电感和电容值的精度,因此精度得到充分提高。另外值得一提的是,便宜的电阻比便宜的电感精度高得多。此外,现在运算放大器的价格也很低,因此一个有源滤波器往往比采用电感实现的无源滤波器更便宜。

设计有源视频滤波器

视频滤波器要求良好的相位线性特征,即在整个视频频段内都应具有十分恒定的相位延迟,同时幅度响应的平坦度要好。这两方面的参数要求使得Butterworth滤波器成为一个不错的选择。采用一个4阶滤波器就能在高频下获得很好的阻带抑制效果。

4阶Butterworth滤波器由两个运算放大器采用Sallen-Key方式构成。本文中的设计采用飞兆半导体的高速双运算放大器(FHP3230),来构造一个可放入狭小印刷电路板中的滤波器。FHP3230的增益带宽为60MHz,是一种采用单电源供电和轨至轨输出方式的

放大器。这些特点使FHP3230成为该类应用的最佳选择。

图1所示为一个4阶滤波器。

图1:采用FHP3230双运算放大器的有源视频滤波器(+5V单电源、AC耦合输入)

下面几段我们将讨论如何设置滤波器中各个元件的值。需注意的是,该滤波器工作在+5V单电源下,并假设输入信号采用AC耦合。如果输入DC电平偏置水平能与电源电压

和放大器的输入共模电压范围兼容,输入信号就可能采用DC耦合。

设计Butterworth有源视频滤波器

该滤波器有两级,每一级都由一个FHP3230运算放大器来实现(因此整个滤波器需要一个双运算放大器器件)。每级各提供两个极点,以构成完整的4阶滤波器。有很多种方法来选择这种滤波器的元件值。在本文的例子中,第一级为单位增益,Q值为0.54;第二级的增益为+2,Q值为1.3。这些Q值可形成一个Butterworth滤波器。为确保滤波器

在整个视频频段内的平坦性,取截止频率fo为6MHz。这将导致整个Butterworth波形

在5MHz频率时的增益为-1dB。

电容应足够大,这样PCB的寄生电容才不至于影响电容值。但电容也不能太大,否则电阻值将会很小,以致放大器将难以驱动如此小的电阻。PCB的寄生电容在短走线的情况下约为1pF(制造PCB的材料直接影响寄生电容大小)。如果以18pF作为电容元件的基本量级,我们就能将寄生电容的影响降到最低。

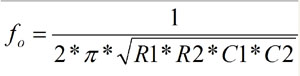

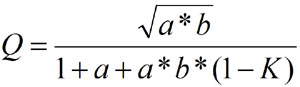

以下是一级Sallen-Key滤波器的转换函数:![]()

图1中每一滤波级的转换函数都可由上式表示,只需用额外的下标(a或b)来区分不同的

滤波级(例如将方程中R1替换成R1a或R1b等)。

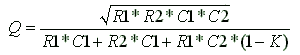

以下为转换函数中的一些关键参数:

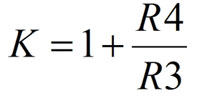

或K=1(对于第一级的情况)。

或K=1(对于第一级的情况)。

这些等式并不是最有效的形式。例如,已知fo和Q值,希望找出最佳的电阻值和电容值。目前有许多种电阻和电容值的不同组合方案可以定义滤波整形,为了简化选择,可以将电阻和电容表示成某个公共值的比例因子,即:R1=R×a、R2=R、C1=C和C2=C

×b。其中C=18pF。

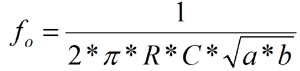

进行替换后,可以得到:

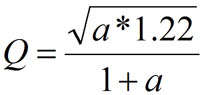

设计滤波器第一级

如果第一级中采用的电容值相同,而该级是单位增益级,因此最高Q值只能达到0.5。

又因为要求的Q值为0.54,所以第一级的电容绝对不能等值。这就需要选用一个大于18pF的标准电容,而22pF的电容就刚好符合要求。当然还有许多其它的电容值也十

分合适。这样,第一级的比例因子b为22/18(即1.22),而第一级的比例因子K为1,

从而可得:![]()

由于已知Q=0.54,则可从上式求解出a,得a=1.53。

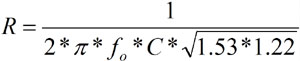

基于比例因子a,可从截止频率fo的等式中求解出R值:

将fo=6MHz代入上式,得到:R=1,079Ω、R1=1,650Ω、R2=1,079Ω。

最接近(1%)标准电阻的值为:R1=1.65kΩ、R2=1.07kΩ。

设计滤波器第二级

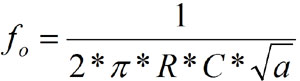

第二级放大器的增益为+2,因此可使用等值的电容(尽管其Q值更高)。假设C1=C2

=C=18pF,同样将电阻值表示为一个比例因子a,即:R1=R×a和R2=R。

可以得到:

由于已知第二级的Q=1.3,可从上式求解出a,得a=1.69。将fo=6MHz代入截止频

率fo的等式,解出R值:R=1,134Ω,R1=1,916Ω,R2=1,134Ω。最接近(1%)标

准电阻的值为:R1=1.91kΩ,R2=1.1kΩ。

调整有源滤波器以适应放大器增益带宽

从以上等式导出的元件值有一个问题,即它们都假设运算放大器的带宽是无限的(如果

存在这样的运算放大器,肯定会非常昂贵)。利用前面导出的元件值来构建滤波器电路,会发现该电路在0.6dB增益时出现峰值,而在增益为-3dB时带宽大约减少18%。因此,必须调整这些元件值,以补偿放大器中的相移延迟。所幸这一调整过程非常简单。

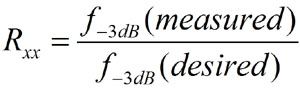

首先,测出构建的电路在-3dB下的带宽。然后,根据实际测量带宽与期望带宽之比,

调整全部四个滤波器电阻(R1a、R2a、R1b、R2b),即:

这里

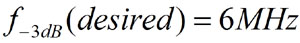

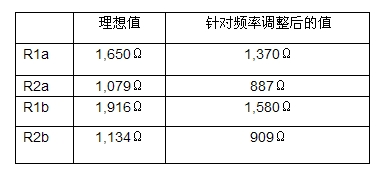

按这种方式调整电阻将改变滤波器频率,但对Q值不会有太大影响。表1为测量电路后

计算出的电阻值。

表1:测量电路后计算出的电阻值

将电路中的电阻变为根据电路计算出来的调整值(针对具体的电路,这些值可能会有差异)。改变电阻值后,再测量带宽。现在的带宽将会更接近要求,但可能也不完全正确,不过对此无需担心。滤波器的峰值可能会比之前略大一些,但这并不会造成问题。

其次,调整峰值(即Q值)。滤波器中几乎所有的峰值都是由第二级所产生,因为该级的

Q值和增益都更高(回路传输更小,带宽更窄),因此,我们将Q值的调整集中在该级上。可通过减小R1b电阻来调整峰值。先减小约20%,如果仍然出现峰值,则进一步减小阻值。如果阻值减小引起的频率响应太大,则应适当增加阻值。一个可使滤波器频率响应波形最接近Butterworth滤波器的好办法是,观察-1dB处的频率并调整R1b,直到

-1dB处的频率为5MHz(当达到该值时,频率响应波形应当干净、平坦)。通过将R1b值从1.58kΩ减小到1.24kΩ,使得滤波电路中的频率响应波形与一个理想的

Butterworth滤波器非常匹配。表2为电路中采用的最终电阻值。

表2:电路中采用的最终电阻值

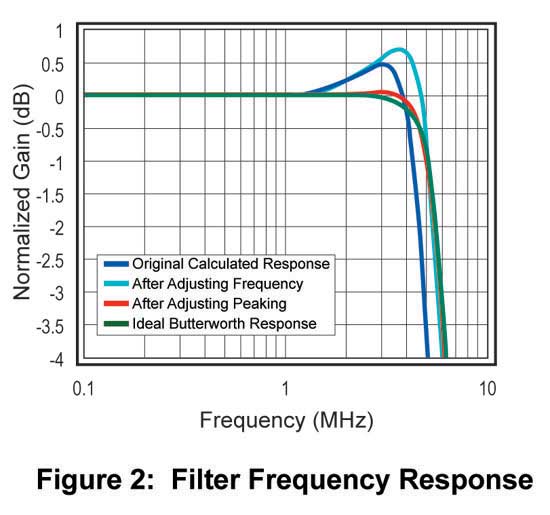

调整峰值后(电阻值应基于测量结果,不必非得与表2中的阻值相同),-3dB处的频率

将接近期望值6MHz。图2所示为电路中测量出的频率响应曲线,图中同时给出了初始

频率响应、调整频率后的结果、调整峰值后的结果(最终电路)以及理想Butterworth

滤波器的频率响应。

图2:电路中测量出的频率响应曲线,包括初始频率响应、调整频率后的结果、调整峰值后的结果以及理想Butterworth滤波器的频率响应。

滤波器性能

该滤波器的频率响应测量结果如图2所示(即调整峰值后的结果,用红色曲线表示),图2中也同时给出了一个理想的6MHz Butterworth滤波器的频率响应曲线(绿色曲线)。该频率响应结果是在用本文方法构建的电路上测出的。如图所示,该滤波器在视频频段内几乎不出现峰值、平坦度好,并且阻带抑制效果好。微分增益和相位同样也很不错。表3概括了该滤波电路的性能细节。

表3:一个理想的6MHz Butterworth滤波电路的性能细节

源阻抗和负载阻抗

这款滤波器在源阻抗为100Ω时工作良好。如果源阻抗更高,那么必须在计算第一个电阻(R1a)的阻值时将其作为考虑因数。例如,若源阻抗为150Ω,就要根据这个阻抗减小R1a的阻值。

图1中滤波器的增益为+2V/V,用于驱动以串联输出电阻(图中为75Ω)端接的线路,从而提供后端终接。后端终接将信号一分为二,这样从输入到线缆远端视频负载的总增益就变成+1V/V。

电路布局

元件之间应尽可能靠近并采用短走线。保持运算放大器的输入短走线比输出短走线更加重要。注意:要去掉运算放大器输入端附近的接地铜层,以减小电路板寄生电容。倒相输入附近的寄生电容会导致运算放大器出现峰值,而若寄生电容靠近非倒相输入,则会给滤波器增加额外的电容,从而改变滤波器的频率响应波形和带宽。

本文小结

采用现代高速运算放大器来实现用于标准清晰度视频系统的有源滤波器时,其设计和调整非常简单,采用有源滤波器来替代无源滤波器能节省设计时间和成本,同时大幅提高最终产品的性能。

上一篇:数字媒体装置的下一代安全技术

下一篇:视频MP3音/视频设计的新需求

推荐阅读最新更新时间:2024-12-18 22:13

- 古尔曼称苹果明年推出 AirTag 2 追踪器:升级 UWB 超宽带芯片,精确定位范围提升 3 倍

- 消息称苹果自研再下一城:蓝牙+Wi-Fi芯片 2025年iPhone 17系列首发

- 苹果从iPhone 18 Pro开始将弃用高通5G芯片

- 印尼投资部长确认:苹果计划在当地投资10亿美元建造零部件工厂

- 消息称苹果有望2026下半年推出折叠iPhone,并重振折叠屏手机市场

- 华为麒麟9020/9030/9040处理器曝光:小步快跑 四大方面升级

- 汇顶超声波指纹方案助力iQOO Neo10流畅解锁体验

- 曝苹果自研5G基带性能弱于高通:iPhone信号问题无解

- 消息称 AMD 将入局手机芯片领域,采用台积电 3nm 工艺

- 基于powerSTEP01的大功率步进电机驱动器扩展板,用于STM32 Nucleo

- 50 W / 60 W直接AC LED驱动器模拟调光

- 采用 TI DLP® 技术的 4K 超高清高亮显示参考设计

- 键盘人偶系统-Laser310电脑键盘仿真控制器

- P1022RDK: P1022参考设计套件(RDK)

- LT3970EMS-5 3.3V 降压转换器的典型应用

- 用于可调电流源的 LT1764AEFE-3.3 LDO 稳压器的典型应用

- AD8305-EVAL,评估板经过仔细布局和测试,以展示器件 AD8305 的指定高速性能

- 使用 PSoC 器件的 LIN 主演示板

- 朱雀T12焊台(修改版本-没有做验证)

ffmpeg基础库编程开发_20140307

ffmpeg基础库编程开发_20140307 【Follow me第二季第4期】任务合集-主板正反面识别,音量大小识别【z75993971】

【Follow me第二季第4期】任务合集-主板正反面识别,音量大小识别【z75993971】 Verilog HDL数字集成电路设计原理与应用

Verilog HDL数字集成电路设计原理与应用 TTLM4250CJ

TTLM4250CJ

京公网安备 11010802033920号

京公网安备 11010802033920号