由于数字电视的产量巨大,制造厂商最关注的就是如何在供应高质量的产品的同时,让大众的消费更加划算。随着电视成为家庭娱乐活动的中心,集成尖端功能和子系统的压力也在不断增长。最终用户变得越来越懂行,他们不但想要平板屏幕的优雅外观,而且还要求每台电视都具备多项功能。TiVo、SlingBox、Apple TV、ICE Box都已经成为现代化起居室内非常普通的必需品。这样就增加了系统设计的难度,而时序设计方面的难度也就更高。设计者正在为解决这一难题寻找更合适的方式,他们摆脱了传统的时钟设计技术,转向更为可靠的硅芯片时序解决方案。集成电路供货商目前已经能够在硅芯片时序器件上提供一些增值功能,以全面解决系统问题。让我们来了解一下这一目标是如何实现的。

每一套电子系统,无论是模拟系统还是数字系统,都需要时序基准信号,而整个电路的工作均以时序基准信号为基础。这个时序基准信号,或称之为“时钟”,在传统上采用晶体(压电石英器件)或晶体振荡器(晶体+振荡控制电路)。随着集成技术的不断发展,基于锁相环(PLL)的硅芯片时序解决方案的应用越来越普遍,为那些需要多种频率的设计方案提供了更洁净、更稳定的时钟选择方案。本文的目的在于详细论述采用硅芯片时序解决方案来解决时序设计难题时所持的价值主张,并与采用多个独立晶体或晶体振荡器(XO)的传统设计方法进行了对比。

1. 高清电视系统中采用多种频率的需要——不同的标准和接口

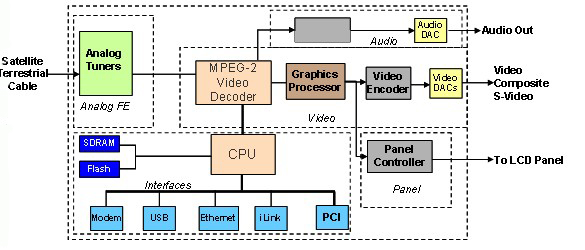

图1所示为液晶电视机天线的基本原理图,简单地说明了数字电视将输入的数字数据流处理成适于用户起居室内电视机使用的正确音频和视频格式的流程。

Satellite Terrestrial Cable?卫星地面电缆

Analog Tuners 模拟天线

Analog FE 模拟前端

MPEG-2 Video Decoder MPEG-2视频解码器

MPEG Audio Decoder MPEG 音频解码器

Audio DAC 音频数模转换器

Audio 音频

Audio out 音频输出

Graphics Processor 图形处理品

Video Encoder 视频编码器

Video DACs 视频数模转换器

Video Composite S-Video 视频复合S-Video端子

Video 视频

Flash 闪存

Panel controller 面板控制器

To LCD Panel 接至液晶显示屏

Panel 显示屏

Interface 接口

Modem 调制解调器

图1:常见液晶电视机体系架构

调谐电路板上加入了多个子系统。各项基本功能从广义上可以归类到以下几种模块下:

1.模拟前端(解调器)

2.音频/视频编码和解码(MPEG视频解码器/MPEG音频解码器)

3.各类接口

4.显示屏

上图中所显的所有模块几乎都需要时钟信号。CPU要求的时钟信号典型范围为30 – 100MHz。MPEG标准要求采用基于27MHz的时钟输入。其中存在需要解码器和编码器同步的必要功能,而这项功能由VCXO(电压控制晶体振荡器)来实现。对于作为数模转换器(DAC)时钟源的音频时钟,其ppm要求极为严格。这些频率取决于采样频率和过采样比率。对于各类接口来说,时钟信号由各自的标准来决定,诸如USB、以太网、调制解调器、PCI、PCIExpress、SATA等等。

显示屏的时钟取决于屏幕尺寸以及显示标准(高清(HD):1080i、1080p、720p;标清(SD):NTSC、PAL)。屏幕控制器子系统的基本系统是将输入图像数据转换成实际屏幕尺寸,例如,采用74.17582418 MHz等时钟。

2. 电视机体系架构和时钟树的实现

目前,设计者不得不在设计前期做出的一项关键决定就是信号格式,包括模拟信号或数字信号。几年以前,电视机的信号链路还是主要以模拟信号为基础,而如今,更为常用的是数字音频数据通路。数字和模拟通路均各自存在着一些固有的优缺点。但是,目前存在着一种全球性的必然发展趋势,即要求所有信号传输都采用数字技术,该趋势将分阶段实现。

高清电视的传输采用了数字信号,所以,新出品的电视机趋向于采用数字通路。采用数字传输方式的优点在于对噪声的容错性很高。另一方面,模拟信号易受到噪声的影响。电路板设计者需要在布线时加特别关注,采用拥有更优信噪比(SNR)性能的差分信号,或者运用屏蔽技术来避免信号品质降低。

传统的时钟树设计方式:这种方式针对每一种频率要求采用了分立的晶体/晶体振荡器(XO)。这种方式的好处在于,时钟可以布置在非常靠近元器件的位置,使布线变得简洁。但是,这种方式的缺陷在于,每一个晶体/晶体振荡器元件都必须提前从供货商处采购,从而不允许在最后阶段做出设计变更。如果有一个频率发生了变化,也要求有很长的交货周期,从而导致整个进度的延迟。

硅芯片时序解决方案:近10多年以来,基于锁相环的时序解决方案的流行度已经超过了传统时钟方法。硅芯片时序解决方案供货商能够提供分立晶体和晶体振荡器元件所不支持的多项功能,从而可应用于复杂的系统设计。这两种设计方式之间的折衷处理将在下文进行讨论。转向采用这种体系架构的客户所获得的主要益处在于,它赋予了客户的设计方案灵活性并节省了成本。

3. 与分立晶体/晶体振荡器相比,采用锁相环硅芯片时序解决方案的优势

1.成本——消费类产品市场领域的重要决策的驱动要素之一就是成本。每一次体系架构的变动都必须经济而划算,这样才可以实施架构转变,所付出的投资才是合理的。硅芯片时序解决方案最具吸引力的优势在于,通过将若干个晶体/晶体振荡器集成到一起,可以降低整体物料清单成本,并保持性能水平,或在某些情况下提升性能水平。在如上图所示的典型电视机天线电路板中,采用了5-6个分立晶体(每个成本为0.12 – 0.50美元),而如果一个能够提供上述频率的可编程功能的硅芯片时钟发生器的成本低于2.00美元,则就会真正为电路板增值。除了成本是晶体/晶体振荡器集成的主要推动要素,另外还有一些能够为OEM商和最终用户所感受到的其它优势。

2.可靠性——晶体是基于石英的元器件,比起基于锁相环的时序解决方案来说,晶体的故障率较高。从系统中每减少一个晶体都有助于提高整个系统的可靠性。集成度高还能够减少电路板上的元器件数量,获得最高的稳定性并实现更低的返修率。

3.晶体可用性——频率范围在10-40 MHz之间的晶体很容易做到。但高于40 MHz以上的高频晶体在制造上难度更高并且需要采用特殊的制造技术。这种晶体属于高阶泛音晶体,成本范围在1-10美元之间。这些高阶晶体较难购得。而硅芯片时序解决方案能够采用单个低频晶体(或者可以使用时钟基准信号)来生成多个高频输出。

4.晶体老化——晶体本身容易出现老化现象,每隔几年会出现+-2ppm至+-5ppm的误差。这种老化现象的原因在于晶体材质内部以及晶体表面之上存在的杂质以及晶体材料与沉积电极之间的机械应力。老化可能导致使用晶体的系统性能缓慢下降。在使用晶体时,长期频率漂移已经成为常见的问题。而基于锁相环的硅芯片时序解决方案能够在产品整个使用寿命内保持精确度。

5.可编程性——基于锁相环的时钟发生器拥有内置可编程性,可以在设计阶段提供一定的灵活性。这些可编程特色不仅包括了输出频率的改变,而且能够改变驱动信号强度设置值、扩频百分比、通过引脚编程实现频率选择,这些意味着同一个输出端可以根据需要提供不同的频率。系统内置的可编程性可以采用串行I2C接口在设计执行过程中改变一些特定参数。这一特色对于那些在多个平台上采用同一组频率的制造厂商是富有吸引力的。

6.减少元器件数量,节约板卡空间——采用可编程时钟发生器有助于通过集成减少电路板上的元器件数量。系统设计者正在趋向于采用更少的元器件,以求减少由于布线和需要保持信号完整性所带来的问题。基于锁相环的时钟发生器能够采用一个低频晶体生成若干个输出,因此对于减少元器件总数量以及节约宝贵的板卡空间极具价值。

7.采用扩频时钟降低电磁干扰——电视机天线电路板典型情况下为5-7层板,并采用了专用的铺地层以便压低干扰。为提高系统性能和避免发生串扰、扭曲和信号完整性问题,要对多路高速信号进行精心的布线。而硅芯片时序器件供货商通过提供扩频等功能,减少了这些板卡设计方面的问题。例如,扩频可以通过扩展高速信号来降低信号的峰值能量。

电磁干扰必须低于强制性标准所规定的限值,这些标准如CISPR 22或FCC Part 15 Class B。所有消费类产品必须通过严格的FCC规范认证才能上市。全球各地诸如美国通信委员会(FCC)这样的管理机构会确保强制性标准得到遵守而且器件产品不能在不属于它们的频段内发射信号。不幸的是,存在频率谐波的高速设计方案经常会遇到这方面的问题。扩频是一项目前由集成电路供货商提供的、能够解决这一干扰问题的功能。

扩频功能能够减少、甚至消除对会增加物料清单成本的铁氧体磁珠、滤波器、线圈和振流器的需要。如果系统未能通过电磁合规试验,则需要花大力气进行重新设计。考虑到试验所耗费的成本以及重新进行工程设计所浪费的时间,我们会认识到对这些问题做好通盘考虑并采取保险措施的重要性,例如提前采用扩频功能。而拥有可编程性就可以在需要时打开扩频功能以及在不需要时关闭该功能。这一功能在开发和测试中尤为实用。

8.库存管理——采购团队目前所面临的一项主要难题是对系统采用的每种元器件的存货量、需求量和预测规划进行管理。由于每家OEM商均拥有多个产品平台和子平台,这些平台和子平台均处于不同市场区间并专门针对特定的目标市场,而管理好这个供应链是一项相当繁重的工作。我们可以想像一下,管理10种频率不同并由全球不同供货商供应的晶体产品会有多么繁琐。而硅芯片时序元器件供应商提供了可编程时钟发生器,这个发生器可以由设计人员在设计时采用软件生成不同的频率,从而解决了这方面的问题。这种可编程性不仅让设计者的工作更加轻松,而且可以提供不同的频率来满足时序方面的预定目标,还能够让采购团队做到多个平台采购相同的器件产品。如果其中一个平台的需求量突然增加,采购团队则可以采用原本为不同平台的所采购器件。此外,由于还有一些诸如引脚可编程以实现频率选择的特色,因此可以在不对设计方案造成显著影响的情况下使用这些元器件。

9.完美的同步输出——某些应用可能需要若干个时钟信号复制,而且要求这些复制的时钟完全同步或一致。通过可编程锁相环器件即可提供这项功能。而使用若干个分立晶体时,达到这样的同步性能可能就较为困难。

10.电源管理——基于可编程锁相环的时钟发生器可以满足便携设备市场的特殊需求,其中包括游戏机、智能手机、个人媒体播放器、数码相机、便携摄像机等。在这些对功耗较为敏感的应用中,通过采用I2C通信或引脚编程技术,可以选择性关闭某些频率。例如,在智能手机领域,并不是所有应用程序都需要长时间运行。在用户希望使用其中一项功能时,例如,使用GPS功能进行指路时,就可以将这一特定频率打开。一旦这项功能不再使用,则系统可以将这一频率源降低功率运行。在采用分立晶体/晶体振荡器的传统设计中,这一点并不容易实现。

4. 为何需要降低液晶面板控制器的电磁干扰

液晶屏幕目前已经无处不在而且极为流行,它在我们实际生活中的应用多得超乎我们的想像。其中包括,你正在购买的所有新款iPhone的3.5英寸触摸屏,你在感恩节大减价时买到的夏普Aquos?电视机,亦或者你走在拉斯维加斯的繁华地带看到的闪闪发光的街道标志,或者更为常见的,你每天使用的ThinkPad笔记本电脑——为这些视觉享受提供动力的技术实际都是液晶技术。液晶面板的这种渗透度表明,推动它流行的技术已经成熟,新机型的价格也比以前更为合理。

而对液晶屏的要求也在不断提高,人们要求更大的面板、更少的电磁干扰、更低的功耗以及更高的图像质量。

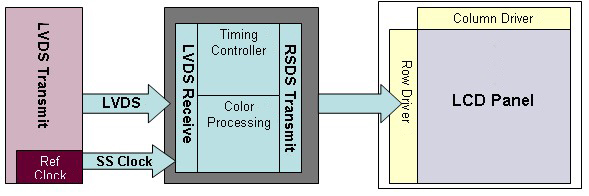

这里,我们从更高层次上对液晶面板的架构进行一些详细剖析。液晶面板实际上是一个晶体管阵列,这个阵列用于对液晶体两端的电压进行调制,并因此能够控制穿过面板的光线数量。而彩色显示实质上是通过采用那些让红光、绿光或蓝光通过给定像素的滤光片实现的。行驱动器连接到晶体管的栅极。行驱动器通过施加“开”或“关”电压来控制着在任一给定时刻哪一行像素正在得到编程。这些晶体管的源极连接到列驱动器,而列驱动器供应着达到正确像素亮度所要求的特定电压。

时序控制器从主机获取显示数据并通过面板接口将数据传输给列驱动器和行驱动器。其中也可以加入附加功能,诸如采用过驱动以减少运动模糊现象、增强图像以及进行伽马校正。行驱动器接口采用晶体管逻辑电路(TTL)作为信号发生级。而列驱动器接口需要大量的带宽,以实现更清晰的显示,所以采用了不同的总线体系架构——典型情况下采用抑制摆幅差分信号(RSDS)。

LVDS Transmitter LVDS(低压差分信号)发射器

Ref Clock 基准时钟

SS Clock 扩频时钟

LVDS Receiver LVDS接收器

Timing Controller 时序控制器

Color Processing 色彩处理

RSDS Transmitter RSDS发射器

Row Driver 行驱动器

Column Driver 列驱动器

LCD Panel 液晶面板

图2:液晶面板控制器方框图

面板电子线路中存在的主要难题之一是降低干扰以满足电磁兼容性(EMC)规范的要求。面板制造厂商通常会为不同种类的应用提供不同类型的面板,包括电视机、PC机显示器、笔记本电脑、手持设备、个人娱乐系统等。但面板制造厂商倾向于在所有尺寸的面板上采用同一种电路板。但这些厂商是怎样采用尺寸受限的2层电路板来满足电磁干扰(EMI)试验要求的呢?他们是如何有效地为各种屏幕尺寸设计印刷电路板(PCB),并且还能够在满足电磁规范的同时按时完成项目的呢?

达到这些目标有几种方法,其一是改善印刷电路板材料的质量,增加采用专用铺地层的附加电路板层。大多数液晶面板中的印刷电路板都采用标准的FR4材料制造。考虑到所要增加的成本,采用成本更高的印刷电路板材料以及增加更多电路板层也不是一项可行的方案。另一种减少电磁干扰的方法是采用滤波,但是,这种方法也不是一种能够适用于所有面板尺寸的万全之策。而且,每一个电路网都需要进行滤波。而未能满足电磁兼容性试验要求会导致重新进行工程设计并影响产品的上市周期。

如图2所示,扩频(SS)时钟发生器已经成为用来解决电磁干扰难题的流行方式。多家硅集成电路供货商,包括赛普拉斯半导体公司,已能够为液晶显示系统供应扩频时钟产品。其优势在于能够采用系统化的方法在前期解决电磁干扰问题。扩频功能可以有选择性地打开,而且可以对扩频百分比进行调整以获得合适的扩展量以便通过电磁兼容性试验。对于不同尺寸面板,其扩展百分比也可以有所不同,这点可根据需要确定,而采用的元器件相同。由于板卡空间有限,这些时钟产品均采用了极小的封装尺寸。

总体来说,包括液晶电视在内的数字电视的体系架构正在不断发展,并正在采用更新的方法来提供高质量的“高清”水平的音频和视频,同时保持对于最终市场的经济合理性。数字电视生产厂商正逐步认识到硅芯片多锁相环和扩频时钟方法在改善性能和加快产品上市周期方面的价值。

Ashwini Raman is a Product Marketing Manager in the General Purpose Clocks business unit at Cypress Semiconductor. Her responsibilities at Cypress include definition and rollout of new products and driving design win activities of Programmable and EMI Reduction clocks.

上一篇:H.264/AVC中扩展空域可伸缩编码的研究

下一篇:基于AVS-M和DM642视频服务器的研究

推荐阅读最新更新时间:2024-12-18 22:14

- 美光推出速率与能效领先的 60TB SSD

- 古尔曼称苹果明年推出 AirTag 2 追踪器:升级 UWB 超宽带芯片,精确定位范围提升 3 倍

- 消息称苹果自研再下一城:蓝牙+Wi-Fi芯片 2025年iPhone 17系列首发

- 苹果从iPhone 18 Pro开始将弃用高通5G芯片

- 印尼投资部长确认:苹果计划在当地投资10亿美元建造零部件工厂

- 消息称苹果有望2026下半年推出折叠iPhone,并重振折叠屏手机市场

- 华为麒麟9020/9030/9040处理器曝光:小步快跑 四大方面升级

- 汇顶超声波指纹方案助力iQOO Neo10流畅解锁体验

- 曝苹果自研5G基带性能弱于高通:iPhone信号问题无解

ffmpeg基础库编程开发_20140307

ffmpeg基础库编程开发_20140307 Verilog HDL数字集成电路设计原理与应用

Verilog HDL数字集成电路设计原理与应用 TTLM4250CJ

TTLM4250CJ

京公网安备 11010802033920号

京公网安备 11010802033920号