为什么烧录Nand Flash经常失败?为什么烧录成功了,一部分Nand芯片贴板之后系统却运行不起来?…,等等,问了那么多为什么,那我反问一个问题:你了解Nand Flash的特性及其烧录关键点吗?

关键字:Nand 烧录 flash

引用地址:从Nand特性谈其烧录关键点

一、Nand flash的特性

1、位翻转

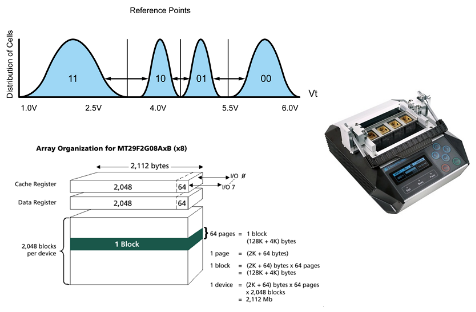

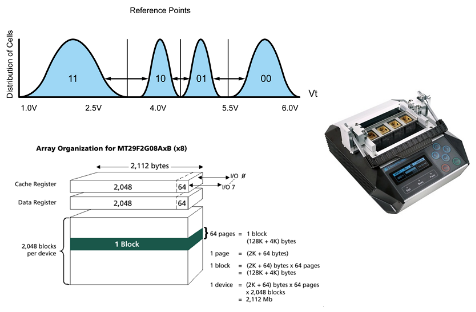

在 NAND 闪存是通过对存储单元(Cell)进行充电来完成数据存储的,存储单元的阈值电压就对应着数据值。当读取的时候,通过将它的阈值电压与参考点对比来获得其数据值。对SLC 而言,就只有两种状态和一个参考点。而对于2-Bits 的MLC 而言,它有4 种状态和三个参考点。TLC就更多状态和参考点。当读出的数据值与编程时数据值对应的阈值电压不相匹配时,表明数据发生了位翻转,就带来了可靠性问题。导致位翻转的最常见原因是“编程干扰”导致的阈值电压漂移。

2、存储结构

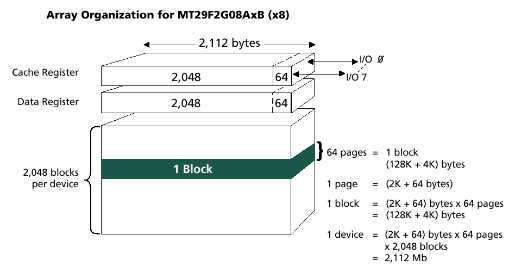

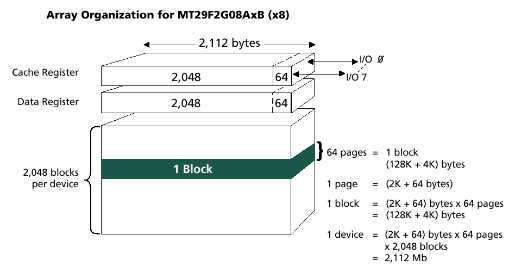

Nand 闪存由多个Block组成,每一个Block又由多个Page组成,Page的大小一般为512+16Bytes 、2K+64Bytes以及4096+128Bytes,Page是读取和编程的基本单位,而擦除的基本单位是Block。

NAND Flash的页,包含主区(Main Area)和备用区(Spare Area)两个域,“主区”也常称作数据区,备用区是保留区域,一般用来标记坏块(bad block)和存放ECC的值,当然有些文件系统使用备用区记录擦除次数、文件组织数据等。

图1.1 为页大小为2048+64的闪存存储结构

3、坏块及ECC

位翻转的发生是随机的,且比特误码的数量会随着擦写次数的增加而增加。但是只要比特误码的数量在ECC 能够纠正的范围内,数据的完整性就始终有保障。在有些点,每页的比特误码有可能很接近ECC 所能纠正的极限,NAND 的控制系统必须严防比特误码超过可纠错的范围,否则,就可能造成数据丢失或者系统无法正常工作。因此,这些块必须要标记为坏块。坏块永远不应该再用来存储数据。由于坏块的产生是不可避免的,NAND 制造商在对裸片测试时会选择对某些块进行坏块标记,而不是放弃整个裸片,所以大多数NAND 在出厂时就已经存在标记为坏块的块。如果一个NAND 的块被标记为坏块,那么NAND 的容量就永久性的减小了。

二、Nand系统裸片量产烧录的关键点

由于Nand flash芯片的特性,以其作为存储介质时必须对这些特性进行恰当处理,这样系统才能正常运行。系统设定各分区数据在Nand芯片的存储布局,并且在存储驱动层对Nand进行位纠错、坏块管理等处理,这些信息需要系统/驱动工程师明确。

研发阶段或小批量生产阶段,常采用在板烧录的方式,原理是将boot通过串口下载到内存跑起来,由boot从SD卡或网络将内核镜像、文件系统镜像等数据烧录到Nand flash芯片。

为了提高生产效率或别的方面考虑,会使用烧录器对Nand flash裸片进行量产烧录,由于烧录器厂家并不知道存储驱动层对Nand各种特性的处理方式,所以不加正确配置就进行烧录的话,往往出现以下情况:1. 烧录失败,经常是校验通不过;2. 烧录通过,但是部分芯片贴板之后系统运行不起来,或者运行起来某些模块出现一些错误与异常。这些大多不是烧录器本身的问题,而是裸片烧录Nand系统时几个重要的关键点没有处理好,或者说没有和目标系统相关处理一致。这些

关键点包括:

1) 坏块处理策略

2) 分区(Partition)

3) 纠错码(Error Correction Codes,ECC)

当然,影响烧录的还有其他因素,比如备用区的使用情况、未用好快的格式化以及动态元数据等,但我们这里只讨论上面几个比较普遍的因素。

1、坏块处理策略

坏块一般是根据芯片的坏块标记位置进行识别的,而坏块处理策略定义了在遇到坏块时算法应该如何处理。策略算法负责将本来应该写到坏块的内容写到其它可选的好块中。最常用的坏块处理策略是跳过坏块,其他典型的还有带BBT的跳过坏块及预留块区等。

跳过坏块的处理策略是最基本最常用的坏块替换策略。当烧录中遇到坏块时,算法简单地跳过坏块,而将数据写入下一个好块。它会造成物理数据和逻辑数据的位置偏移,这通常需要分区来解决这个问题。

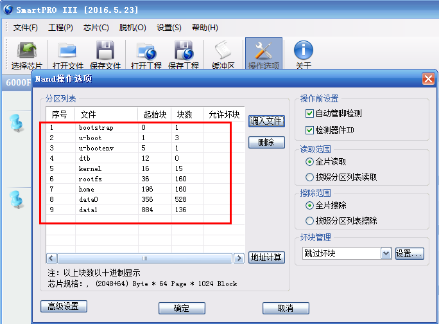

2、分区(Partition)

采用类跳过坏块的处理策略的Nand系统,常常会把存储区分成若干个不同的物理区域,这就是我们说的分区,概念上很像电脑硬盘的分区。使用分区使得你有能力确保你的数据可以存到预先指定的物理块区内,即便在这之前发现了一些坏块。这对一些底层软件组件比如启动引导程序和某些必须很容易定位的文件系统驱动程序来说,是非常有帮助的。

当使用跳过坏块的替换策略时,坏块会导致数据顺移到下一个好块。如果设置了分区,就可以指导烧录器确定数据的边界,确保数据文件不会侵占邻近的分区。

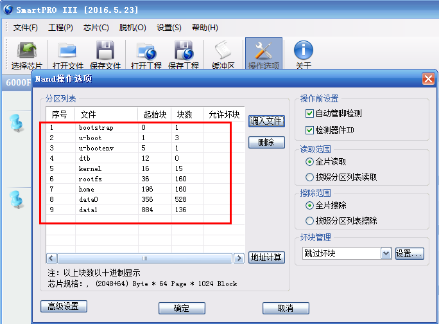

图2.2.1就是典型的嵌入式Linux系统的分区情况。

图2.2.1 典型的嵌入式Linux系统分区情况

3、纠错码(Error Correction Codes,ECC)

针对不同工艺、容量的NAND存储系统采用适当的ECC算法是应该的,要保证系统的可靠性,甚至是必须的。ECC纠错码一般存放在备用区中,对一整页或将页分成若干节的数据进行计算而得。数据烧录之前需要准备好ECC(硬件ECC除外),如果是纯数据则需要使用ECC算法来生成。Nand裸片量产中,知道ECC算法的纠错能力(纠错位数)是很重要的,因为要保证生产效率,烧录器如果采用ECC来进行校验数据是不实际的,而通过简单数据比对就可以知道数据的位翻转个数,如果翻转个数范围在ECC算法的纠错范围之内,则认为校验应该是通过的。

三、烧录定制

对于以上关键点或其它特殊部分,如果烧录器软件没有支持的相应的方案,需要联系原厂进行相关算法的定制,比如坏块处理方案、ECC方案等。

上一篇:三星NAND Flash 传四年后重返iPhone

下一篇:eMMC烧录时需注意的寄存器配置

推荐阅读最新更新时间:2024-05-03 15:37

赛普拉斯采用UMC 工艺生产的40nm eCT Flash MCU现已出货

2016年12月19日,美国加利福尼亚州圣何塞,中国台湾新竹市— 全球领先的嵌入式解决方案供应商赛普拉斯半导体公司(纳斯达克交易代码:CY)和全球领先的半导体代工厂联华电子公司(纽约证券交易所:UMC;台湾证券交易所:2303)(以下简称 UMC )于今日宣布,赛普拉斯由UMC代工的专有40nm嵌入式 电荷捕获 (eCT™) 闪存微控制器(MCU),现已开始大单出货。这标志着赛普拉斯闪存技术和UMC 40nm低功耗(40LP)逻辑工艺的多年合作达到了一个全新高度。40nm eCT Flash 单元尺寸仅为0.053μm2,比最接近的竞品约小25%。该微型eCT闪存具备8纳秒的随机存储速度和30微秒的word-programming

[嵌入式]

离线语音芯片是怎么烧录的?

语音芯片是芯片内的一部分,语音IC;中文又被叫做声音芯片、音乐芯片,可以由按键控制或MCU控制的,直接发声的集成电路芯片。 根据语音芯片的输出方式分为两大类,一种是PWM输出方式,一种是DAC输出方式,PWM输出音量不可连续可调,不能接普通功放,目前市面上大多数语音芯片是PWM输出方式。另外一种是DAC经内部EQ放大,该语音芯片声音连续可调,可数字控制调节,可外接功放。 而我们的生活中经常见的停车场报金额、电梯报站、货车报“左转弯,请注意”等等,都是应用了语音芯片,那么语音芯片是什么烧录的呢?作为源头语音芯片专业厂家,九芯电子根据10余年的行业经验为大家讲解: 语音芯片的烧录是根据不同类型的芯片,有不同的选择的,具体的如下

[嵌入式]

台媒:芯片制造商计划提高QLC NAND产量

据业内消息人士透露,由于个人电脑(PC)和数据中心的需求强劲,全球主要的NAND闪存供应商准备在今年年底至2022年之间提高 QLC NAND产量。 digitimes报道指出,消息人士称,随着OEM越来越多地在其产品中采用QLC SSD,芯片供应商将增加用于PC的QLC NAND产量。与此同时,数据中心应用的QLC NAND需求前景广阔,这也鼓励了主要芯片供应商加强在该领域的部署。 从各大厂商的动作来看,英特尔已经推出了面向企业存储应用的144 层 QLC固态硬盘系列产品,并于今年上半年开始面向数据中心应用出货。英特尔采用浮栅技术制造的QLC NAND依然是该领域的领导者。 美光已将其176层 TLC NAND的生产良率提

[手机便携]

解决烧录问题:Jlink的三线制SWD方式连接STM32芯片无法识别

网上找到此文章解决了j-flash只能连接后不能烧录的问题,希望遇到相同问题的小伙伴,可以用同样的办法解决: 前段时间,做了一块板子,调试接口只留了三个口SWD、SWCLK、GND,在使用Jlink的SWD方式调试的时候发现无法连接。使用ST-link的时候可以连接,无奈楼主的ST-link的链接方式相当的不可靠,时而能识别时而不能识别:当然我的ST-link是山寨版的。 那么问题来了:为什么通过20针全部连接的方式可以调试,而三针的方式就不行了呢? 古人云知之为知之,不知Google之,Google不让用,那就问度娘好了。 通过查阅网上资料发现,jlink的20针,不光有调试的功能还有供电和检测电压的功能。 下面是jl

[单片机]

日美公司开发出高密度NAND闪存

日本东芝公司和美国SanDisk公司日前宣布合作开发出高密度NAND闪存,并计划分别于年内开始批量生产相关产品。 两家公司7日发布的新闻公报说,它们已利用43纳米工艺开发出新型16吉比特NAND闪存,其密度与利用56纳米工艺生产的同等容量NAND闪存相比要高出一倍,这意味着闪存芯片的面积可显著缩小,从而能够降低有关成本。 据悉,两家公司在开发高密度NAND闪存生产工艺的过程中,采用了一些新技术并调整了有关外围电路的设计,从而大幅度缩减了芯片的面积。 东芝公司打算今年3月开始批量生产新型16吉比特NAND闪存,然后于7月到9月间批量生产32吉比特的产品。SanDisk公司则计划于今年第二季度生产和发售这两种不同

[焦点新闻]

STM32F7 片上闪存(Flash)

这篇文章我们来说一下嵌入式FLASH。 FLASH接口 FLASH接口其实在前面的文章中有提到,可以分为三类: 第一类,64位ITCM接口,该接口连接Cortex-M7的ITCM总线,用于指令执行以及数据读访问。它不支持写访问,支持64个标准化缓存行,256位宽。 第二类,64位AHB接口,该接口通过AHB总线矩阵连接Cortex-M7的AXI总线,用于代码执行以及读写访问。无论寻址的FLASH接口是TCM还是AHB,FLASH上的DMA和外设DMA数据传输都通过AHB接口完成。 第三类,32位AHB寄存器接口,该接口主要用于访问控制寄存器和状态寄存器。 FLASH构成 F7的FLASH最高有1M字节的用户闪存,它一共分

[单片机]

若拿下东芝 郭董:优先设厂美国

鸿海董事长郭台铭昨(12)日证实,将筹组美、日、台梦幻团队,共同竞标 东芝 半导体。 对日本出现担心鸿海「中国因素」的评论,郭董炮火全开,左打美系私募基金,右批日本经济产业省高层,并强调,鸿海如果顺利得标,海外市场将优先考虑在美设内存芯片厂。下面就随手机便携小编一起来了解一下相关内容吧。 东芝 半导体竞标案进入倒数计时,预计本周公布结果。 竞标者之一鸿海动作不断,郭台铭接连接受日经新闻、路透社专访。 郭董强调,如果鸿海顺利标下 东芝 半导体事业,希望未来能在海外建立内存工厂,地点将优先考虑美国。 郭台铭补充,因为美国国内市场需求在当地还没达到,目前当地公司所需要的芯片,只有14%在美国制造。 东芝所生产的 NAND

[手机便携]

玩转mini2440开发板之【tekkamanninja版的u-boot的编译和烧录】

今天继续玩一玩mini2440开发板,弄清楚U-boot的编译和烧录过程。 首先,这里交代一个前提,此处所使用的u-boot,是已经移植测试过的,完全可用的版本。就本文而言,我使用的是tekkamanninja大神于2010.03移植过来的mini2440定制版的u-boot,这位大神是友善之臂官方推荐的研究u-boot的大神,厉害之极,其所移植的代码也一直都是大众所效仿和研究的目标。下面就开始具体步骤的介绍: 1、下载和分支 由于tekkamanninja大神的u-boot源码存放于github上,因此我们使用以下命令进行克隆: git clone https://github.com/tekkamanninja/u

[单片机]

最新手机便携文章

- 消息称 AMD 将入局手机芯片领域,采用台积电 3nm 工艺

- 苹果搁置反垄断报告的请求遭印度监管机构拒绝,案件将继续推进

- 曝iPhone SE 4首发苹果自研5G基带:明年3月登场

- 曝iPhone 17全系首发3nm A19系列芯片:无缘台积电2nm工艺制程

- 供应链称上游元器件要大降价:国产手机现涨价潮后会主动下调售价吗

- 消息称苹果将拿出近 1 亿美元用于解除印尼 iPhone 16 系列销售禁令

- 消息称塔塔公司收购和硕在印度的唯一一家iPhone工厂,深化与苹果合作

- 苹果遭4000万英国iCloud用户集体诉讼,面临276亿元索赔

- 消息称苹果、三星超薄高密度电池均开发失败,iPhone 17 Air、Galaxy S25 Slim手机“变厚”

更多精选电路图

更多热门文章

更多每日新闻

更多往期活动

厂商技术中心

随便看看

嵌入式系统软硬件协同设计教程:基于Xilinx Zynq-7000 (符意德)

嵌入式系统软硬件协同设计教程:基于Xilinx Zynq-7000 (符意德)

京公网安备 11010802033920号

京公网安备 11010802033920号