引言

系统硬件设计

TMS320C5409作为主处理器的可行性分析

在本系统中,TMS320C5409作为主处理器,任务是实现JPEG压缩编码。

通过分析不难得到,当处理一帧大小为640×480的图像时,作JPEG压缩编码所需要的时间为:T=62×10(ns)×640×480=0.19866s,当所处理的图像分辨率更小时,则压缩每帧所花的时间更少,这对于应用在对实时性要求不是很高的场合是完全可行的。

硬件设计框图

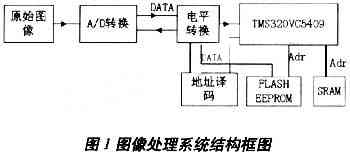

图1是基于TMS320C5409的图像处理系统结构图。C5409为中央处理器,SRAM为DSP片外扩展数据存储器,EEPROM为脱机工作时的程序存储器,用于存储系统的引导程序和其它应用程序,A/D转换部分负责把转换为数字信号的图像存入帧存储器中。地址译码、图像采集系统控制电路产生本系统各部分的地址译码信号,使之映射到不同的地址区域,并控制ADC进行图像采集,这部分由CPLD控制;图像采集芯片的寄存器控制由51单片机完成。

存储空间的扩展方案

DSP芯片电源电路设计

电源设计中需要考虑的主要问题是功率和散热。功率要求:电流的消耗主要取决于器件的激活度,即CPU的激活度,外设功耗主要取决于正在工作的外设及其速度,与CPU相比,外设功耗是比较小的。以TMS320C5409为例,进行FFT运算时,需要的电源电流最大。因此在设计电源时,必须考虑在电源电流和实际需用电流之间留有一定裕量,因为峰值电流会更大,裕量至少是20%。

C5409采用了双电源供电机制,工作电压为3.3V和1.8V。其中,1.8V主要为DSP的内部逻辑提供电压,包括CPU和其它所有外设逻辑。外部接口引脚采用3.3V电压。本系统的电源采用了TI公司的两路输出电源芯片TPS73HD318,它是一种双输出稳压器。输出电压一路为3.3V、一路为1.8V,每路电源的最大输出电流为750mA。

JPEG图像压缩算法

JPEG算法的优化

尽管JPEG基本系统能够对图像进行低压缩比压缩,但是DCT和IDCT在软件实现的过程中,是最耗费时间的运算,而且,由于没有考虑图像本身的频谱特性,JPEG量化表对于所有图像压缩并不一定最优。采用快速DCT算法可提高软件的速度,增强软件的实时性。同时,根据图像本身的频谱特性,自适应改进JPEG推荐的量化表。

快速DET算法

如果将一幅图像分成许多8×8的小块后直接进行2D—DCT变换,运算量将会十分巨大。因此,需要将8×8二维DCT变换转换成两次8点的一维DCT复合运算。具体做法是对每一个8×8块先做列方向上的DCT变换,得到一个中间矩阵,再对该矩阵各行进行DCT变换。可以看到,8×8矩阵的2维DCT可以转换成16次一维8点DCT。

目前,很多针对一维DCT运算的DCT快速算法已经提出。其中,Loeffler算法所需要的计算量最小。Loeffler算法将8点一维DCT运算分为4级,由于各级之间的输入/输出存在依存关系,4级操作必须串行进行,而各级内部的运算可并行处理。

流程图中有三种运算因子:蝶形因子、旋转因子和倍乘因子,分别如图3中的a,b,c所示。蝶形因子的运算关系为:

D0=I0+I1

O1=I0-I1

需要2次加法完成,倍乘因子的输入/输出关系比较简单: ,只需1次乘法,旋转因子的运算关系为:

,只需1次乘法,旋转因子的运算关系为:

需4次乘法、2次加法完成。如果对其输入/输出关系式做以下变换:

只需要3次乘法、3次加法。其中, 和差都是已知系数,可通过查表获得。

和差都是已知系数,可通过查表获得。

由此计算可知,一个8点DCT的Loeffler算法共需要11次乘法和29次加法。从DSP汇编语言编程的角度来看,一个代数运算应包括取操作数、运算、存操作数三个步骤。因此,该算法大约需要120条指令。C5409的运算能力很强,支持单周期加/减法和单周期乘法运算,并且能够在单周期内完成两个16位数的加/减法运算,再加上DSP中有3组数据总线,因而可以利用长操作数(32位)进行长字运算。在长字指令中,给出的地址存取的总是高16位操作数,因而只需5条长字指令即可计算2个蝶形运算。加上采取其它优化措施,大约需90条指令完成Loeffler算法。

虽然Loeffler算法运算量最小,但是运用于本文系统并不是最优。因为该算法是为高级语言设计,没有利用汇编语言的特点和DSP硬件的特点。本文提出了基于DSP乘法累加单元的DCT快速算法。

DSP的乘法累加单元能在单周期内完成一次乘法和一次累加运算。如汇编指令运用于DCT运算,将大大简化程序的复杂度并减少计算时间。具体算法如下,利用蝶形运算:

从上面表达式可以看出,y(0)-y(7)都是乘法累加运算,而s0-s7可由x(0)一x(7)经过蝶形运算得到,因此,DCT算法由原来的4级运算变成两级,即第一级蝶形运算和第二级乘法累加运算,第一级蝶形运算共要10+4=14(10次计算操作和4次辅助操作)条指令,第二级运算中,每个输出要4+1+1=6条指令(做4次乘法累加运算、1次读取操作和1次存储操作),一共48条指令,这样,计算一个8点DCT要62条指令,大大缩减了运算时间,提高了CPU的工作效率,增强系统的实时性。

量化运算优化

本文提出了基于实际情况的自适应量化方法,即量化阶段采用二次计算的方法,其算法主要分为两步:(1)对变换后的图像系数进行自适应处理;(2)构造新的量化表。具体方法如下:

首先求出亮度分量和两个色度分量在频域中所有8×8子块的63个交流系数绝对值的平均值P(u,v),其中,u,v=0…7为位置信息。接下来求出163个交流系数平均值中的最大值,Z1(u,v)=MAX[P1(u,v)],最后将63个交流系数平均值进行归一化处理,同时加入频率位置信息,分别得出亮度和色度量化表中63个交流分量的矫正系数,计算过程为:

由此可以得到量化表的矫正式Qpl(u,v)=Q1(u,v)/X1(u,v),对JPEG量化表进行矫正。

将上述矫正后的量化表作为最终的量化表,对图像进行标准JPEG压缩,形成完全符合JPEG格式的压缩文件。本算法的解码过程与标准.JPEG解码过程完全相同,可以看出它也是标准.IPEG编码过程的逆过程。

实验结果

快速DCT运算

将本文提出的算法、Loeffler的DSP优化算法和纯Loeffler算法分别进行测试。结果见表1,可以看到本文算法较Loeffler的DSP优化算法大约节省了1/4的时间,较纯Loeffler算法大约节省了一半时间,其效果是十分明显的。

自适应量化

对自适应量化器进行仿真。本文采用中等复杂度的标准图像作为测试图,与基本JPEG系统进行性能比较(基于峰值信噪比(PSNR))。只将JPEG标准方法中的量化表更改为修正的量化表,就可以在同等压缩比下,提高恢复图像的质量。表2为不同压缩比下,采用JPEG量化表和自适应量化表两种方法的峰值信噪比。从压缩比和峰值信噪比的对比结果可看出,自适应量化JPEG方法的压缩比略高于标准JPEG方法。

结语

本文以TI的TMS320C5409作为开发平台,实现了一种新的JPEG图像压缩系统。该系统的优点是提高了JPEG的运行速度,增强了图像的压缩率和质量,并且易于硬件实现。这一方案可应用于需要对视频图像进行实时采集、压缩及存储的绝大部分场合。

上一篇:研祥携维宏召开浙江宁海数控行业发展研讨会

下一篇:基于DSP的电力线载波OFDM调制解调器

推荐阅读最新更新时间:2024-05-02 20:42

【模拟工程师】电路设计指导手册:运算放大器

【模拟工程师】电路设计指导手册:运算放大器 Verilog HDL数字集成电路设计原理与应用

Verilog HDL数字集成电路设计原理与应用

京公网安备 11010802033920号

京公网安备 11010802033920号