摘要:利用视频解码芯片ADV7183A来完成模拟视频信号的采集量化,进而由ADSP-BF561完成视频数据的压缩,再通过PPI传输将压缩过的视频数据传送到由ADSP-BF537和LAN8187等芯片组成的网络传输模块,网络传输模块再将处理后的视频数据流通过组播和单播方式发送给指定用户。能够满足观频监控系统的实时性和远程化要求。

关键词:BF561;ADV7183A;视频压缩;网络传输

随着视频社会的发展和科技的进步,视频信息业务得到快速增长,视频信息技术经历了由模拟到数字的转变,数字视频是以数字形式记录的视频,数字化对视频信息的传输和存储创造了有利条件,但末处理的数字视频流有较高的带宽,因此在保证视频图像清晰度、流畅度、实时性的条件下,进行视频缩和网络传输成为一项重要的技术。

1 设计方案

文中网络视频压缩硬件系统结构如图1所示。在本网络视频压缩系统中,采用Analog Device公司的ADSP-BF561、ADSP-BF537、ADV7183A心片;SMSC公司的LAN8187网络芯片;系统可分为视频采集压缩模块及网络控制模块,其中视频采集压缩模块由ADI高性能双核处理器DSP BF5 61和视频解码芯片ADV7183A构成,并辅以SDRAM和Flash等外围器件。网络控制模块由ADI高性能DSP BF537和以太网接口芯片LAN8187构成,同样辅以SDRAM和Flash等外围器件。前端输入的模拟视频信号经过视频解码芯片ADV7183A采集量化变换为数字视频信号,通过BF561的并行PPI接口进入BF561的缓冲存储区,由BF561完成觎频数据的压缩处理,压缩形成的MPEG4视频流通过并行PPI接口进入BF537,经过封装处理后通过以太网接口进行分发。

2 硬件电路设计

2.1 视频采集压缩模块设计

视频采集压缩模块由核心压缩处理器BF561和前端视频解码器ADV7183构成,并辅以外围的SDRAM和Flash。

(1)视频压缩处理器BF561。BF561处理器是Blackfin系列中的高性能产品,BF561的核心由两枚独立的Blackfin处理器组成。BF561集成了一套通用的数字图像处理外围设备,为数字图像处理和多媒体应用创建了一个完整的系统级片上解决方案。利用BF561双核结构,将前端视频解码器采集的视频信号分割为上下半帧数据,并将分割的视频数据分别由其双核独立进行压缩处理,为完整地恢复压缩前的画面,在其双核之间进行了同步处理,使得根据输出的数据信息解码后能够完整流畅的恢复压缩前的画面,同时为平衡两个内核工作量,还将系统的初始化、控制前端视频解码器等工作交给主核来处理,给视频画面叠加动态辅助信息的工作交给另一个内核进行处理。

(2)视频解码器ADV7183A ADV7183A是美国摸拟器件公司(ADI)推出的集成了10位ADC的增强型视频解M码器。它内含3个精确模数转换器(ADCs)和完整的自动增益控制(AGC)电路。其灵活的数字式输出接口能够与BF561的PPI接口进行无缝连接,消除了由于数据信息传输速度造成整体压缩处理能力的瓶颈。ADV7183A与DSP之间的配置通信遵循I2C协议,因此ADV7183A提供了标准I2C接口,与BF561的PF接口相连接。

BF561的PF,引脚和ADV7183A的0E引脚相连,控制视频解码器的数据输出,这里输出的数据可以选择16/8位输出,系统选择8位输出数据格式;

BF561的PF2引脚和ADV7183A的SDATA引脚相连,ADV7183A的SDATA引脚是I2C总线的串行数据输入/输出引脚;

BF561的PF0引脚和ADV7183A的SCLK引脚相连,ADV7183A的SCLK引脚是I2C总线的串行数据输入/输出引脚,为视频解码器提供串行时钟输入;

BF561的PPI2CLK引脚和ADV7183A的LLC1引脚相连,由ADV7183A的LLC1引脚为BF561提供视频像素输出同步时钟;

BF561的PF13引脚和ADV7183A的RESFT引脚相连,为视频解码器提供复位信号;

BF561的PPI2D0~7引脚和ADV7183A的,P8-P15引脚相连,作为视频数据传输总线。

同时为ADV7183A提供27 MHz的晶振输入列XTAL引脚,选择模拟输入通道AIN1,在AIN1引脚上输入模拟信号,对于系统而言,采取默认配置,不再对I2C总线进行配置。完成这些设置后,接上电源,ADV7183A就可以在默认配置下正常工T作了,默认输入为PAL制的图像,输出是P8~P15的8位ITU—BT656的YCrCb型4:2:2视频数据。[page]

2.2 网络传输模块设计

网络传输模块是将视频采集压缩模块处理过后的输出数据流发送到外界用户的通道,所以要求其核心处理理器既可以与BF561方便地连接又有很好的网络扩展性,所以选择了同一系列的BF537处理器,充分利用其PPI接口实现与BF561的快速无缝连接;由于BF537集成了以太网MAC控制器,所以又可以和用BF537的网络扩展性能,辅以SMSC公司的以太网接口芯片LAN8187,同时由于LwIP(LightweightTCP/IP Stack,轻量级TCP/IP协议栈)有效地减少TCP/IP协议栈所占用的空间,LwIP约占用40 kB的内存空间和ROM存储空间,比在内核中实现的TCP/IP协议栈要小得多,并且LwIP支持多网络接口下的IP转发,支持ICMP协议,支持扩展性的UDP报文,支持转发的TCP报文,提供专门的内部回调接口(RawAPI)。RAW API直接使用了LwIP协议栈中的回调函数(Call Back Functions),从而使应用程序和协议栈代码能够更好地集成在一起,运行在同一个进程中,以提高应用程序性能,使之适合于嵌入式系统的需要。

系统中的SDRAM主要用以加载系统程序和开辟视频数据信息的存储缓冲区,Flash用于烧写调试完成后的系统加载程序。它们通过核心处理器BF561和BF537的外部总线接口单元(EBIU)进行扩展。

3 系统软件设计

3.1 视频采集压缩模块

视频采集压缩模块:由于BF561为双核处理器,为充分利用其双核结构来提高视频压缩能力,在这个模块的软件设计中,对系统工作量进行了合理的分配,系统加电后,首先在其主核中对系统进行初始化,设置系统的工作倍频,并对前端视频解码芯片ADV7183A进行配置,管理和前段视频解码器的通信传输工作,然后进入循环等待开始视频压缩命令,同时其另一个核也处于等待状态,在接收到视频压缩开始命令后,在主核中将前端采集的视频数据分割为上下各半帧数据,分别交给双核进行压缩处理,为保证每一帧压缩之后的视频数据的完整性,在每一帧视频数据压缩的前后采用了信号量同步的方式,保证了双核工作的同步性和视频数据输出的完整性,视频采集压缩处理部分程序流程如图2所示。

[page]

[page]

3.2 网络传输模块

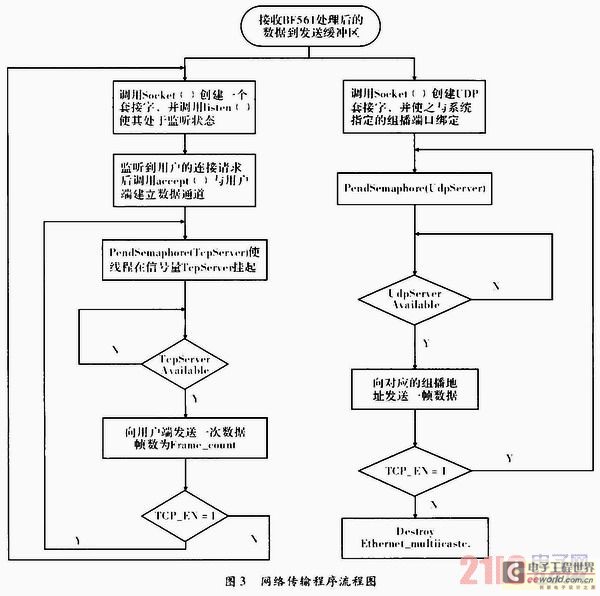

网络传输模块:网络传输模块主要负责本系统和用户之间的交互,包括接收用户命令和向用户提供视频数据流,其中向用户提供数据流包括发送视频数据和提供组播服务两种方式,视频采集压缩模块每压缩处理完一帧数据后,就通过中断的方式提醒BF537以DMA方式读取压缩完成后的视频数据,对于要求严格保证数据传输稳定性与可靠性的用户,网络传输模块以TCP的传输方式将读取的视频数据发送给指定用户,对于主要以局域网用户为主,用户数量不定,且对传输稳定性与可靠性要求不是很高的用户,网络传输模块采用DP的传输方式将读取的视频数据发送给组播中的群成员,这里之所以用组播的方式也为了节省网络带宽资源。在系统工作中为防止接收视频数据和发送之间的协调性,采用信号量的方式来约束接收和发送数据的逻辑,防止了发送重复数据或者空数据的问题,网络传输模块的程序流程如图3所示。

4 结束语

网络视频压缩系统利用核心处理器BF561、BF537以及外围芯片,完成视频信息的采集、压缩处理、网络传输等功能,能够满足视频监控系统的实时性和远程化要求,提供了单播和组播两种不同的远程监控方式。

上一篇:基于DSP的数字音频均衡器设计

下一篇:嵌入式系统在可配置系统中实现模拟I/O

推荐阅读最新更新时间:2024-05-02 22:09

图像处理、分析与机器视觉 (3th) (Milan Sonka、艾海舟)

图像处理、分析与机器视觉 (3th) (Milan Sonka、艾海舟) Verilog HDL数字集成电路设计原理与应用

Verilog HDL数字集成电路设计原理与应用

京公网安备 11010802033920号

京公网安备 11010802033920号