摘 要:本文分析了传统的多个DSP 的各种互联的方法,提出将串行RapidIO 协议,这种基于开关的、点对点的互连方法作为基带数据处理中的互连方案,可以减少成本,并且提供高带宽下低延时的双向通信。然后结合基站基带处理,这种方案具有很大的灵活性,最后总结了使用这种互连方案的好处。

目前,在通信系统中,比如在 VoIP 网关和无线基站的系统中,语音和数据都在急剧增加,系统的处理能力也要极大地增加,因此单个DSP 已经不能满足越来越多的需求,需要把多个DSP 互联成DSP 簇来增加对更多数据的更快处理能力。DSP 的互连有很多种,不同的应用场合可以使用不同的DSP 互联。比如基于总线的多DSP 结构复杂,而且因为共享总线造成总线带宽,降低系统整体的效率,总线瓶颈的限制将凸显出来;通过HPI 接口-可以提供DSP 之间的互联,但是数据传输速率有限,数据传输有时会成为系统处理能力提高的瓶颈,造成系统整体效率的降低;多通道缓冲串口MCBSP-数据传输带宽有限,他们都不适合多DSP 之间的高速数据传输。DSP 簇需要通过一种特殊的方式互联,以支持更高的带宽,同时进行低延时的双线通信。可以通过专用的互联芯片来实现多DSP 互联方案,这样,连接上不会复杂,而且具有灵活性和高速传输的特点。在无线基站中,如果利用RapidIO协议进行DSP 互连则可以大大提高运算效率。而且目前芯片的厂家已经生产出支持串行RapidIO 接口的芯片,使得DSP 之间高速互联成成为可能。

1. 系统介绍

1.1 串行RapidIO

RapidIO 商业联盟组织2001 年提出了针对多处理器互连的RapidIO 协议。RapidIO 协议是一个点对点的包交换协议, 有物理层、运输层和逻辑层3 层结构。逻辑层为RapidIO 节点的交易, 定义了所有的包格式:运输层为RapidIO 数据包提供了路由和寻址的功能;物理层提供了设备接口的电气特性说明此外, 协议还提供了流量控制、差错控制等功能。对于采用较少连线的长距离传输以及背板传输,由于RapidIO 物理层采用Lvds 传输和高速串行收发器技术,在每个方向上支持高达10-Gbps 的数据吞吐量,可用在图像和信号处理、高带宽存储器接口等领域中。

1.2 DSP 之间通过串行RapidIO 进行互连

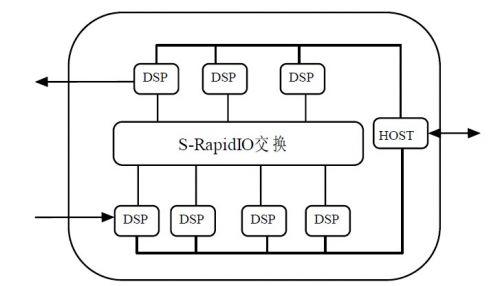

如果 DSP 簇的互连使用串行RapidIO 协议,可以大大提高吞吐量。如图1 所示:

图 1 一种初步的互连方案

可以看出,几个DSP 通过这种方法进行互连,利用两个DSP 分别从外部收集未处理的数据并将处理好的数据送出,在几个DSP 内部利用串行RapidIO 协议,数据在几个DSP 之间高速运转,正是因为RapidIO 这种基于点到点的传输特性才能使得高速传输的实现。另外,还可以通过一个外部的主机hoST 来实现控制这几个DSP 的一些功能,比如在某种场合可以只运行某个DSP 进行特殊运算,那么其他的DSP 则处于不工作的状态。这种DSP 之间使用串行RapidIO 互连有很多优点:

1、RapidIO 协议分为三层,所有DSP 可以集中处理码元速率和符号速率。

2、拥有可以升级的交织查找表,可以平衡几个 DSP 的工作量。

3、这种点到点的开关互连可以满足更高更复杂的要求,比如多用户检测等等。

4、协议中四种优先级设定,允许高优先级的优先通信。

5、RapidIO 中的数据流,可以选择第六种数据类型,允许数据传输具有更小的包头。

1.3 无线传输系统基带部分

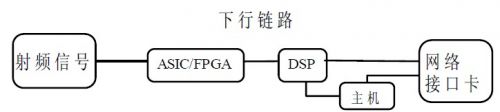

在无线传输中,模拟的用户数据经过射频模块进行模拟的转换,发送到基站的基带板接收,运行一系列的运算规则进行调制解调来分析用户数据。基带子系统完成信道解扩解调、编译码、扩频调制的功能。基带子系统对上行基带数据进行解调,包括相关、信道估计、频率跟踪和RAKE 合并等,然后经过译码处理、FP 处理传递给传输子系统。而在下行链路中,基带子系统接收到来自传输子系统的FP 包,根据要求完成编码,包括TB 块CRC 校验和码块分段、信道编码、速率匹配、交织、传输信道复用与物理信道映射等,将下行数据发送到中频子系统。其中,互相关、信道估计和多用户检测等通常都是用ASIC 和FPGA 来实现的,Viterbi 译码和turbo 译码等通常都是用DSP 实现的。如图2 所示:

图 2 基站基带处理板简化框图

传统的 ASIC/FPGA 构成的处理器,没有对等网络的要求,对语音、数据进行固定分配,处理效率比较低。因此可以考虑用DSP 来实现,但是单个DSP 只有一个内核,它的处理能力非常有限,处理数据的速度不及FPGA.如果多个多核协作进行并行计算,则可以成倍提高DSP 的处理能力,因此可以考虑多个DSP 互连。多个DSP 通过高速协议互连构成的DSP簇能够很灵活地实现多种功能,他们之间通过软件编程,可以非常灵活地适应更高复杂的要求,并且使对等网络通信成为可能,具有更高的吞吐量。

由于这种模块只有 DSP 在运算,需要进行负载均衡,对于处理链中的DSP 簇,需要给每个DSP 分配不同的算法模块。因为需要更高的数据速率并且需要更复杂的多用户运算,进行信道估计和检测,需要用多个DSP 对这些运算进行负载均衡,从而去实现更大的算法模块。比如说可以给每个DSP 相同的算法,也可以让每个DSP 本身成为一个独立的算法模块,这些都是非常灵活的。

2. 系统的具体实现

DSP 之间通过RapidIO 协议进行通信的实现方法,目前可以通过FPGA 实现,FPGA 作为DSP 节点本地互连网络协处理器,采用了分层结构,包括DSP 接口层、RapidIO 的逻辑层、运输层和物理层[4].DSP 通过外部存储器接口( EMIF) 和FPGA 相连。但是这种方法需要在FPGA 内部进行比较复杂的互连。目前,TUNDRA 公司推出了一款专门的串行RapidIO芯片--TSI568A.

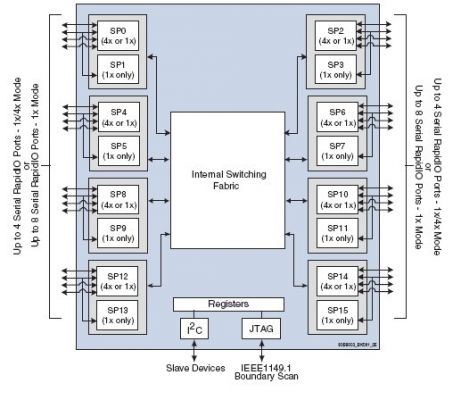

图 3 Tsi568a 的内部结构。[page]

Tsi568A 是一款业内最先进的串行RapidIO 交换机,支持高达每秒80GB 的总带宽。它高度的灵活性可以满足多个I/O 设备的带宽要求,每个端口可以配置成4x 模式或者1x 模式,这样可以为多个DSP 连接提供接口。Tsi568A 还支持RapidFabric 扩展,包括以交互工作和封装为目的的数据流分组交换。而且Tsi568a 支持热插拔I/O 设备。同时,TI 公司的TMS320C6455 系列DSP 也集成了串行RapidIO 接口,这样就可以实现DSP 簇之间进行无缝的串行RapidIO 通信。

图 4 互连的实现。

如图 3 所示接收端基带处理。自相关和多径估计由DSP1 和DSP2 中完成,信道估计和多用户检测由DSP3 和DSP5 完成,QPSK 和MRC 也由DSP5 处理,turbo 译码和viterbi 译码由DSP7 完成。还可以看出,给DSP4 和DSP6 并没有使用,这时候它们可以进入Power down模式,可以根据需要来决定是否使用某个DSP.

另外,上图只是接收端的基带处理,给每个 DSP 分配不同或者相同的功能,使得DSP处理板还可以在系统的多天线接收板,多天线发送板,基带接收处理板中使用。由于是对等的关系,采用适当的升级可以使发送和接收功能在一块板卡中灵活实现。除了功能上的差别外,不同单板需要的处理能力不同,可以选用不同的DSP 来适应。如果处理能力要求不高,可以选用工作频率较低的6455-720 或者6455-850;如果处理能力要求比较高,则可选用工作频率最高的6455-1000.这种模块处理机制,每个DSP 都执行这一系列信道处理的功能,在某些时候几个DSP 可以进入Power down 模式,TSI568a 也能够中断没有使用的端口以节省功率。而在高通信量的时候可以使能所有的DSP 工作。

借助 Tsi568A 系列交换机,可以通过多种端口带宽和频率选项,可以选择灵活的端口配置各个DSP.系统基于串行RapidIO 规范,拥有多种功能:SerDes、错误恢复、给予优先级的体系路由、高有效载荷和基于表格的体系分组路由。由于拥有广泛缓冲和流量管理架构,可以有效防止线路中枢发生堵塞。Tsi568a 提供了芯片到芯片的互联,因此几个DSP 的数据传输是点到点的。同时,Tsi568A 可以通过区分数据包的优先级来提供流量汇总功能,通过自己的无阻塞体系来提供高性能的对等通讯。通过x4 串行RapidIO 连接,可以具有更高的信道密度,承载更高的吞吐量。

3. 结论

在基站的基带处理结构中灵活使用串行 rapidio 协议,能够减少复杂度,使电路板的设计更加简单,发送和接收功能更加灵活地在一块板卡中实现;并且多个DSP 同时执行并行计算提升了基带处理的能力;允许更灵活的现场切换;弥补了传统互联方案的不足,具有可升级的空间,可以通过软件改进对算法和数据路径进行升级。

上一篇:基于DSP的恒流充电电源设计方案

下一篇:基于3G时代的DSP技术应用

推荐阅读最新更新时间:2024-05-02 22:34

RapidIO™ Interconnect Specification

RapidIO™ Interconnect Specification 零基础学电子与Arduino:给编程新手的开发板入门指南

零基础学电子与Arduino:给编程新手的开发板入门指南

京公网安备 11010802033920号

京公网安备 11010802033920号