您可以显著提高无线系统中信号处理功能的性能。怎样提高呢?有效方法是利用FPGA结构的灵活性和目前受益于并行处理的FPGA架构中的嵌入式DSP模块。

常见于无线应用中这类处理包括有限冲激响应(FIR)滤波、快速傅里叶变换(FFT)、数字上下变频和前向误差校正(FEC)。Xilinx? Virtex-4和Virtex-5架构提供多达512个并行嵌入式DSP乘法器,这些乘法器的工作频率高于500MHz,最高可提供256 GMAC的DSP性能。

将需要高速并行处理的工作卸载给FPGA,而将需要高速串行处理的工作留给处理器,这样即可在降低系统要求的同时优化整体系统的性价比。

子系统划分选择方案

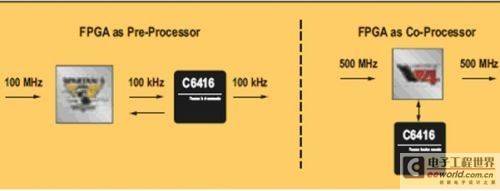

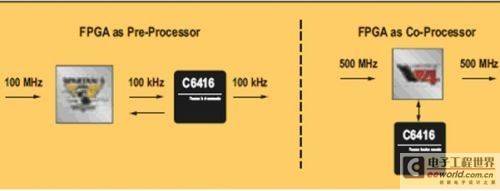

FPGA可与DSP处理器一起使用,作为独立的预处理器(有时是后处理器)器件,或者作为协处理器。在预处理架构中,FPGA直接位于数据通路中负责信号预处理,预处理后的信号可以高效又经济地移交给DSP处理器进行速率较低的后续处理。

在协处理架构中,FPGA与DSP并列而置,后者将特定算法函数卸载给FPGA,以便实现比单独采用DSP处理器能达到的速度更高的处理速度。FPGA的处理结果传回DSP,或者送至其他器件进一步进行处理、传输或存储(图1)。

选择预处理、后处理还是协处理,常常取决于在处理器和FPGA之间移动数据所需的时序余量及其对整体延迟的影响。虽然协处理解决方案是设计人员最常考虑的拓扑结构(主要是因为DSP可以更直接地控制数据移交过程),但这并不一定总是最佳的总体策略。

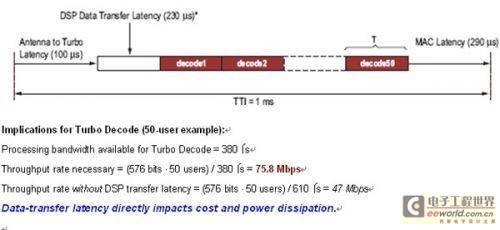

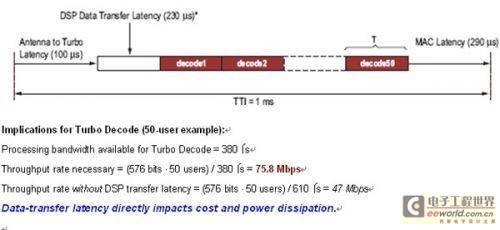

例如,最新的3G LTE规范将传输时间间隔(TTI)从HSDPA的2ms和WCDMA的10ms缩短到了1ms。这实质上是要求从接收器一直到MAC层输出之间的数据处理时间短于1,000?sec。

图1:FPGA 用作预处理器和协处理器的解决方案

如图2所示,在运行速度为3.125Gbps的DSP上使用SRIO端口(使用8b/10b编码,Turbo解码功能需要200比特的额外开销)会造成230?sec的DSP到FPGA传输延迟(也就是说TTI时段中有将近四分之一仅用来传输数据)。加之其他可预见的延迟,为满足这些系统时序,当用户为50个时,所需的Turbo编解码器性能就是高达75.8Mbps。

图2:协处理数据传输延迟问题的 LTE 示例

使用FPGA将Turbo编解码器作为基本上独立的后处理器来处理,不仅可消除DSP延迟,还能节省时间,因为不需要以高带宽在DSP和FPGA之间传输数据。这样做可将Turbo解码器的吞吐量降至47Mbps,因而可选用更多比较经济的器件,并且可以减少系统功耗。

另一项考虑是在XilinxFPGA上是否使用软嵌入式或硬嵌入式处理器IP来卸载某些系统处理任务,进而可能进一步减少成本、功耗和占用空间。有了如此大量的信号处理资源,就可以在DSP处理器、FPGA可配置逻辑块(CLB)、嵌入式FPGA DSP模块和FPGA嵌入式处理器之间更好地分配各种复杂功能(如基带处理中的复杂功能)。Xilinx提供了两种类型的嵌入式处理器:MicroBlaze软核处理器(常用于系统控制)和性能更高的PowerPC硬核嵌入式处理器(用于更复杂的任务)。

FPGA嵌入式处理器提供的有利条件允许将所有非关键性操作都合并到在嵌入式处理器上运行的软件中,从而尽量减少整体系统所需的硬件资源总量。

软件和IP的重要性

关键问题是如何将这种潜在能力全部释放出来。必须考虑需要用哪些软件对问题的复杂性进行抽象以及可以使用哪些IP,应该考虑利用FPGA为关键部分提供最佳解决方案。

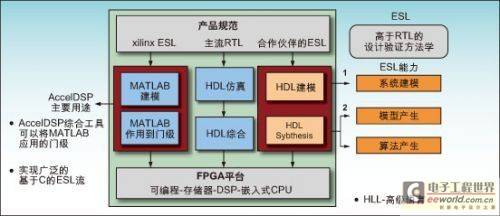

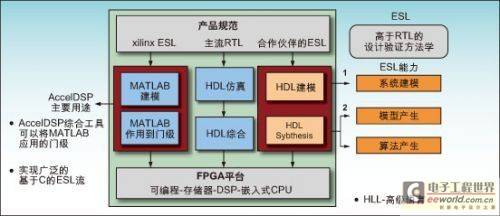

Xilinx致力于开发行业领先的工具和体系,能够在比HDL工具(如MATLAB模型和C代码)所能提供的更高的抽象层上实现高效的FPGA解决方案。利用Xilinx专门用于DSP的系统生成开发工具和AccelDSP综合工具,可以尽可能无缝实现从算法到硅片的链接。

目前有一个日益重要的工具提供商团队,其产品通过C/C++到逻辑门的设计流程把开发提升到电子系统级(ESL)。ESL设计工具的目的是提供一种完备的系统级方法,以便生成和集成硬件加速功能以及控制这些功能的处理器的控制代码。

没有哪一种高级语言或软件工具能适合当今复杂系统中所见的所有不同单元。语言和设计流程的选择取决于客户,有时取决于具体的工程师。因此,Xilinx开发了一套齐全的集成功能,以满足客户需求并提供最佳设计环境(见图3)。

图3:系统级到 FPGA 设计流程

本文小结

另外,Xilinx正在斥巨资提供一套功能广泛的高价值IP、电路板和参考设计,以涵盖射频卡和基带应用中的许多关键部分,其中包括FFT/iFFT、调制、数字上下变频和波峰系数的降低电路等。

这一重点举措的一个例子是开发针对特定无线标准和FPGA架构优化的行业领先的高性能FEC功能,如Turbo编码器和解码器。正如我们在分析3GLTE延迟和Turbo解码器流量要求时所示,FEC功能的硬件加速及其对系统架构的作用在现代无线设备设计中是日渐紧要的当务之需。

虽然一些专家级DSP处理器陆续以嵌入式模块的形式集成这类功能,但是,从制订出符合新无线标准的FEC功能参数到形成嵌入式加速模块出现在硅片中,通常需要好几个月。一旦实现了嵌入,也还会有遗留的难题,偶尔还会有嵌入式模块中的功能并非都能按要求工作的局面出现。同时,标准演化迅速,现标准中不时纳入一些固定嵌入式模块不能支持的新要求。

关键字:IP 信号处理 FPGA

引用地址:

基于DSP+FPGA协处理架构的无线子系统设计

推荐阅读最新更新时间:2024-05-02 23:00

压力传感器由压力敏感元件和信号处理单元组成

通常由压力敏感元件和信号处理单元组成。按不同的压力类型,压力可分为表压传感器、差压传感器和绝压传感器。

[机器人]

让我们看得更清楚—探索高清视频监控

2008年对于安防行业来讲,是高速发展的一年,城市的现代化建设和经济的快速发展,构建和谐社会的要求,对城市各行业系统的安防监控工作提出了许多新的要求和课题。同时,平安城市项目、奥运会的召开,都为安防行业的发展提供了广阔的平台,促进了行业内技术的发展。而安防行业中目前占有非常重要地位的视频监控产品,在安防市场高速发展的同时,也暴露出许多问题。

随着视频监控技术的高速发展,客户对于视频监控产品的要求也在不断提高,功能要求更加完善、稳定,性能要求更加清晰、准确。与此同时,在商场、储蓄所等监控场所如何看清一个人的面部特征?如何看清楚高速行驶车辆的牌照?拥挤喧闹的火车站、体育场馆、广场等场合,如何能够迅速准确的找到目标……?这些

[安防电子]

基于FPGA的数字稳定校正单元的实现

摘要:为了实现对非相干雷达的接收相参处理,基于数字稳定校正(DSU)的原理,采用ALTERA公司的StratixⅡ系列芯片和VHDL编程语言,设计了一种基于FPGA的DSU硬件实现方法。实验结果表明基于FPGA的DSU方法可以提高程序的执行效率和系统的实时性,可实现非相参雷达的相参化功能。 关键词:雷达;数字稳定校正单元;相参;FPGA 雷达从体制上可以分为相参雷达和非相参雷达,由于磁控管发射机的起始相位不固定、存在幅度抖动和频率漂移,对接收回波无法做相参积累,所以采用磁控管发射机的雷达属于非相参雷达。而现代信号处理中相参积累可以获得更大的增益和更多的功能,例如成像或动目标检测都需要发射和接收信号具有相参性。因此对原有非相

[嵌入式]

英特尔发布行业首款集成高带宽内存、支持加速的 FPGA

近日,英特尔宣布推出英特尔® Stratix® 10 MX FPGA,该产品是行业首款采用集成式高带宽内存 DRAM (HBM2) 的现场可编程门阵列 (FPGA)。通过集成 HBM2,英特尔 Stratix 10 MX FPGA 可提供 10 倍于独立 DDR 内存解决方案的内存带宽1。凭借强大带宽功能,英特尔 Stratix 10 MX FPGA 可用作高性能计算 (HPC)、数据中心、网络功能虚拟化 (NFV) 和广播应用的基本多功能加速器,这些应用需要硬件加速器提升大规模数据移动和流数据管道框架的速度。 在 HPC 环境中,大规模数据移动前后数据的压缩和解压缩功能至关重要。相比独立的 FPGA,集成 HBM2 的 F

[嵌入式]

基于FPGA的HDLC转E1传输控制器的实现

摘 要:本文介绍了一种用FPGA实现的HDLC转E1的协议控制器,能实现将速率为N%26;#215;64Kbps(N=1"124)的HDLC数据分接至M路(M=1"4)E1信道中传输,并允许各路E1的最大时延为64ms。讨论了E1帧结构设计和系统的FPGA实现方法。

关键词: 帧结构;HDLC;E1;FPGA

引言

E1是我国电信传输网一次群使用的传输标准,由于我国的E1资源十分丰富, 这样的传输路径非常容易获得,灵活利用现有丰富的E1信道来传输HDLC数据,可以节约大量传输成本。通常,一路HDLC数据仅通过一路E1信道传输,但是如果HDLC数据的速率很大,一路E1信号的带宽不足以传输,那么HDLC数据就要分接到M

[网络通信]

28nm Stratix V FPGA抢先解析

日前,Altera公布了其28nm Stratix V FPGA的性能参数指标,并透露该款芯片最早发售日期为2011年一季度。 与Altera Stratix IV及Xilinx Virtex-6对比 根据已公布的Stratix IV及刚刚公布的Stratix V,我们对于两代产品的性能参数做了一个大致比较。 Stratix V Stratix IV Virtex-6 逻辑单元 1.1M 820K 760K 乘法器 可变精度 18*18 25*18 存储器 53Mbit 23.1Mbits

[嵌入式]

基于FPGA的LDPC编码器设计与实现

引言 低密度奇偶校验(Low Density Parity Check Code,LDPC)码是一类具有稀疏校验矩阵的线性分组码,不仅有逼近Shannon限的良好性能,而且译码复杂度较低, 结构灵活,是近年信道编码领域的研究热点,目前已广泛应用于深空通信、光纤通信、卫星数字视频和音频广播等领域。LDPC码已成为第四代通信系统(4G)强有力的竞争者,而基于LDPC码的编码方案已经被下一代卫星数字视频广播标准DVB-S2采纳。 编码器实现指标分析 作为前向纠错系统的重要部分,设计高速率低复杂度LDPC码编译码器成为提高系统性能的关键。对LDPC码来说,其编码复杂度相对较大,编码器的设计与实现是首要任务,也是译码器设计与实现的前提

[应用]

利用DSP技术与软件的企业IP电话解决方案

引言

从最初的概念展示,一直到目前的广泛应用,VoIP(Voice over IP)市场的成长可说极为快速。透过VoIP网关的实际安装布署,下一代的电信厂商不但已经开始提供全球性的IP电话服务,其成本也低于传统的通话方式。事实上,只要利用现有的分组交换网络基础设施,然后再使用IP电话网关以及客户端设备,厂商就可大幅降低电话服务的成本,这包括了语音与传真服务。今天,在所有实际应用的VoIP解决方案中,几乎都可以看到数字信号处理器(DSP)的踪迹,在这些解决方案的成功经验中,DSP芯片与软件都扮演了极为重要的角色。目前,许多企业的电话系统都采用专用电话交换机设备,因此为了继续支持这些服务,下一代的IP电话产品也会

[应用]

汽车电子的革新与FPGA-24页

汽车电子的革新与FPGA-24页 硬件架构艺术:数字电路的设计方法与技术

硬件架构艺术:数字电路的设计方法与技术

京公网安备 11010802033920号

京公网安备 11010802033920号