频率合成器是决定电子系统性能的关键设备,随着通信、数字电视、卫星定位、航空航天、雷达和电子对抗等技术的发展,对频率合成器提出了越来越高的要求。频率合成理论自20世纪30年代提出以来,已取得了迅速的发展,逐渐形成了直接频率合成技术、锁相频率合成技术、直接数字式频率合成技术三种基本频率合成方法。直接频率合成技术原理简单,易于实现,频率转换时间短,但是频率范围受限,且输出频谱质量差。锁相频率合成技术(PLL)具有输出频带宽、工作频率高、频谱质量好的优点,但是频率分辨率和频率转换速度却很低。直接式数字频率合成技术(DDS)的频率分辨率高、频率转换时间快、频率稳定度高、相位噪声低,但目前尚不能做到宽带,频谱纯度也不如PLL。低相位噪声、高纯频谱、高速捷变和高输出频段的频率合成器已成为频率合成发展的主要趋势,传统的单一合成方式很难兼顾上述各项性能指标,达到现代通信系统对频率合成器的要求。本文采用DDS和PLL相结合的方法,设计一个应用于(GSM 1 800 MHz系统中的频率合成器,其中输出频带为1 805~1 880 MHz,分辨率为200 kHz,相位噪声为-80 dBc/Hz@1 kHz,频率误差为5 kHz,杂波抑制大于50 dB。

1 电路设计

1.1 设计原理

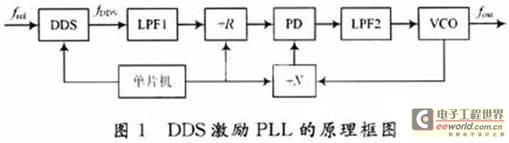

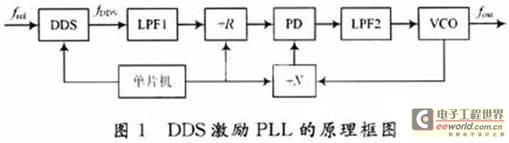

DDS直接激励PLL的频率合成技术,与单纯的PLL技术相比,作为参考源的DDS具有很高的频率分辨率,可以在不改变PLL分频比的情况下,提高PLL的频率分辨率,而且采用DDS激励PLL设计方法的电路结构简单,所用硬件少,通过合理设计环路滤波器可以较好地改善因PLL倍频作用而恶化的相位噪声。系统原理框图如图1所示。

图1中,fref是参考信号,一般由高稳定度的晶体振荡器产生,用于保证DDS各个部件的同步工作。fDDS取代原有的晶振作为锁相环(PLL)的激励源,其输出fDDS频率取决于频率控制字K。频率合成器的输出由VCO提供,PLL芯片中电荷泵的输出由低通滤波器(LPF2)产生,用于控制VCO的输出频率。DDS中K和PLL的分频比可以通过单片机中的控制程序加以改变,从而实现频率合成。

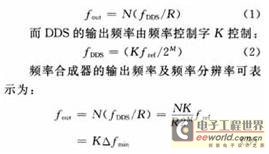

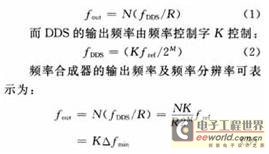

VCO输出信号频率与DDS输出信号频率之间的关系为:

式中:fref为DDS的时钟频率;K为DDS的频率控制字;M为DDS相位累加器字长;fref/2M为DDS的频率分辨率;△fmin为频率合成器输出信号的频率分辨率。由此可见,以DDS为激励源,只要相位累加器的字长取得足够大,频率合成器就能得到较高的频率分辨率。

1.2 电路实现

如图1给出的原理框图所示,整个频率合成器由DDS和PLL两个功能模块实现。

1.2.1 DDS电路

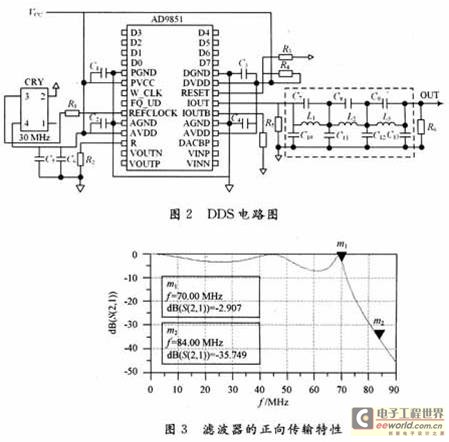

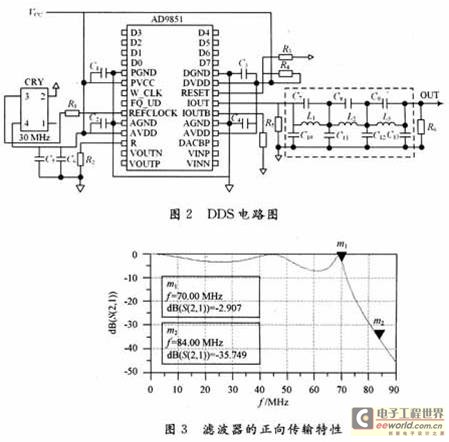

DDS电路如图2所示,该电路由DDS、低通滤波器(LPF)和外部参考时钟源组成。电路中的直接数字频率合成器芯片AD9851是AD公司采用先进的DDS技术生产的高集成度DDS器件。它允许最高输入时钟180 MHz,同时提供可选择的片内6倍频乘法器,内置高性能的10 b数/模转换器,内含一个高速比较器。芯片具有简单的控制接口,允许串/并行异步输入控制字,采用32 b频率控制字,内部使用5 b相位调制字,外接参考时钟源时,AD9851可以产生一个频谱纯净、频率和相位都可以控制,而且稳定性非常高的正弦波。

本文采用单片机C8051F021实现对AD9851数据控制,改变AD9851内部编程控制寄存器所选的操作模式、相位累加器的位数、频率控制字,可实现各种不同频率信号的输出。外部参考时钟源选用30 MHz无源晶振,DDS输出信号的频率最高可达72 MHz。外部的低通滤波器用来滤除高频杂散和谐波。

DDS有一个很明显的缺点,输出频率越接近Nyquist带宽的高度,采样点数越少,其输出的杂散干扰也就越大。因此,必须在DDS芯片的正弦信号输出端加一个滤波器,以便有效地抑制谐波和杂散。本设计中采用七阶椭圆低通滤波器,该滤波器电路如图2虚线框内所示,其中R5,R6完成电流信号到电压信号的转换,其截止频率可达70 MHz。图3给出该七阶椭圆低通滤波器的正向传输特性,70 MHz截止频率衰减为-2.907 dB,带外衰减在84 MHz达到-35.749 dB,基本符合设计要求。

1.2.2 PLL电路

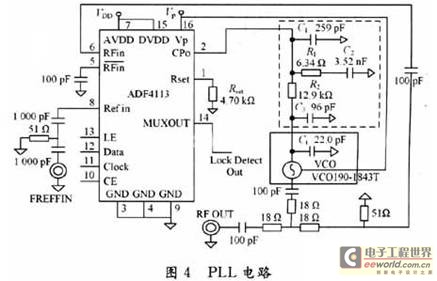

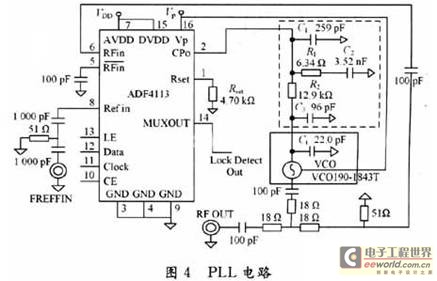

PLL电路如图4所示,该电路由性价比很高的锁相芯片ADF4113、滤波电路、VC0构成。设计中采用DDS输出取代原有的晶振,为GSM系统提供13 MHz的激励源,信道频率间隔为200 kHz,基准输入需经ADF4113中的基准分频器完成65分频。

ADF4113是ADI公司研制的数字锁相频率合成器,最高工作频率可达4 GHz,可用于无线射频通信系统的基站、手机、通信检测设备及CATV设备中。该芯片内部主要包括可编程的14位基准分频器;可编程双模式前置分频器:8/9,16/17,32/33和64/65;可编程的射频信号分频器;3线串行总线接口;模拟和数字锁定状态检测功能。该芯片具有良好的相位噪声参数,鉴相频率为200 kHz时,相噪基底为-164 dBc/Hz;输出1 840 MHz时,相噪可达-85 dBc/Hz。VCO选用Sirenza微波公司的VC0190-1843T,输出频率范围为1 740~1 930 MHz,具有良好的相位噪声特性,其独特的缓冲放大器设计,可减小频率漂移。

环路滤波器对频率合成器的性能有十分重要的影响,环路滤波器决定频率合成器的杂散抑制、相位噪声、环路稳定性以及捷变时间等重要参数。由于本设计采用ADF4113电流型电荷泵鉴相器,因此环路滤波器采用无源方式。鉴于本系统对跳频的切换时间要求不是很高,因此可以适当降低环路带宽,以确保系统稳定性。降低环路带宽还有助于滤除参考信号中的谐波成分。但环路带宽太小会增加建立时间和带内VCO相位噪声,由于带内噪声主要取决于参考信号引入的噪声,VC0相位噪声不是主要因素。该系统设计成三阶无源滤波器构成的四阶环路。图4虚线框给出三阶无源环路滤波器电路,根据系统对相位噪声和频率转换时间的要求,取环路带宽ωc=15 kHz,相位裕度为φ=45°。

2 电路仿真

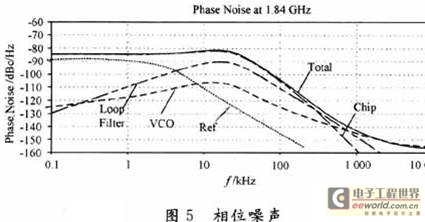

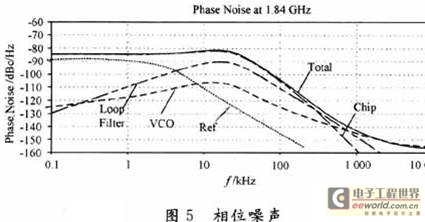

采用ADISimPLL软件对该方案进行了仿真分析,图5给出仿真结果。可以看出,该频率合成器的相位噪声为-84.63 dBc/

3 结果分析

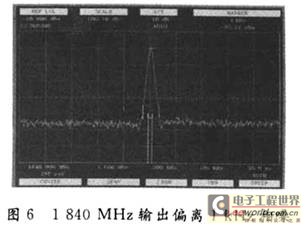

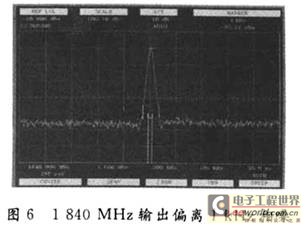

系统采用DDS直接激励PLL的设计方案,充分利用了DDS小步进、频率捷变快及PLL频带宽,工作频率高,频谱纯度高的优点,研制出满足GSM l 800 MHz系统指标要求的频率合成器。相位噪声的测量如图6所示,为-83.75 dBc/

4 结语

采用DDS激励PLL的频率合成技术,克服了宽带系统中DDS输出频率较低和PLL频率分辨率低的缺点。通过合理设计环路低通滤波器、相位噪声、环路稳定性等性能得到提高,并对电源采取滤波措施,以改善杂波抑制,最终设计出高性能频率合成器。

关键字:DDS PLL 频率合成器

引用地址:基于DDS+PLL高性能频率合成器的设计与实现

1 电路设计

1.1 设计原理

DDS直接激励PLL的频率合成技术,与单纯的PLL技术相比,作为参考源的DDS具有很高的频率分辨率,可以在不改变PLL分频比的情况下,提高PLL的频率分辨率,而且采用DDS激励PLL设计方法的电路结构简单,所用硬件少,通过合理设计环路滤波器可以较好地改善因PLL倍频作用而恶化的相位噪声。系统原理框图如图1所示。

图1中,fref是参考信号,一般由高稳定度的晶体振荡器产生,用于保证DDS各个部件的同步工作。fDDS取代原有的晶振作为锁相环(PLL)的激励源,其输出fDDS频率取决于频率控制字K。频率合成器的输出由VCO提供,PLL芯片中电荷泵的输出由低通滤波器(LPF2)产生,用于控制VCO的输出频率。DDS中K和PLL的分频比可以通过单片机中的控制程序加以改变,从而实现频率合成。

VCO输出信号频率与DDS输出信号频率之间的关系为:

式中:fref为DDS的时钟频率;K为DDS的频率控制字;M为DDS相位累加器字长;fref/2M为DDS的频率分辨率;△fmin为频率合成器输出信号的频率分辨率。由此可见,以DDS为激励源,只要相位累加器的字长取得足够大,频率合成器就能得到较高的频率分辨率。

1.2 电路实现

如图1给出的原理框图所示,整个频率合成器由DDS和PLL两个功能模块实现。

1.2.1 DDS电路

DDS电路如图2所示,该电路由DDS、低通滤波器(LPF)和外部参考时钟源组成。电路中的直接数字频率合成器芯片AD9851是AD公司采用先进的DDS技术生产的高集成度DDS器件。它允许最高输入时钟180 MHz,同时提供可选择的片内6倍频乘法器,内置高性能的10 b数/模转换器,内含一个高速比较器。芯片具有简单的控制接口,允许串/并行异步输入控制字,采用32 b频率控制字,内部使用5 b相位调制字,外接参考时钟源时,AD9851可以产生一个频谱纯净、频率和相位都可以控制,而且稳定性非常高的正弦波。

本文采用单片机C8051F021实现对AD9851数据控制,改变AD9851内部编程控制寄存器所选的操作模式、相位累加器的位数、频率控制字,可实现各种不同频率信号的输出。外部参考时钟源选用30 MHz无源晶振,DDS输出信号的频率最高可达72 MHz。外部的低通滤波器用来滤除高频杂散和谐波。

DDS有一个很明显的缺点,输出频率越接近Nyquist带宽的高度,采样点数越少,其输出的杂散干扰也就越大。因此,必须在DDS芯片的正弦信号输出端加一个滤波器,以便有效地抑制谐波和杂散。本设计中采用七阶椭圆低通滤波器,该滤波器电路如图2虚线框内所示,其中R5,R6完成电流信号到电压信号的转换,其截止频率可达70 MHz。图3给出该七阶椭圆低通滤波器的正向传输特性,70 MHz截止频率衰减为-2.907 dB,带外衰减在84 MHz达到-35.749 dB,基本符合设计要求。

1.2.2 PLL电路

PLL电路如图4所示,该电路由性价比很高的锁相芯片ADF4113、滤波电路、VC0构成。设计中采用DDS输出取代原有的晶振,为GSM系统提供13 MHz的激励源,信道频率间隔为200 kHz,基准输入需经ADF4113中的基准分频器完成65分频。

ADF4113是ADI公司研制的数字锁相频率合成器,最高工作频率可达4 GHz,可用于无线射频通信系统的基站、手机、通信检测设备及CATV设备中。该芯片内部主要包括可编程的14位基准分频器;可编程双模式前置分频器:8/9,16/17,32/33和64/65;可编程的射频信号分频器;3线串行总线接口;模拟和数字锁定状态检测功能。该芯片具有良好的相位噪声参数,鉴相频率为200 kHz时,相噪基底为-164 dBc/Hz;输出1 840 MHz时,相噪可达-85 dBc/Hz。VCO选用Sirenza微波公司的VC0190-1843T,输出频率范围为1 740~1 930 MHz,具有良好的相位噪声特性,其独特的缓冲放大器设计,可减小频率漂移。

环路滤波器对频率合成器的性能有十分重要的影响,环路滤波器决定频率合成器的杂散抑制、相位噪声、环路稳定性以及捷变时间等重要参数。由于本设计采用ADF4113电流型电荷泵鉴相器,因此环路滤波器采用无源方式。鉴于本系统对跳频的切换时间要求不是很高,因此可以适当降低环路带宽,以确保系统稳定性。降低环路带宽还有助于滤除参考信号中的谐波成分。但环路带宽太小会增加建立时间和带内VCO相位噪声,由于带内噪声主要取决于参考信号引入的噪声,VC0相位噪声不是主要因素。该系统设计成三阶无源滤波器构成的四阶环路。图4虚线框给出三阶无源环路滤波器电路,根据系统对相位噪声和频率转换时间的要求,取环路带宽ωc=15 kHz,相位裕度为φ=45°。

2 电路仿真

采用ADISimPLL软件对该方案进行了仿真分析,图5给出仿真结果。可以看出,该频率合成器的相位噪声为-84.63 dBc/

3 结果分析

系统采用DDS直接激励PLL的设计方案,充分利用了DDS小步进、频率捷变快及PLL频带宽,工作频率高,频谱纯度高的优点,研制出满足GSM l 800 MHz系统指标要求的频率合成器。相位噪声的测量如图6所示,为-83.75 dBc/

4 结语

采用DDS激励PLL的频率合成技术,克服了宽带系统中DDS输出频率较低和PLL频率分辨率低的缺点。通过合理设计环路低通滤波器、相位噪声、环路稳定性等性能得到提高,并对电源采取滤波措施,以改善杂波抑制,最终设计出高性能频率合成器。

上一篇:数字信号控制器提供实时控制功能

下一篇:基于ARM核和DSP核的OMAP5910嵌入式系统

推荐阅读最新更新时间:2024-05-02 23:01

基于单片机和CPLD的DDS正交信号源滤波器的设计

1 前 言 由于传统的多波形函数信号发生器需采用大量分离元件才能实现,且设计复杂,这里提出一种基于CPLD的多波形函数信号发生器。它采用CPLD作为函数信号发生器的处理器,以单片机和CPLD为核心,辅以必要的模拟和数字电路,构成的基于DDS(直接数字频率合成)技术、波形稳定、精度较高的多功能函数信号发生器。 2 系统设计 图1给出系统设计框图,该系统设计主要由CPLD电路、单片机电路、键盘输入液晶显示输出电路以及D/A转换电路和低通滤波器等电路组成。 2.1 频率合成器 该系统设计采用直接数字式频率合成DDS(Direct Digital Frequency Synthesis)技术,采用ROM存储

[单片机]

基于DDS跳频信号源的设计与实现

0 引言 跳频通信具有较强的抗干扰、抗多径衰落、抗截获等能力,已广泛应用于军事、交通、商业等各个领域。频率合成器是跳频系统的心脏,直接影响到跳频信号的稳定性和产生频率的准确度。目前频率合成主要有三种方法:直接模拟合成法、锁相环合成法和直接数字合成法(DDS)。直接模拟合成法利用倍频(乘法)、分频(除法)、混频(加法与减法)及滤波,从单一或几个参考频率中产生多个所需的频率。该方法频率转换时间快(小于100ns),但是体积大、功耗高,目前已基本不用。锁相环合成法通过锁相环完成频率的加、减、乘、除运算。该方法结构简单、便于集成,且频谱纯度高,目前使用比较广泛,但存在高分辨率和快转换速度之间的矛盾,一般只能用于大步进频率合成技术中。D

[嵌入式]

基于DDS芯片AD9852的基准源设计

0 引 言 直接数字频率合成(DD6)是一种以固定的精确时钟源为基准,利用数字处理模块产生频率和相位均可调的输出信号的技术。随着超大规模集成电路和微电子技术的发展,现代高性能、高集成度和小体积的DDS产品正快速取代传统的模拟信号频率合成技术,成为了这类问题新的解决方案。本文利用FPGA计算出相应的频率控制字,并对DDS芯片AD9852进行编程,最终得到所要求的输出波形。 1 系统总体方案设计 基准源主要由上位机控制、FPGA控制、DDS、参考源、调制信号源及波形输出模块组成,如图1所示。上位机控制单元是由计算机通过USB总线连接至电路板进行控制操作。FPGA控制单元实现与上位机控制单元交互信息,同时以并行

[电源管理]

一种新的实现DDS的AVR信号发生器

这是一个AVR DDS信号发生器V2.0新的实施,已经在scienceprog.com出版。 很明显,对于原原理图和固件完全归功于它的原创者。这里呈现的是一个不同的PCB,结构紧凑,单只通孔,便于建筑构件片面的。函数发生器有两个BNC输出:为高速 一平方信号(BNC1)和DDS的信号(BNC2)另一个。偏移和幅度可以用两个调节电位器:在+5 V至- 5V(POT1)和0至10V(POT2)范围幅度范围偏移。向上和向下箭头按钮用于改变函数的类型(正弦,三角等),而左,右箭头按钮用于改变频率值。还有一个改变频率步进单独的菜单。当中间按钮按下时,产生的信号启动。示意图 EAGLE示意图(仅一个状态LED和开/关

[单片机]

AT89C2051控制LMX2332的频率合成器

摘要:LMX2332是美国国家半导体公司生产的集成数字锁相环(PLL)电路。文章介绍了利用单片机AT89C2051控制数字锁相环LMX2332及压控振荡器JTOS-150实现低噪声频率源的方法,该方法可通过改变AT89C2051的程序得到不同频率的信号。

关键词:AT89C2051;单片机;锁相环;LMX2332;频率合成器

1 引言

数字式频率合成器能提供长期频率稳定度与短期频率稳定度都比较高且杂波少的信号输出,而且,波道数目多、体积小、易于数字化和集成化。数字锁相环构成的数字式频率合成器是目前通信、仪表、雷达等电子技术中广泛应用的一种频率合成技术,它的基本组成如图1所示。

该环路的输入端有一个数字参考分频器%26;#

[单片机]

基于ADF4360_4的混频器本振源电路设计

0 引言 锁相(Phase Lock)技术是一种相位负反馈频率控制技术,该技术在锁定时无剩余频差,并具有良好的窄带载波跟踪性能和带宽调制跟踪性能,而且对相位噪声和杂散也具有很好的抑制作用。因此,通过锁相频率合成技术实现的频率源已在通信、电视等领域得了广泛应用。本文介绍的ADl公司的ADF4360系列芯片就是用于无线通信射频系统(GSM,DECT,PCS,WCDMA。DCS)基站和WLAN混频电路的一款性价比很高,且应用范围较广的锁相芯片。 1 ADF4360_4的性能特点 ADF4360_4丰要由数字鉴相器、电荷泵、R分频器、A,B计数器及双模前置P/P+1分频器等组成。数字鉴相器对R计数器与N计数器的输出信

[模拟电子]

为微控制器增加PWM/模拟通道的方法

微控制器是将微型计算机的主要部分集成在一个芯片上的单芯片微型计算机。在片上PWM(脉冲宽度调制)资源方面,低成本的8位单片微控制器是很吝啬的。设计人员在采用PWM资源时,经常被迫要牺牲一个捕捉/比较通道或定时器通道,因为PWM通道要共用相同的片上资源。很多基于微控制器的独立电气设备都不会使用同步串行端口。因此,可以用微控制器的波特率发生器和并/串转换器部分来生成位模式,构成一个256位的PWM形式。然后用RC滤波器过滤这个PWM输出,提取出一个模拟信号。同步通信没有异步通信的起始位和停止位,因此位模式可以产生出长周期的高电平或低电平。

图1,可以用片上未用的同步串行端口产生PWM信号,并将其转换为

[电源管理]

基于内插和QLA技术的并行DDS的实现

1 引 言 直接数字频率合成技术(Direel Digital FrequencySynthesis,DDS)称为第三代频率合成技术,他利用正弦信号的相位与时间呈线性关系的特性,通过查表的方式得到信号的瞬时幅值,从而实现频率合成。这种方法不仅可以产生不同频率的正弦波,而且具有超宽的相对带宽,超高的变频速率,超细的分辨率以及相位的连续性和产生任意波形(AWG)的特点。 目前所使用的大部分DDS结构,在相位累加模块和相位幅度转换模块均采用了流水线技术和某些压缩算法等,但都不能从根本上解决DDS的输出频率受外部时钟频率约束的瓶颈以及波形的输出质量受查找表容量限制的问题。因此在对DDS的结构进行深入研究的基础上,我们在相位

[嵌入式]

小广播

热门活动

换一批

更多

最新嵌入式文章

更多精选电路图

更多热门文章

更多每日新闻

更多往期活动

- 有奖直播:借助Maxim的模拟技术优化设计

- TI 邀您填问卷赢好礼|私人定制专属你的 2019 工业应用方案

- TI工业月参考设计亮点抢先看

- TE助力数据中心设计,缩短你与奥运的距离,猜猜它属于哪个“奥运场馆”赢大礼!

- 更好的你我,更好的EEWorld!2020年终庆典

- 有奖直播|MPS电感解决方案,助力更好的开关电源设计

- TI E2E中文社区年终回馈,15 块 CC3200-LAUNCHXL 开发板免费申请中……测评赢好礼喽!

- 雅特力AT32WB415系列蓝牙BLE 5.0 MCU,免费抢鲜体验!

- 我们猜啦!MDO3000之竞猜有奖:免费的部分会值多少?

- 直播【英飞凌应用于变频家电和中小功率工业变频控制领域的产品:iMOTION™】

11月21日历史上的今天

厂商技术中心

高频电路设计与制作 (市川裕一,青木胜,卓圣鹏 著)

高频电路设计与制作 (市川裕一,青木胜,卓圣鹏 著) 零基础学电子与Arduino:给编程新手的开发板入门指南

零基础学电子与Arduino:给编程新手的开发板入门指南

京公网安备 11010802033920号

京公网安备 11010802033920号