摘要:给出了以两片高性能TMS320C6414作为核心处理器,并辅以FPGA来实现系统逻辑时序控制,从而组成双DSP柔性机载实时图像处理系统的设计方案。同时对系统的硬件资源选择及工作流程进行了讨论。

关键词:DSP;并行处理;FPGA;柔性;超高速

1 引言

利用可见光成像与红外成像传感器实现实时目标成像跟踪是精确制导武器及机载成像光电系统研究的核心技术。伴随着实战环境日益复杂以及伪装、隐身等目标特性控制技术的飞速发展,机载实时图像跟踪系统的应用也日益广泛与深入。当跟踪目标并非一般地面慢速目标,而是其它快速运动目标如:低空导弹、无人驾驶飞机等时,系统将要求现有机载实时图像跟踪系统具有更高的技术性能。基于此,为了进一步提高现有机载光电跟踪系统在实战环境中,针对复杂场景下快速运动目标实施实时跟踪的鲁棒性与稳定性,笔者提出以双DSP和FP-GA为核心来构建主从式超高速并行处理体系的设计思想,并研究开发了基于双DSP的新型柔性机载实时图像跟踪系统。一方面,采用双DSP体系结构实现系统任务的并行划分使本系统具备极高的运算处理速度;另一方面,现场可编程逻辑器件FPGA的引入使系统的灵活性也得到极大的提高。而将两者结合可使本系统充分体现新一代机载实时图像跟踪系统更快速、更精确、更灵活的特点。

图1

2 TMS320C6414的结构特点

美国德州仪器公司(TI)推出的新一代数字信号处理器TMS320C6414(以下简称C6414)的主频为400MHz~700MHz,其数据处理能力为3200MIPS~5760MIPS。该器件的结构框图如图1所示。其主要特点如下:

(1)DSP内核采用超长指令字(VLIW)体系结构,有8个功能单元、64个32bit通用寄存器,一个时钟周期可同时执行8条指令,运算能力可以达到5760MIPS;

(2)为了使数据能满足超高速DSP内核的需求,C6414采用了两级超高速缓冲存储器,即16k Byte的一级数据Cache、16k Byte的一级程序Cache和1024k Byte的数据和程序统一内存。

(3)增加了直接处理打包数据指令,可建立无缝的数据流,以提高指令集的效率;

(4)每个功能单元在硬件上都增加了附加功能,从而增强了指令集的正交性。

3 系统硬件设计

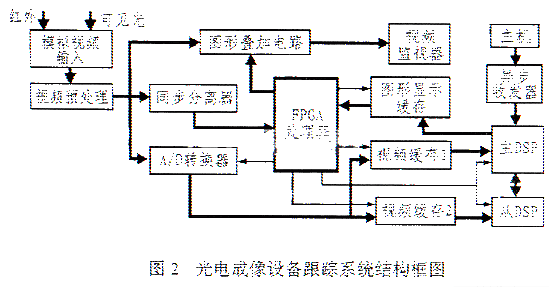

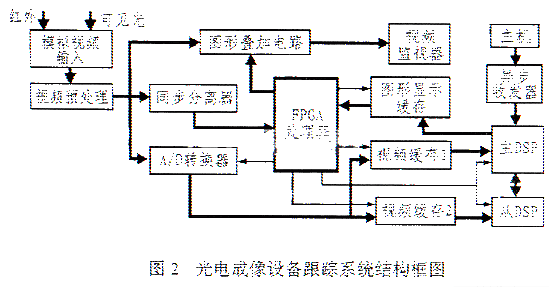

本光电成像跟踪系统硬件平台由六部分组成:图像采集与预处理模块、同步分离模块、FPGA逻辑控制模块、双DSP+双口RAM 图像处理模块、异步通信模块和图形显示模块。其系统原理框图如2所示。从图2可以知道:红外探测器及可见光摄像仪输出的模拟视频信号经多路信号选择芯片导入之后,经箝位、放大、滤波以及去同步头等预处理后,一路经A/D转换器将模拟视频转换为8bit数字信号并导入片外视频缓存1、2,而后等待FPGA时序控制DSP外部中断,以便将全部缓存数据搬移到DSP片内的2级缓存,再通过系统任务划分实现数据重组,然后分别在主从DSP进行同步并行数据处理,并将中间结果由主DSP综合,最后在完成后续运算后给出最终匹配结果。与此同时,主DSP则通过写图形显示缓存将目标匹配位置信息传递到外界;另一路模拟信号先导入同步分离器,然后提取行场同步信号送交FPGA作为时基,以产生系统各级时序控制信号;第三路模拟信号送给图形叠加电路作为输入叠加信号之一,当场正程来到时,FPGA中断控制并读出图形存储器数据,同时在FPGA片内实现读入数据的并/串转换后移位输出至图形叠加电路,此时两路信号将会合送入视频监视器,从而完成视频图像上图形的显示。整个系统工作期间,每隔80ms主DSP还通过异步收发器与外部上位机进行串行通信,以便系统能够实时接收外部命令与目标参数进而调整跟踪系统的工作状态。

3.1 图像采集与预处理模块

本系统中的多路选择器件选用CD4052芯片。它能根据不同的工作场合来切换红外/可见光视频输入;视频预处理电路采用AD817进行视频信号的放大,以得到更清晰的信号来进行视频处理;A/D芯片选用AD公司的AD9225,输出的8bit数字视频信号送入74LS245进行数据锁存。

3 系统硬件设计

本光电成像跟踪系统硬件平台由六部分组成:图像采集与预处理模块、同步分离模块、FPGA逻辑控制模块、双DSP+双口RAM 图像处理模块、异步通信模块和图形显示模块。其系统原理框图如2所示。从图2可以知道:红外探测器及可见光摄像仪输出的模拟视频信号经多路信号选择芯片导入之后,经箝位、放大、滤波以及去同步头等预处理后,一路经A/D转换器将模拟视频转换为8bit数字信号并导入片外视频缓存1、2,而后等待FPGA时序控制DSP外部中断,以便将全部缓存数据搬移到DSP片内的2级缓存,再通过系统任务划分实现数据重组,然后分别在主从DSP进行同步并行数据处理,并将中间结果由主DSP综合,最后在完成后续运算后给出最终匹配结果。与此同时,主DSP则通过写图形显示缓存将目标匹配位置信息传递到外界;另一路模拟信号先导入同步分离器,然后提取行场同步信号送交FPGA作为时基,以产生系统各级时序控制信号;第三路模拟信号送给图形叠加电路作为输入叠加信号之一,当场正程来到时,FPGA中断控制并读出图形存储器数据,同时在FPGA片内实现读入数据的并/串转换后移位输出至图形叠加电路,此时两路信号将会合送入视频监视器,从而完成视频图像上图形的显示。整个系统工作期间,每隔80ms主DSP还通过异步收发器与外部上位机进行串行通信,以便系统能够实时接收外部命令与目标参数进而调整跟踪系统的工作状态。

3.1 图像采集与预处理模块

本系统中的多路选择器件选用CD4052芯片。它能根据不同的工作场合来切换红外/可见光视频输入;视频预处理电路采用AD817进行视频信号的放大,以得到更清晰的信号来进行视频处理;A/D芯片选用AD公司的AD9225,输出的8bit数字视频信号送入74LS245进行数据锁存。

3.2 同步分离模块

系统采用一款专门的视频同步分离器LM1881来从标准的负同步NTSC(PAL或SECAM)视频信号中分离出有效的行/场同步信号,并将其送入FPGA以产生系统的各级逻辑控制输出。

3.3 FPGA逻辑控制模块

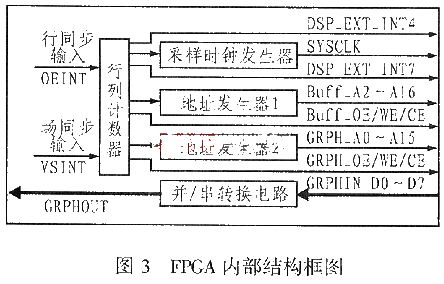

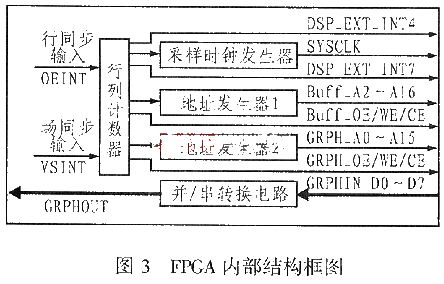

由于系统中各个芯片的功能相对独立,要协调这些芯片的运作就需要一片起控制逻辑作用的可编程芯片,为此,笔者选用了ALTERAL公司的EPF10K30A,该芯片有246个用户I/O口、30000个典型门、216个逻辑阵列块、1728个逻辑单元不仅能满足系统的控制要求,而且也可以为将来系统的功能扩展提供控制逻辑。在这个光电跟踪系统中,FPGA主要用来完成如下几方面的工作:

(1)生成A/D采样控制时钟,实现模拟视频的正确采样;

(2)提供字符图形存储器地址及片选/读控制信号,并在场正程到来时,控制图形数据的读出;

(3)提供视频数据缓存器地址及片选/写控制信号,控制视频数据的连续写入;

(4)产生外部中断4至双DSP,当数据写满视频图像高速缓存预定空间时,控制主从DSP以将数据块快速搬移至片内2级缓存;

(5)产生外部中断7至主DSP,并在每个场逆程时刻来到时,控制主DSP擦、写字符图形存储器数据;

(6)产生一并/串转换电路,以将并行读入的字符图形数据串行移位输出至图形叠加电路,从而实现“+”、“□”图形在视频图像上的叠加。

3.2 同步分离模块

系统采用一款专门的视频同步分离器LM1881来从标准的负同步NTSC(PAL或SECAM)视频信号中分离出有效的行/场同步信号,并将其送入FPGA以产生系统的各级逻辑控制输出。

3.3 FPGA逻辑控制模块

由于系统中各个芯片的功能相对独立,要协调这些芯片的运作就需要一片起控制逻辑作用的可编程芯片,为此,笔者选用了ALTERAL公司的EPF10K30A,该芯片有246个用户I/O口、30000个典型门、216个逻辑阵列块、1728个逻辑单元不仅能满足系统的控制要求,而且也可以为将来系统的功能扩展提供控制逻辑。在这个光电跟踪系统中,FPGA主要用来完成如下几方面的工作:

(1)生成A/D采样控制时钟,实现模拟视频的正确采样;

(2)提供字符图形存储器地址及片选/读控制信号,并在场正程到来时,控制图形数据的读出;

(3)提供视频数据缓存器地址及片选/写控制信号,控制视频数据的连续写入;

(4)产生外部中断4至双DSP,当数据写满视频图像高速缓存预定空间时,控制主从DSP以将数据块快速搬移至片内2级缓存;

(5)产生外部中断7至主DSP,并在每个场逆程时刻来到时,控制主DSP擦、写字符图形存储器数据;

(6)产生一并/串转换电路,以将并行读入的字符图形数据串行移位输出至图形叠加电路,从而实现“+”、“□”图形在视频图像上的叠加。

其FPGA内部结构框图如图3所示。

3.4 双DSP+双口RAM 图像处理模块

高速并行数字信号处理电路以双DSP为并行运算处理核心单元,并辅以双口RAM来实现视频图像的高速缓存,从而完成大运算量的高速实时目标跟踪处理任务。该并行处理系统的组成与功能分述如下:

a. 视频图像高速缓存子模块

为了实现图像的实时采集与高速处理,本系统用两片双口RAM组成相互独立的视频缓存,分别对应主/从DSP处理器。设计时选用IDT公司的3.3V 异步双口PRAM IDT70V657,同时与DSP接口采用ASRAM方式。由于EMIF的ASRAM接口支持32Bit的数据接口,因此,利用IDT70V657构成不完全地址结构来存取数据能够更好地实现8Bit锁存数据与C6414的接口,而无须对DPRAM进行宽度扩展。同时亦可减少DSP读取外部数据的时间开销。

IDT70V657的大小是32K%26;#215;36Bit系统采用将两个DPRAM各划分为前后两个半场的方式来实现存取数据时的乒乓切换。即在系统工作的任一时刻,当对DPRAM前半场写入数据时,使DPRAM后半场向DSP读出数据。当前半场写满视频数据时,由FPGA给DSP发出中断信号,以通知DSP读出DPRAM前半场所写入数据,同时,将A/D转换器的数据写入DPRAM后半场缓冲空间,如此反复进行来实现数据的读出与写入同步操作。

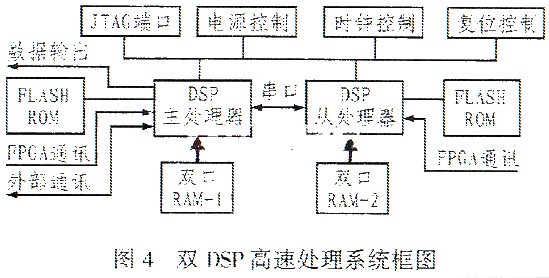

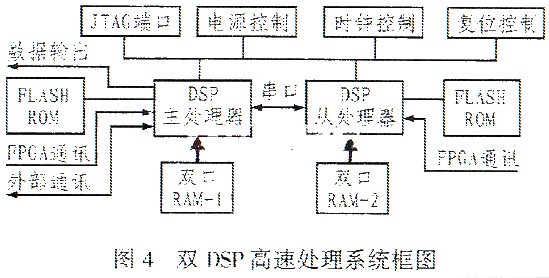

b. 双DSP高速信号处理系统

TMS320C6414-600型DSP的主频高达600MHz,在超高速实时图像处理领域有着非常出色的性能。本系统的双DSP高速实时信号处理系统就以2片C6414-600 DSP芯片为核心组成邻域图像并行处理机,并通过系统任务的划分与分解实现同步并行运算处理。其系统框图如图4所示。

在本系统中,主DSP完成的主要功能如下:

(1) 实现外部缓存数据到片内的搬移,为DSP高速批处理开辟片内二级缓存;

(2) 实现与外部上位机的即时通讯,接收外部命令与目标参数;

(3) 实现与从DSP的即时通信,下传命令字与目标参数以及获取中间结果;

(4) 运行系统跟踪算法,承担系统核心运算任务的一半;

(5) 与FPGA建立即时通信,实现系统程序模块的调度与协调;

从DSP完成的主要功能是:

(1) 实现外部缓存数据到片内的搬移,为DSP高速批处理开辟片内二级缓存;

(2)运行系统跟踪算法,承担系统核心运算任务的一半;

(3)实现与主DSP的即时通信,上传匹配运算中间结果;

(4)与FPGA建立即时通信,实现系统程序模块的调度与协调。

双DSP处理系统的柔性特色体现在:可依据实时环境需要加载不同的跟踪算法来实现目标跟踪。算法运行之初,两片C6414-600都在FPGA的控制下,通过EMIFA口以EDMA方式,分若干次,依系统跟踪算法而定将外部视频缓存中的数据(一场图像)依次读入DSP的L2片内缓存中;算法运行之后,主从DSP则通过McBSP直接互接来实现双DSP间的高速同步通信以便交换数据处理结果。

系统设计中,Flash ROM选用AMD公司的AM29LV800(1M%26;#215;8Bit)来把FLASH映射到DSP统一编址地址空间EMIFB口的CE1空间。当系统上电复位后,该地址空间为首先引导区域,这样即可将应用程序代码加载到片内高速执行,从而实现系统的脱机运行。

3.5 异步通信模块

本系统与外部上位机的异步通信主要通过主DSP的McBSP。C6000的McBSP是一个功能非常强大的标准串口,支持全双工串行通信,它的双缓冲数据寄存器允许连续的数据流,可与多达128个通道进行收发通信。通过对McBSP的SPCR、RCR、XCR、SRGR、PCR寄存器的配置可实现系统通信时收发数据的帧同步和时钟同步。

由于外部上位机的通讯机制是RS422标准,而DSP与外部通信只提供RS232接口,故应采用一片MAX3074芯片来实现RS422到RS232的转换。

其FPGA内部结构框图如图3所示。

3.4 双DSP+双口RAM 图像处理模块

高速并行数字信号处理电路以双DSP为并行运算处理核心单元,并辅以双口RAM来实现视频图像的高速缓存,从而完成大运算量的高速实时目标跟踪处理任务。该并行处理系统的组成与功能分述如下:

a. 视频图像高速缓存子模块

为了实现图像的实时采集与高速处理,本系统用两片双口RAM组成相互独立的视频缓存,分别对应主/从DSP处理器。设计时选用IDT公司的3.3V 异步双口PRAM IDT70V657,同时与DSP接口采用ASRAM方式。由于EMIF的ASRAM接口支持32Bit的数据接口,因此,利用IDT70V657构成不完全地址结构来存取数据能够更好地实现8Bit锁存数据与C6414的接口,而无须对DPRAM进行宽度扩展。同时亦可减少DSP读取外部数据的时间开销。

IDT70V657的大小是32K%26;#215;36Bit系统采用将两个DPRAM各划分为前后两个半场的方式来实现存取数据时的乒乓切换。即在系统工作的任一时刻,当对DPRAM前半场写入数据时,使DPRAM后半场向DSP读出数据。当前半场写满视频数据时,由FPGA给DSP发出中断信号,以通知DSP读出DPRAM前半场所写入数据,同时,将A/D转换器的数据写入DPRAM后半场缓冲空间,如此反复进行来实现数据的读出与写入同步操作。

b. 双DSP高速信号处理系统

TMS320C6414-600型DSP的主频高达600MHz,在超高速实时图像处理领域有着非常出色的性能。本系统的双DSP高速实时信号处理系统就以2片C6414-600 DSP芯片为核心组成邻域图像并行处理机,并通过系统任务的划分与分解实现同步并行运算处理。其系统框图如图4所示。

在本系统中,主DSP完成的主要功能如下:

(1) 实现外部缓存数据到片内的搬移,为DSP高速批处理开辟片内二级缓存;

(2) 实现与外部上位机的即时通讯,接收外部命令与目标参数;

(3) 实现与从DSP的即时通信,下传命令字与目标参数以及获取中间结果;

(4) 运行系统跟踪算法,承担系统核心运算任务的一半;

(5) 与FPGA建立即时通信,实现系统程序模块的调度与协调;

从DSP完成的主要功能是:

(1) 实现外部缓存数据到片内的搬移,为DSP高速批处理开辟片内二级缓存;

(2)运行系统跟踪算法,承担系统核心运算任务的一半;

(3)实现与主DSP的即时通信,上传匹配运算中间结果;

(4)与FPGA建立即时通信,实现系统程序模块的调度与协调。

双DSP处理系统的柔性特色体现在:可依据实时环境需要加载不同的跟踪算法来实现目标跟踪。算法运行之初,两片C6414-600都在FPGA的控制下,通过EMIFA口以EDMA方式,分若干次,依系统跟踪算法而定将外部视频缓存中的数据(一场图像)依次读入DSP的L2片内缓存中;算法运行之后,主从DSP则通过McBSP直接互接来实现双DSP间的高速同步通信以便交换数据处理结果。

系统设计中,Flash ROM选用AMD公司的AM29LV800(1M%26;#215;8Bit)来把FLASH映射到DSP统一编址地址空间EMIFB口的CE1空间。当系统上电复位后,该地址空间为首先引导区域,这样即可将应用程序代码加载到片内高速执行,从而实现系统的脱机运行。

3.5 异步通信模块

本系统与外部上位机的异步通信主要通过主DSP的McBSP。C6000的McBSP是一个功能非常强大的标准串口,支持全双工串行通信,它的双缓冲数据寄存器允许连续的数据流,可与多达128个通道进行收发通信。通过对McBSP的SPCR、RCR、XCR、SRGR、PCR寄存器的配置可实现系统通信时收发数据的帧同步和时钟同步。

由于外部上位机的通讯机制是RS422标准,而DSP与外部通信只提供RS232接口,故应采用一片MAX3074芯片来实现RS422到RS232的转换。

MAX3074是MAXIM公司生产的一款专门用于RS422/485至RS232的转接芯片,采用3.3V供电,这与C6000 DSP 外围供电电压一致,连接非常方便,不再需要多余的电压适配器。另一方面,由于McBSP为同步串口,为了实现McBSP与RS232的无缝连接,可通过软件加入发送扩展算法与接收压缩算法,从而实现DSP与上位机异步串口通信协议的握手。

3.6 图形显示模块

该模块由图形存储器、图形叠加电路和视频监视器组成。图形存储器选择IDT公司的70V08(64K%26;#215;8Bits)DPRAM来存储标识目标匹配位置的图形数据。图形叠加电路用于实现视频与图形的叠加,并最终由视频监视器显示叠加结果。

4 系统工作流程

本系统的软件工作模式包括复位和初始化模式、运行模式、系统维护模式,可由系统程序来控制三种模式的切换。

在复位和初始化模式下,系统启动后将由主从DSP同步实现程序搬移,把程序代码搬移到片内并运行系统程序,从而初始化主从DSP的运行环境并设置相关参数。

运行模式下,双DSP一方面独立响应并处理FPGA中断、运行核心跟踪算法并实现子系统内的进程调度;另一方面通过主从DSP串口间的互连响应中断以及主DSP串口与远程主机的通讯等功能来实现双DSP子系统间和双DSP系统与外部主机的进程调度。

系统维护模式下,主从DSP在进行系统自检后,可由远程主机通过RS422接口与主DSP进行通讯,以实现程序的更新下载和参数修改等功能。图5为系统软件工作流程框图。

5 结束语

笔者对该系统的实时性进行了仿真测试,结果分析表明:

(1)单DSP只能实现开窗搜索,高速场合下一旦目标逃逸搜索区,将导致目标丢失;而本系统能够实现基于整场搜索的大运算量高速处理,从而加大了被跟踪目标搜索区的动态范围,避免了目标丢失情况的发生,进一步提高了实时跟踪的可靠性。

(2)传统单DSP系统一般只能实现基于一帧的匹配性能,而本系统可实现基于逐场的跟踪匹配,进一步提高了跟踪系统的实时性。

(3)根据实际场合的需要,本系统可通过软件选择加载跟踪算法,从而极大的增强了系统的通用性和易维护性,体现出柔性处理系统的特色。

由此可见,双DSP柔性处理系统为复杂场景下快速移动目标的高速识别与跟踪提供了一个有效的实现方案,同时也为机载实时图像跟踪系统提供了新的高速处理平台。

MAX3074是MAXIM公司生产的一款专门用于RS422/485至RS232的转接芯片,采用3.3V供电,这与C6000 DSP 外围供电电压一致,连接非常方便,不再需要多余的电压适配器。另一方面,由于McBSP为同步串口,为了实现McBSP与RS232的无缝连接,可通过软件加入发送扩展算法与接收压缩算法,从而实现DSP与上位机异步串口通信协议的握手。

3.6 图形显示模块

该模块由图形存储器、图形叠加电路和视频监视器组成。图形存储器选择IDT公司的70V08(64K%26;#215;8Bits)DPRAM来存储标识目标匹配位置的图形数据。图形叠加电路用于实现视频与图形的叠加,并最终由视频监视器显示叠加结果。

4 系统工作流程

本系统的软件工作模式包括复位和初始化模式、运行模式、系统维护模式,可由系统程序来控制三种模式的切换。

在复位和初始化模式下,系统启动后将由主从DSP同步实现程序搬移,把程序代码搬移到片内并运行系统程序,从而初始化主从DSP的运行环境并设置相关参数。

运行模式下,双DSP一方面独立响应并处理FPGA中断、运行核心跟踪算法并实现子系统内的进程调度;另一方面通过主从DSP串口间的互连响应中断以及主DSP串口与远程主机的通讯等功能来实现双DSP子系统间和双DSP系统与外部主机的进程调度。

系统维护模式下,主从DSP在进行系统自检后,可由远程主机通过RS422接口与主DSP进行通讯,以实现程序的更新下载和参数修改等功能。图5为系统软件工作流程框图。

5 结束语

笔者对该系统的实时性进行了仿真测试,结果分析表明:

(1)单DSP只能实现开窗搜索,高速场合下一旦目标逃逸搜索区,将导致目标丢失;而本系统能够实现基于整场搜索的大运算量高速处理,从而加大了被跟踪目标搜索区的动态范围,避免了目标丢失情况的发生,进一步提高了实时跟踪的可靠性。

(2)传统单DSP系统一般只能实现基于一帧的匹配性能,而本系统可实现基于逐场的跟踪匹配,进一步提高了跟踪系统的实时性。

(3)根据实际场合的需要,本系统可通过软件选择加载跟踪算法,从而极大的增强了系统的通用性和易维护性,体现出柔性处理系统的特色。

由此可见,双DSP柔性处理系统为复杂场景下快速移动目标的高速识别与跟踪提供了一个有效的实现方案,同时也为机载实时图像跟踪系统提供了新的高速处理平台。

引用地址:基于高速双DSP的柔性机载实时图像跟踪系统研究

3 系统硬件设计

本光电成像跟踪系统硬件平台由六部分组成:图像采集与预处理模块、同步分离模块、FPGA逻辑控制模块、双DSP+双口RAM 图像处理模块、异步通信模块和图形显示模块。其系统原理框图如2所示。从图2可以知道:红外探测器及可见光摄像仪输出的模拟视频信号经多路信号选择芯片导入之后,经箝位、放大、滤波以及去同步头等预处理后,一路经A/D转换器将模拟视频转换为8bit数字信号并导入片外视频缓存1、2,而后等待FPGA时序控制DSP外部中断,以便将全部缓存数据搬移到DSP片内的2级缓存,再通过系统任务划分实现数据重组,然后分别在主从DSP进行同步并行数据处理,并将中间结果由主DSP综合,最后在完成后续运算后给出最终匹配结果。与此同时,主DSP则通过写图形显示缓存将目标匹配位置信息传递到外界;另一路模拟信号先导入同步分离器,然后提取行场同步信号送交FPGA作为时基,以产生系统各级时序控制信号;第三路模拟信号送给图形叠加电路作为输入叠加信号之一,当场正程来到时,FPGA中断控制并读出图形存储器数据,同时在FPGA片内实现读入数据的并/串转换后移位输出至图形叠加电路,此时两路信号将会合送入视频监视器,从而完成视频图像上图形的显示。整个系统工作期间,每隔80ms主DSP还通过异步收发器与外部上位机进行串行通信,以便系统能够实时接收外部命令与目标参数进而调整跟踪系统的工作状态。

3.1 图像采集与预处理模块

本系统中的多路选择器件选用CD4052芯片。它能根据不同的工作场合来切换红外/可见光视频输入;视频预处理电路采用AD817进行视频信号的放大,以得到更清晰的信号来进行视频处理;A/D芯片选用AD公司的AD9225,输出的8bit数字视频信号送入74LS245进行数据锁存。

3 系统硬件设计

本光电成像跟踪系统硬件平台由六部分组成:图像采集与预处理模块、同步分离模块、FPGA逻辑控制模块、双DSP+双口RAM 图像处理模块、异步通信模块和图形显示模块。其系统原理框图如2所示。从图2可以知道:红外探测器及可见光摄像仪输出的模拟视频信号经多路信号选择芯片导入之后,经箝位、放大、滤波以及去同步头等预处理后,一路经A/D转换器将模拟视频转换为8bit数字信号并导入片外视频缓存1、2,而后等待FPGA时序控制DSP外部中断,以便将全部缓存数据搬移到DSP片内的2级缓存,再通过系统任务划分实现数据重组,然后分别在主从DSP进行同步并行数据处理,并将中间结果由主DSP综合,最后在完成后续运算后给出最终匹配结果。与此同时,主DSP则通过写图形显示缓存将目标匹配位置信息传递到外界;另一路模拟信号先导入同步分离器,然后提取行场同步信号送交FPGA作为时基,以产生系统各级时序控制信号;第三路模拟信号送给图形叠加电路作为输入叠加信号之一,当场正程来到时,FPGA中断控制并读出图形存储器数据,同时在FPGA片内实现读入数据的并/串转换后移位输出至图形叠加电路,此时两路信号将会合送入视频监视器,从而完成视频图像上图形的显示。整个系统工作期间,每隔80ms主DSP还通过异步收发器与外部上位机进行串行通信,以便系统能够实时接收外部命令与目标参数进而调整跟踪系统的工作状态。

3.1 图像采集与预处理模块

本系统中的多路选择器件选用CD4052芯片。它能根据不同的工作场合来切换红外/可见光视频输入;视频预处理电路采用AD817进行视频信号的放大,以得到更清晰的信号来进行视频处理;A/D芯片选用AD公司的AD9225,输出的8bit数字视频信号送入74LS245进行数据锁存。

3.2 同步分离模块

系统采用一款专门的视频同步分离器LM1881来从标准的负同步NTSC(PAL或SECAM)视频信号中分离出有效的行/场同步信号,并将其送入FPGA以产生系统的各级逻辑控制输出。

3.3 FPGA逻辑控制模块

由于系统中各个芯片的功能相对独立,要协调这些芯片的运作就需要一片起控制逻辑作用的可编程芯片,为此,笔者选用了ALTERAL公司的EPF10K30A,该芯片有246个用户I/O口、30000个典型门、216个逻辑阵列块、1728个逻辑单元不仅能满足系统的控制要求,而且也可以为将来系统的功能扩展提供控制逻辑。在这个光电跟踪系统中,FPGA主要用来完成如下几方面的工作:

(1)生成A/D采样控制时钟,实现模拟视频的正确采样;

(2)提供字符图形存储器地址及片选/读控制信号,并在场正程到来时,控制图形数据的读出;

(3)提供视频数据缓存器地址及片选/写控制信号,控制视频数据的连续写入;

(4)产生外部中断4至双DSP,当数据写满视频图像高速缓存预定空间时,控制主从DSP以将数据块快速搬移至片内2级缓存;

(5)产生外部中断7至主DSP,并在每个场逆程时刻来到时,控制主DSP擦、写字符图形存储器数据;

(6)产生一并/串转换电路,以将并行读入的字符图形数据串行移位输出至图形叠加电路,从而实现“+”、“□”图形在视频图像上的叠加。

3.2 同步分离模块

系统采用一款专门的视频同步分离器LM1881来从标准的负同步NTSC(PAL或SECAM)视频信号中分离出有效的行/场同步信号,并将其送入FPGA以产生系统的各级逻辑控制输出。

3.3 FPGA逻辑控制模块

由于系统中各个芯片的功能相对独立,要协调这些芯片的运作就需要一片起控制逻辑作用的可编程芯片,为此,笔者选用了ALTERAL公司的EPF10K30A,该芯片有246个用户I/O口、30000个典型门、216个逻辑阵列块、1728个逻辑单元不仅能满足系统的控制要求,而且也可以为将来系统的功能扩展提供控制逻辑。在这个光电跟踪系统中,FPGA主要用来完成如下几方面的工作:

(1)生成A/D采样控制时钟,实现模拟视频的正确采样;

(2)提供字符图形存储器地址及片选/读控制信号,并在场正程到来时,控制图形数据的读出;

(3)提供视频数据缓存器地址及片选/写控制信号,控制视频数据的连续写入;

(4)产生外部中断4至双DSP,当数据写满视频图像高速缓存预定空间时,控制主从DSP以将数据块快速搬移至片内2级缓存;

(5)产生外部中断7至主DSP,并在每个场逆程时刻来到时,控制主DSP擦、写字符图形存储器数据;

(6)产生一并/串转换电路,以将并行读入的字符图形数据串行移位输出至图形叠加电路,从而实现“+”、“□”图形在视频图像上的叠加。

其FPGA内部结构框图如图3所示。

3.4 双DSP+双口RAM 图像处理模块

高速并行数字信号处理电路以双DSP为并行运算处理核心单元,并辅以双口RAM来实现视频图像的高速缓存,从而完成大运算量的高速实时目标跟踪处理任务。该并行处理系统的组成与功能分述如下:

a. 视频图像高速缓存子模块

为了实现图像的实时采集与高速处理,本系统用两片双口RAM组成相互独立的视频缓存,分别对应主/从DSP处理器。设计时选用IDT公司的3.3V 异步双口PRAM IDT70V657,同时与DSP接口采用ASRAM方式。由于EMIF的ASRAM接口支持32Bit的数据接口,因此,利用IDT70V657构成不完全地址结构来存取数据能够更好地实现8Bit锁存数据与C6414的接口,而无须对DPRAM进行宽度扩展。同时亦可减少DSP读取外部数据的时间开销。

IDT70V657的大小是32K%26;#215;36Bit系统采用将两个DPRAM各划分为前后两个半场的方式来实现存取数据时的乒乓切换。即在系统工作的任一时刻,当对DPRAM前半场写入数据时,使DPRAM后半场向DSP读出数据。当前半场写满视频数据时,由FPGA给DSP发出中断信号,以通知DSP读出DPRAM前半场所写入数据,同时,将A/D转换器的数据写入DPRAM后半场缓冲空间,如此反复进行来实现数据的读出与写入同步操作。

b. 双DSP高速信号处理系统

TMS320C6414-600型DSP的主频高达600MHz,在超高速实时图像处理领域有着非常出色的性能。本系统的双DSP高速实时信号处理系统就以2片C6414-600 DSP芯片为核心组成邻域图像并行处理机,并通过系统任务的划分与分解实现同步并行运算处理。其系统框图如图4所示。

在本系统中,主DSP完成的主要功能如下:

(1) 实现外部缓存数据到片内的搬移,为DSP高速批处理开辟片内二级缓存;

(2) 实现与外部上位机的即时通讯,接收外部命令与目标参数;

(3) 实现与从DSP的即时通信,下传命令字与目标参数以及获取中间结果;

(4) 运行系统跟踪算法,承担系统核心运算任务的一半;

(5) 与FPGA建立即时通信,实现系统程序模块的调度与协调;

从DSP完成的主要功能是:

(1) 实现外部缓存数据到片内的搬移,为DSP高速批处理开辟片内二级缓存;

(2)运行系统跟踪算法,承担系统核心运算任务的一半;

(3)实现与主DSP的即时通信,上传匹配运算中间结果;

(4)与FPGA建立即时通信,实现系统程序模块的调度与协调。

双DSP处理系统的柔性特色体现在:可依据实时环境需要加载不同的跟踪算法来实现目标跟踪。算法运行之初,两片C6414-600都在FPGA的控制下,通过EMIFA口以EDMA方式,分若干次,依系统跟踪算法而定将外部视频缓存中的数据(一场图像)依次读入DSP的L2片内缓存中;算法运行之后,主从DSP则通过McBSP直接互接来实现双DSP间的高速同步通信以便交换数据处理结果。

系统设计中,Flash ROM选用AMD公司的AM29LV800(1M%26;#215;8Bit)来把FLASH映射到DSP统一编址地址空间EMIFB口的CE1空间。当系统上电复位后,该地址空间为首先引导区域,这样即可将应用程序代码加载到片内高速执行,从而实现系统的脱机运行。

3.5 异步通信模块

本系统与外部上位机的异步通信主要通过主DSP的McBSP。C6000的McBSP是一个功能非常强大的标准串口,支持全双工串行通信,它的双缓冲数据寄存器允许连续的数据流,可与多达128个通道进行收发通信。通过对McBSP的SPCR、RCR、XCR、SRGR、PCR寄存器的配置可实现系统通信时收发数据的帧同步和时钟同步。

由于外部上位机的通讯机制是RS422标准,而DSP与外部通信只提供RS232接口,故应采用一片MAX3074芯片来实现RS422到RS232的转换。

其FPGA内部结构框图如图3所示。

3.4 双DSP+双口RAM 图像处理模块

高速并行数字信号处理电路以双DSP为并行运算处理核心单元,并辅以双口RAM来实现视频图像的高速缓存,从而完成大运算量的高速实时目标跟踪处理任务。该并行处理系统的组成与功能分述如下:

a. 视频图像高速缓存子模块

为了实现图像的实时采集与高速处理,本系统用两片双口RAM组成相互独立的视频缓存,分别对应主/从DSP处理器。设计时选用IDT公司的3.3V 异步双口PRAM IDT70V657,同时与DSP接口采用ASRAM方式。由于EMIF的ASRAM接口支持32Bit的数据接口,因此,利用IDT70V657构成不完全地址结构来存取数据能够更好地实现8Bit锁存数据与C6414的接口,而无须对DPRAM进行宽度扩展。同时亦可减少DSP读取外部数据的时间开销。

IDT70V657的大小是32K%26;#215;36Bit系统采用将两个DPRAM各划分为前后两个半场的方式来实现存取数据时的乒乓切换。即在系统工作的任一时刻,当对DPRAM前半场写入数据时,使DPRAM后半场向DSP读出数据。当前半场写满视频数据时,由FPGA给DSP发出中断信号,以通知DSP读出DPRAM前半场所写入数据,同时,将A/D转换器的数据写入DPRAM后半场缓冲空间,如此反复进行来实现数据的读出与写入同步操作。

b. 双DSP高速信号处理系统

TMS320C6414-600型DSP的主频高达600MHz,在超高速实时图像处理领域有着非常出色的性能。本系统的双DSP高速实时信号处理系统就以2片C6414-600 DSP芯片为核心组成邻域图像并行处理机,并通过系统任务的划分与分解实现同步并行运算处理。其系统框图如图4所示。

在本系统中,主DSP完成的主要功能如下:

(1) 实现外部缓存数据到片内的搬移,为DSP高速批处理开辟片内二级缓存;

(2) 实现与外部上位机的即时通讯,接收外部命令与目标参数;

(3) 实现与从DSP的即时通信,下传命令字与目标参数以及获取中间结果;

(4) 运行系统跟踪算法,承担系统核心运算任务的一半;

(5) 与FPGA建立即时通信,实现系统程序模块的调度与协调;

从DSP完成的主要功能是:

(1) 实现外部缓存数据到片内的搬移,为DSP高速批处理开辟片内二级缓存;

(2)运行系统跟踪算法,承担系统核心运算任务的一半;

(3)实现与主DSP的即时通信,上传匹配运算中间结果;

(4)与FPGA建立即时通信,实现系统程序模块的调度与协调。

双DSP处理系统的柔性特色体现在:可依据实时环境需要加载不同的跟踪算法来实现目标跟踪。算法运行之初,两片C6414-600都在FPGA的控制下,通过EMIFA口以EDMA方式,分若干次,依系统跟踪算法而定将外部视频缓存中的数据(一场图像)依次读入DSP的L2片内缓存中;算法运行之后,主从DSP则通过McBSP直接互接来实现双DSP间的高速同步通信以便交换数据处理结果。

系统设计中,Flash ROM选用AMD公司的AM29LV800(1M%26;#215;8Bit)来把FLASH映射到DSP统一编址地址空间EMIFB口的CE1空间。当系统上电复位后,该地址空间为首先引导区域,这样即可将应用程序代码加载到片内高速执行,从而实现系统的脱机运行。

3.5 异步通信模块

本系统与外部上位机的异步通信主要通过主DSP的McBSP。C6000的McBSP是一个功能非常强大的标准串口,支持全双工串行通信,它的双缓冲数据寄存器允许连续的数据流,可与多达128个通道进行收发通信。通过对McBSP的SPCR、RCR、XCR、SRGR、PCR寄存器的配置可实现系统通信时收发数据的帧同步和时钟同步。

由于外部上位机的通讯机制是RS422标准,而DSP与外部通信只提供RS232接口,故应采用一片MAX3074芯片来实现RS422到RS232的转换。

MAX3074是MAXIM公司生产的一款专门用于RS422/485至RS232的转接芯片,采用3.3V供电,这与C6000 DSP 外围供电电压一致,连接非常方便,不再需要多余的电压适配器。另一方面,由于McBSP为同步串口,为了实现McBSP与RS232的无缝连接,可通过软件加入发送扩展算法与接收压缩算法,从而实现DSP与上位机异步串口通信协议的握手。

3.6 图形显示模块

该模块由图形存储器、图形叠加电路和视频监视器组成。图形存储器选择IDT公司的70V08(64K%26;#215;8Bits)DPRAM来存储标识目标匹配位置的图形数据。图形叠加电路用于实现视频与图形的叠加,并最终由视频监视器显示叠加结果。

4 系统工作流程

本系统的软件工作模式包括复位和初始化模式、运行模式、系统维护模式,可由系统程序来控制三种模式的切换。

在复位和初始化模式下,系统启动后将由主从DSP同步实现程序搬移,把程序代码搬移到片内并运行系统程序,从而初始化主从DSP的运行环境并设置相关参数。

运行模式下,双DSP一方面独立响应并处理FPGA中断、运行核心跟踪算法并实现子系统内的进程调度;另一方面通过主从DSP串口间的互连响应中断以及主DSP串口与远程主机的通讯等功能来实现双DSP子系统间和双DSP系统与外部主机的进程调度。

系统维护模式下,主从DSP在进行系统自检后,可由远程主机通过RS422接口与主DSP进行通讯,以实现程序的更新下载和参数修改等功能。图5为系统软件工作流程框图。

5 结束语

笔者对该系统的实时性进行了仿真测试,结果分析表明:

(1)单DSP只能实现开窗搜索,高速场合下一旦目标逃逸搜索区,将导致目标丢失;而本系统能够实现基于整场搜索的大运算量高速处理,从而加大了被跟踪目标搜索区的动态范围,避免了目标丢失情况的发生,进一步提高了实时跟踪的可靠性。

(2)传统单DSP系统一般只能实现基于一帧的匹配性能,而本系统可实现基于逐场的跟踪匹配,进一步提高了跟踪系统的实时性。

(3)根据实际场合的需要,本系统可通过软件选择加载跟踪算法,从而极大的增强了系统的通用性和易维护性,体现出柔性处理系统的特色。

由此可见,双DSP柔性处理系统为复杂场景下快速移动目标的高速识别与跟踪提供了一个有效的实现方案,同时也为机载实时图像跟踪系统提供了新的高速处理平台。

MAX3074是MAXIM公司生产的一款专门用于RS422/485至RS232的转接芯片,采用3.3V供电,这与C6000 DSP 外围供电电压一致,连接非常方便,不再需要多余的电压适配器。另一方面,由于McBSP为同步串口,为了实现McBSP与RS232的无缝连接,可通过软件加入发送扩展算法与接收压缩算法,从而实现DSP与上位机异步串口通信协议的握手。

3.6 图形显示模块

该模块由图形存储器、图形叠加电路和视频监视器组成。图形存储器选择IDT公司的70V08(64K%26;#215;8Bits)DPRAM来存储标识目标匹配位置的图形数据。图形叠加电路用于实现视频与图形的叠加,并最终由视频监视器显示叠加结果。

4 系统工作流程

本系统的软件工作模式包括复位和初始化模式、运行模式、系统维护模式,可由系统程序来控制三种模式的切换。

在复位和初始化模式下,系统启动后将由主从DSP同步实现程序搬移,把程序代码搬移到片内并运行系统程序,从而初始化主从DSP的运行环境并设置相关参数。

运行模式下,双DSP一方面独立响应并处理FPGA中断、运行核心跟踪算法并实现子系统内的进程调度;另一方面通过主从DSP串口间的互连响应中断以及主DSP串口与远程主机的通讯等功能来实现双DSP子系统间和双DSP系统与外部主机的进程调度。

系统维护模式下,主从DSP在进行系统自检后,可由远程主机通过RS422接口与主DSP进行通讯,以实现程序的更新下载和参数修改等功能。图5为系统软件工作流程框图。

5 结束语

笔者对该系统的实时性进行了仿真测试,结果分析表明:

(1)单DSP只能实现开窗搜索,高速场合下一旦目标逃逸搜索区,将导致目标丢失;而本系统能够实现基于整场搜索的大运算量高速处理,从而加大了被跟踪目标搜索区的动态范围,避免了目标丢失情况的发生,进一步提高了实时跟踪的可靠性。

(2)传统单DSP系统一般只能实现基于一帧的匹配性能,而本系统可实现基于逐场的跟踪匹配,进一步提高了跟踪系统的实时性。

(3)根据实际场合的需要,本系统可通过软件选择加载跟踪算法,从而极大的增强了系统的通用性和易维护性,体现出柔性处理系统的特色。

由此可见,双DSP柔性处理系统为复杂场景下快速移动目标的高速识别与跟踪提供了一个有效的实现方案,同时也为机载实时图像跟踪系统提供了新的高速处理平台。

上一篇:基于DSP运动控制器的丝杠副动态误差测控系统

下一篇:Blackfin533的DMA技术及其在图像处理中的应用

- 热门资源推荐

- 热门放大器推荐

小广播

热门活动

换一批

更多

最新嵌入式文章

更多精选电路图

更多热门文章

更多每日新闻

- 芯启源(上海)将持续发力,“做深做精”EDA及IP产品

- 本田严厉警告日产:若与鸿海合作,那么本田与日产的合作将终止

- Microchip推出新款交钥匙电容式触摸控制器产品 MTCH2120

- Matter对AIoT的意义:连接AIoT设备开发人员指南

- 我国科学家建立生成式模型为医学AI训练提供技术支持

- Diodes 推出符合车用标准的电流分流监测器,通过高精度电压感测快速检测系统故障

- Power Integrations面向800V汽车应用推出新型宽爬电距离开关IC

- 打破台积电垄断!联电夺下高通先进封装订单

- Ampere 年度展望:2025年重塑IT格局的四大关键趋势

- 存储巨头铠侠正式挂牌上市:首日股价上涨超10%

更多往期活动

厂商技术中心

Verilog HDL数字集成电路设计原理与应用

Verilog HDL数字集成电路设计原理与应用 TLE2161MD

TLE2161MD

京公网安备 11010802033920号

京公网安备 11010802033920号