摘要:对符号定时恢复环路、载波恢复环路算法进行了分析和仿真,提出了宽带多速率解调器的总体结构和同步的硬件实现方案.根据QPSK信号的特点,对载波同步算法进行了简化.对实现的解调器样机进行了性能测试和分析.测试结果表明,该解调器可以工作在2-45 MS/s符号速率下,当符号速率小于10 MS/s时,中频环路的误码性能指标与理论值之差小于1 dB;当符号速率大于10MS/s时,中频环路的误码性能指标与理论值之差小于1.6dB.

关键词:宽带多速率解调器;定时同步;载波同步

解调器作为数字接收机中的关键部分,对通信系统的整体性能有着重要的影响.随着多媒体业务的发展,对无线通信宽带传输的需求越来越大,而无线信道环境是时变的,为了适应在不同的信道条件下传输不同的业务,作者研究了宽带多速率QPSK解调器中的关键算法,给出了基于SPW的性能仿真结果.在此基础上,研究了宽带多速率解调器的FPGA实现方案,并对研制的样机进行了性能测试.

1 宽带多速率解调器算法设计

1.1符号定时恢复环路

传统的符号定时恢复环路采用模拟器件(如VCO)控制A/D采样时钟实现同步采样.在宽带多速率条件下,改变采样时钟将带来相位抖动,从而影响接收机的性能.因此,异步采样的符号定时恢复结构逐渐得到了广泛应用.图1为异步采样的符号定时恢复原理框图.

插值器的任务是根据几个连续输入的采样点x(mTs),计算出插值点y(kTi)的值,并且完成采样率转换.常用的插值器包括线性内插器、分段抛物线内插器和立方拉格朗日内插器.

在采样率相对较低的情况下,立方拉格朗日内插器在性能和复杂度上可以达到良好的折衷.

定时控制器用于产生插值器的基点,并且计算小数间隔μk,它可以由累减的NCO和小数间隔μk产生单元实现.

定时误差检测器采用Gardner算法.由于该算法每个符号只需2个采样点,并且符号定时误差的提取与载波恢复无关,因此已经被广泛应用于数字解调器的设计中.

1.2 载波恢复环路

图2为基于解旋转的载波恢复环路的原理框图.相位误差检测器采用基于最大后验概率的相位误差检测算法。其算法表达式为

式中I和Q为两支路信号的硬判决.该算法为判决反馈型,因此可以在较高信噪比下获得好的检测性能.

1.3 基于SPW的同步环路性能仿真

用SPW软件对系统进行建模.A/D采样率设为96 MHz,对于2和8MS/s符号速率的采样信号分别进行12倍和4倍的CIC抽取,对于32和45MS/s符号速率则旁路CIC滤波器.图3为用SPW仿真得到的2~45 MS/s符号速率QPSK信号的误比特率(PBER)与Eb/No关系曲线.仿真结果表明,在低速率条件下,采用上述算法,Eb/No的损失小于0.5 dB;在高速率条件下,Eb/No的损失为1.0dB.

2 宽带多速率解调器的实现

设计的宽带多速率解调器框图如图4所示,本振和A/D采样的时钟信号都不受反馈环路的控制,符号定时恢复和载波恢复由FPGA全数字实现.图中略去了自动增益控制(AGC)环路、锁定检测、数字时钟管理等模块,这些模块在设计中均已经实现.设计使用的芯片为xilinx公司生产的VirtexⅡXC2V1000-5 FPGA.

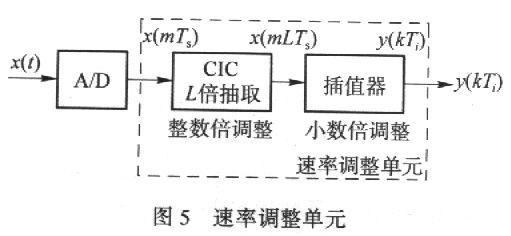

2.1 多速率调整单元的实现

由于要求设计的宽带多速率解调器需要在2~45 MS/s符号速率可变的QPSK信号下正常工作,因此模拟I-Q解调器后的模拟低通滤波器需要按照最大符号速率时所占用的30 Mtz带宽设计.对于较低符号速率,由于模拟部分无法滤除宽带噪声,需要在FPGA中设计数字低通滤波器.另一方面,由于采用了固定时钟异步采样的符号定时恢复结构,在低符号速率条件下,需要对采样数据进行抽取,减少数据处理量,从而降低FPGA芯片功耗.因此,设计中在A/D采样后进行了CIC抽取,滤除宽带噪声,并且调整采样率.图5为速率调整单元示意图.其中,CIC滤波器实现整数倍抽取,抽取倍数L与符号速率和采样速率之比有关,插值器实现小数倍抽取.这种CIC滤波器与插值器相结合的结构,使得只要对基带信号的采样率满足采样定理,设计的解调器在理论上都可以采用统一的结构实现,需要改变的仅仅是CIC抽取倍数以及定时控制器的参数.

2.2 符号定时恢复电路的实现

插值器是变系数的FIR滤波器,其系数可以由两种方法产生:一种是在线计算方法;另一种是将系数存储在ROM里,然后由量化的小数间隔μk进行查表.前者通常选择多项式插值器,因为这类插值器可以由Farrow结构实现.但是由于Farrow结构的延迟可能造成反馈环路不稳定,因此作者选择基于ROM的结构.图6为基于ROM的立方拉格朗日插值器的实现结构.

所需ROM的容量由小数间隔μk的精度和FIR系数的精度共同决定.SPW定点仿真表明,μk取5 bit已经可以满足应用要求.FIR系数取13 bit因此,需要的总ROM容量为1 664 bit,它可以方便地用VirtexⅡFPGA中嵌入的硬核BlockRAM实现.

定时控制器的结构见文献。

2.3 载波恢复电路的实现

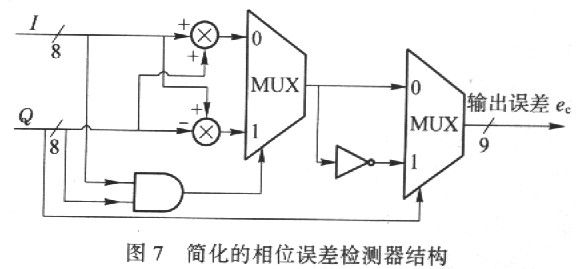

载波恢复电路可根据图2给出的结构实现.其中的相位误差检测器可作如下简化.

与图2中的结构相比,式(2)节省了两个乘法器,其结构如图7所示.

高速解调器的基带信号处理子模块均用Verilog硬件描述语言实现.表1为在Xilinx公司的VirtexⅡxC2V1000-5 FPGA芯片中实现上述模块的资源占用情况.

3 性能测试结果

对宽带多速率解调器进行了中频环路的误码率性能测试,测试平台如图8所示.

矢量信号发生器选用Agilent公司的E4438C,其最高符号速率可达50 MS/s;噪声发生器为Noise/Com公司的NC6110;信号功率和噪声功率通过Agilent公司的频谱分析仪8561E测量,然后将测得的SNR转换为相应的Eb/No.

图9为宽带多速率解调器工作时,利用xilinx公司的ChipSeope软件,通过JTAG口读出的数据其中,图9a为A/D采样后进入FPGA的基带信号星座图;图9b为解调器完成符号定时恢复和载波恢复后输出的信号星座图;图9c为小数间隔μk随时间的变化;图9d为环路滤波器输出的误差信号.由于采样速率与符号速率为整数倍关系,因此小数间隔μk具有周期性,在几个固定值之间变化.实际应用中,A/D的采样速率与符号速率可能是无理数倍关系,这时小数间隔μk的取值将不再具有周期性.

误码率测试结果如图10所示.测试结果表明,作者设计实现的宽带多速率解调器可对高达45 MS/s符号速率的QPSK信号进行解调.与理论值相比,在误比特率相同的条件下,在符号速率2~10 MS/s范围内,Eh/No相差小于1.0 dB,在45 MS/s时相差小于1.6 dB.

解调器在45MS/s时性能损失的原因在于A/D的采样率小于100 MHz,因此对于45 MS/s的QP-SK信号,每个符号的采样点数小于2.3,因此带来插值定时恢复结构性能的恶化,引起误码率上升提高A/D的采样速率或设计低采样率下性能更好的插值滤波器,将会进一步提高解调器在高符号速率下的性能.

上一篇:宽带多速率解调器的设计与实现

下一篇:基于DSP的SPWM变频电源数字控制

推荐阅读最新更新时间:2024-05-02 20:40

电力工程设计手册 23 变电站设计

电力工程设计手册 23 变电站设计 Verilog HDL数字集成电路设计原理与应用

Verilog HDL数字集成电路设计原理与应用

京公网安备 11010802033920号

京公网安备 11010802033920号