在科学研究、通信和一些自动控制中,经常需要精确定时的连续脉冲信号,用于产生测试信号或控制用的时序。脉冲延迟的基本方法可分为数字方法和模拟方法。数字方法采用计数器或存储器实现延迟控制,其缺点是无法满足高分辨率的要求;模拟方法采用专用的脉冲延迟器件实现延迟控制,其缺点是抗干扰效果不好,容易产生抖动和电压不稳等问题。于是我们提出构建数模结合的系统,实现连续脉冲信号的高分辨率延迟。

1 系统功能

本系统拟定对频率范围在1~50 kHz左右的TTL电平脉冲序列进行多路延迟处理。各路延迟时间分别由单片机动态设定,最大延迟时间为1ms,最大分辨率为O.15 nS级。

2 方案选择

用模拟方法进行延迟低位部分控制时,选用了DS1020延迟线芯片。只要在电路板上搭建多组以DS1020延迟线芯片为主的电路,就可以同时输出多路脉冲序列。此时最大延迟分辨率可以达到0.15 ns级。本方案中各路计数器模块和延迟线的延迟时间均可由MCU编程来动态调整,系统结构框图如图1所示。

3 方案实现

系统选用Actel公司的ProASIC3 A3P250芯片实现数字部分。系统时钟由外部50 MHz晶振提供,时钟引脚连接到FPGA的CCC全局时钟引脚上;频率可以通过FPGA内部的PLL实现倍频和分频,设定需要的频率。因为在多路脉冲延迟方案中电路的同步是保证控制准确的前提,所以应该首先为电路提供一个基准脉冲。通过PLL将50 MHz的频率倍频,产生一个100 MHz的低频触发脉冲,从而触发各路计数模块开始计数。同时,将100 MHz通过另一计数器模块得到1 kHz的触发脉冲,此时可以根据需要延迟的范围通过MCU编程来设定各计数器的初值,产生一个粗延迟的脉冲信号,实现以10 ns为步进的延迟,延迟分辨率为10 ns级。FPGA内部结构如图2所示。

FPGA将粗延迟脉冲信号送给多路延迟线芯片DS1020进行低位延迟。实际电路中DSl020的8个并行数据引脚(PO~P7)与MCU相连,MCU通过软件程序将延迟时间写入DSl020,并发送指令给EN端口,通知DS1020实现低位延时。通过与MCU相连的8位数据脚

实现lO ns以内的延时,最后输出脚OUTPUT将脉冲信号送至D/A转换器,再经放大器放大后得到总延迟后的输出信号。多路延迟线结构框图如图3所示。

[page]

[page]

4 系统仿真

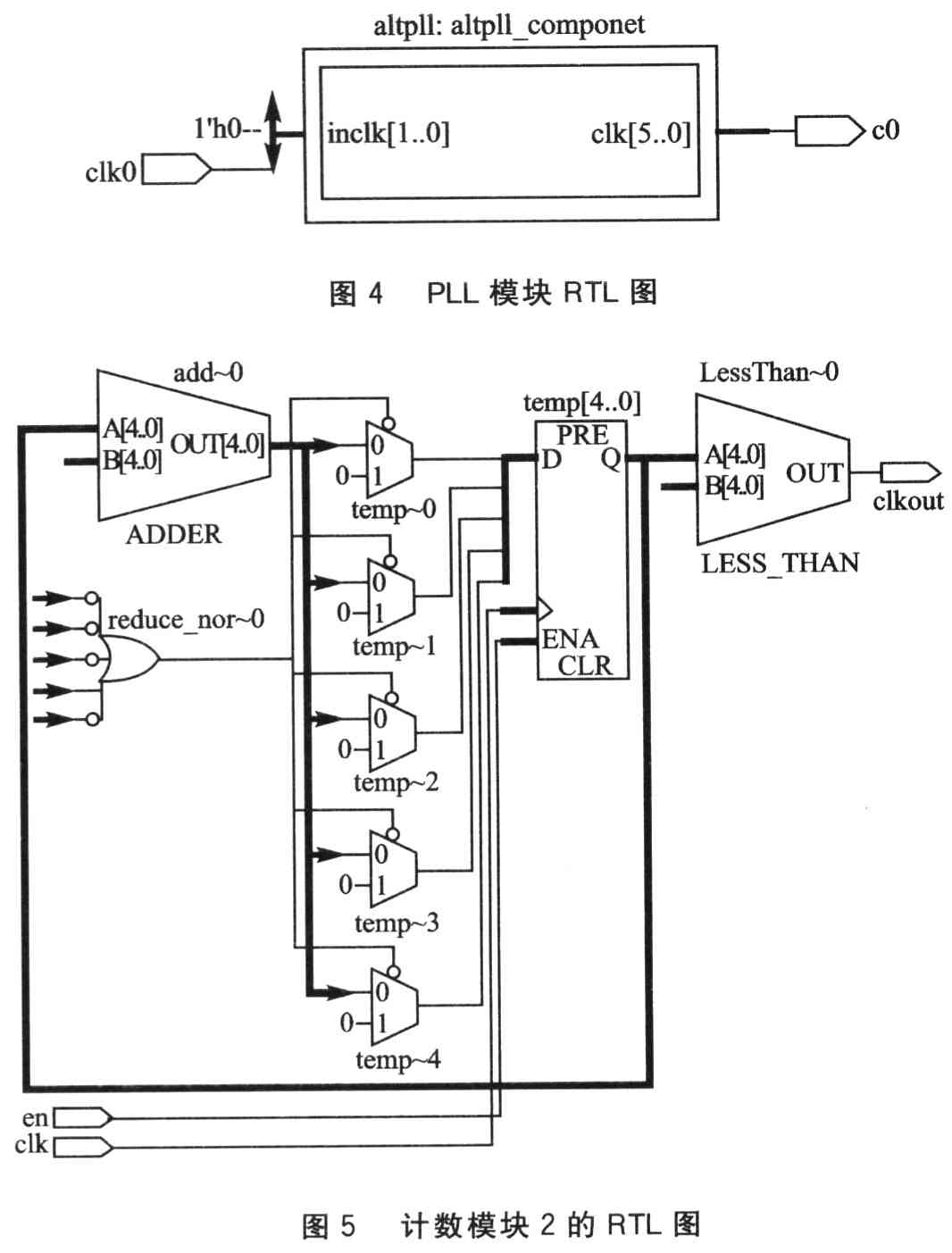

下面给出了核心部分的RTL图及QuartusII时序仿真波形。PLL模块的RTL图如图4所示。

计数模块2的RTL图如图5所示。该模块的输入clk应连接到频率为100 MHz的时钟信号,作为计数脉冲。en是使能信号,应连接到经过计数模块1分频后得到的1 kHz的时钟信号上。假设en信号到来,该信号为高电平时,计数器temp开始计数,到达设定的计数时间后输出高电平,否则为低电平。经过计数模块2后系统完成粗延迟,此时延迟分辨率为10 ns级。

PLL模块实现倍频的功能。其中,输入clk0应连接频率为50 MHz的时钟信号。输出信号cO为100 MHz,分别送给计数模块1和2实现分频和计数脉冲的作用。其仿真波形如图6所示。

计数模块1和2的延迟时间均可由单片机动态写入,本方针波形写入的延迟时间为300 ns。延迟后的波形如图7所示。

结 语

本设计不同于现有的延迟电路,它将数字方法和模拟方法相结合,对多路连续脉冲信号进行大范围高分辨率的动态延迟,将分辨率提高到了O.15 ns级。而且,本系统用Flash FPGA替代现有系统的SRAM FPGA,从而大大提高了系统集成度,降低了成本。

上一篇:FPGA嵌入式系统开发过程中的XBD文件设计

下一篇:Dan Leibholz担任ADI通用DSP工程总监

推荐阅读最新更新时间:2024-05-02 20:44

新能源汽车核心技术详解:电池包 BMS VCU MCU

新能源汽车核心技术详解:电池包 BMS VCU MCU Verilog HDL数字集成电路设计原理与应用

Verilog HDL数字集成电路设计原理与应用

京公网安备 11010802033920号

京公网安备 11010802033920号