按键在数字电路设计中经常用到。按键的弹跳现象是数字系统设计中存在的客观问题。按键是机械触点,当接触点断开或闭合时会产生抖动。为使每一次按键只做一次响应,就必须去除抖动。本文对按键的抖动信号进行了分析,并通过计数器的方式完成了消除抖动电路模块的设计。把该模块应用到按键控制LCD显示的系统中,并在Memec代理的Virtex-4 MB系统实验板上实现了该系统。消抖电路的效果良好,按键控制LCD显示结果正常。

按键开关是电子设备人机交互的主要器件之一。按键大多是机械式开关结构,由于机械式开关的核心部件为弹性金属簧片,因而在开关切换的瞬间会在接触点出现来回弹跳的现象。对于灵敏度比较高的电路,这种弹跳现象引起的信号抖动会造成误动作而影响到系统的正确性。因此,我们需要设计按键弹跳消除电路来去除抖动.。

1.弹跳消除电路的原理和功能

按键开关的典型连线分为低电平有效和高电平有效,本文的是低电平有效。

机械开关的抖动存在三种情况:按下时有抖动,松开时也有抖动;按下时有抖动,松开时无抖动;按下时无抖动,松开时有抖动。机械开关的抖动波形、抖动次数、抖动时间都是随机的,并不是每次都会产生抖动。

不同开关的最长抖动时间也不同。抖动时间的长短和机械开关特性有关,一般为5ms到10ms。但是,某些开关的抖动时间长达20ms,甚至更长。所以,在具体设计中要具体分析,根据实际情况来调整设计。

弹跳现象以及弹跳消除如图1 所示,虽然只是按下按键一次后放掉,结果在按键信号稳定先后竟出现了多个段脉冲,如果将这样的信号直接送到计数器之类的时序电路,结果将可能发生计数超过一次以上的误动作,从而误以为键盘按了多次。因此,必须加上弹跳消除电路,除去短脉冲,避免误操作的发生。

[page]

[page]

2.按键弹跳消除模块的实现

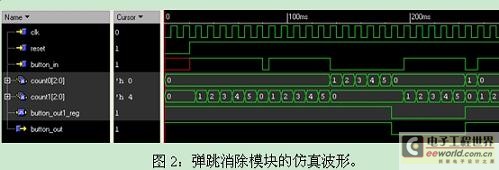

为了使按键弹跳消除模块的更加简洁,并且移植性好,在此用计数器的方式实现消除按键抖动的功能。

2.1 计数器模值的计算

计数器模值的确定是按键弹跳消除效果的关键问题,如果值过大,即采样时间过长,就会漏掉正确的信号;如果值过小,采样时间过短,则会将毛刺误认为是输入信号。

计数器的模值n根据抖动信号的脉冲宽度和采样信号clk的周期大小决定。根据一般人按键的速度小于10Hz(每秒小于10次),所以按键时间大于100ms,按占空比50%计算,按下的时间大于50ms。按这种约定,我们认为按下的时间小于50ms的为抖动信号,按下的时间大于50ms的是按键信号。即n=50ms/采样脉冲信号周期,这样就可以把按下的时间小于50ms的抖动信号滤掉。

在此,根据实验板提供的系统时钟来确定实际需要的模值。实验板提供的系统时钟为100mHz,通过分频后得到25mHz的时钟,50ms*25mHz得到count的模值为21’h1312D0。采用这个模值得到的消抖时间大约为50ms,符合要求。

2.2 程序设计

设计一个高脉冲计数器count1和一个低脉冲计数器conut0。引入一个采样脉冲信号clk,对输入信号button_in进行采样,并对clk进行计数。若button_in为高电平,count1做加法计数,直到count1各位全为1,停止计数,归零,使消抖后的输出信号button_out输出1。若button_in为低电平,count0做加法计数,直到count0各位全为1,停止计数归零,并使消抖后的输出信号button_out输出0。

部分程序如下:

[page]

[page]

3 按键弹跳消除模块的实际应用

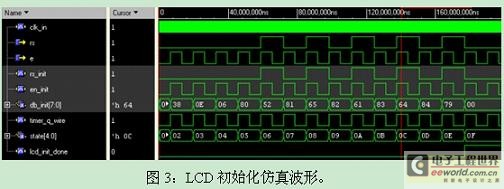

利用Memec virtex-4 开发板,通过开发板上的按钮输入8位的01控制代码,用开发板上的开关输入状态控制位,从而控制板上的1602 C型字符型液晶模块的显示模式和内容。

LCD控制信号生成模块:根据按钮输入,产生控制显示模块的8位控制信号。对按钮送入该模块的1位(0/1)信号进行保存并进行转换,使每8次输入形成一个8位的信号。如果输入不满8位或需重新输入,则取消上次结果;如果确定输入结果正确,则将8位信号保存并输出。

LCD显示控制模块:完成1602 C型字符型液晶模块的初始化,并根据控制信号完成状态转换。

总系统设计如图4:

结束语

本文进行性模块化设计,实现了弹跳消除电路模块、LCD控制信号生成模块和LCD显示控制模块组成的系统的具体功能,在Memec实验板上运行效果良好。并且在用FPGA进行电路调试的时候,可以将该系统嵌入其它电路中,增加需要的测试点和观察点,通过按钮控制显示,可以动态的对电路进行测试,找出问题,使调试更加直观,从而提高的FPGA的内部信号的可观察性,提高验证效率。

上一篇:基于FPGA和DDS技术的正弦信号发生器设计

下一篇:基于FPGA的数字视频转换接口的设计与实现

推荐阅读最新更新时间:2024-05-02 21:06

汽车电子的革新与FPGA-24页

汽车电子的革新与FPGA-24页 Verilog HDL数字集成电路设计原理与应用

Verilog HDL数字集成电路设计原理与应用

京公网安备 11010802033920号

京公网安备 11010802033920号