0 引言

CMI码是传号反转码的简称,它是一种应用于PCM四次群和光纤传输系统中的常用线路码型,具有码变换设备简单、有较多的电平跃变,含有丰富的定时信息,便于时钟提取,有一定的纠错能力等优点。

在高次脉冲编码调制终端设备中广泛应用作接口码型,在速率低于8 448 Kb/s的光纤数字传输系统中也被建议作为线路传输码型。

本文针对光纤通信传输码型的要求和CMI码的编码原理,介绍了一种以EPM系列7064芯片为硬件平台,以Max+PlusⅡ为软件平台,以VHDL为开发工具,适合于CPLD实现的CMI编码器的设计方案。

1 CMI码的编码规则

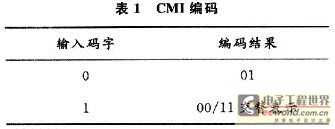

CMI编码规则如表1所示。

在CMI编码中,输入码字0直接输出01码型,较为简单。对于输入为1的码字,其输出CMI码字存在两种结果OO或11码,因而对输入1的状态必须记忆。同时,编码后的速率增加一倍。

2 CMI编码器的建模与实现

首先在原始时钟MUX_Clk的上升沿进行翻转得到二分频时钟Clk,周期为原始时钟的2倍。

然后产生伪随机序列,由3个D触发器产生7位伪随机序列,序列产生原理如图1所示。

任何一个D触发器的输出都可以作为要产生的m序列,则序列以7为周期循环出现,在3个D触发器输出都为0时,语句m_buffer(2)<=(m_bu-ffer(1)xor m_buffer(O))Or((not m_buffer(2))and(not m_buffer(1))and(not m_buffer(O))),可以使第一个D触发器在Clk上升沿到来时输出为1,从而避免陷入“000"的死循环。

最后为“O”码、“1”码的编码:

“O”编码的实现:在原始时钟信号的下降沿对m序列进行检测,当其值为“0”时,将原始信号的二分频后的信号求非赋值给编码输出,即可实现对“O”进行“01”编码。[page]

“1”编码的实现:在原始时钟信号的二分频信号的上升沿对m序列进行检测,如果其值为“1”,用表达式statel<=statel X0R m_buff(O)对“1”的奇偶进行记录;在原始时钟的下降沿,将statel的值赋给编码输出即可实现对“1”的“00”,“11”交替编码。

其中:m_test:产生的m序列;

MUX_DT:CMI编码输出;

MUX_CLK:原始时钟。

3 仿真结果

在Max+PlusⅡ平台下对CMI编码进行编译和仿真,最后得到CMI编码仿真结果。图2是CMI码编码波形图。

在时钟MUX_CLK驱动下工作,m_test是产生的m序列1011100,MUX_的DT为CMI编码输出,可以看到,编码为11010011000101,有一定延时,但编码完全正确。

4 结语

该设计详细介绍了基于CPLD的CMI编码的实现方法。提出利用原始信号的二分频后的信号求非赋值给编码输出,得到“0”的编码,利用缓存对“1”的个数进行记录,而对“1”进行编码的编程思路,利用VHDL进行程序设计实现,在Max+PlusⅡ平台下对设计结果进行仿真,结果完全正确。

实践表明,运用CPLD实现CMI编码具有软件开发周期短、成本低、执行速度高、实时性强、升级方便等特点,而且可以把该电路和其他功能电路集成在同一块CPLD/FPGA中,减少了外接元件的数目,提高了集成度,而且有很大的编程灵活性,很强的移植性,因此有很好的应用前景。

关键字:CPLD FPGA CMI编码

引用地址:

基于CPLD/FPGA的CMI编码设计与实现

推荐阅读最新更新时间:2024-05-02 21:07

基于FPGA的电子设计竞赛电路板的设计

引言 全国大学生电子设计竞赛至今已成功举办了八届, 参赛人数越来越多, 竞赛规模越来越大。大学生电子竞赛在培养学生创新能力、促进高校学风建设及电子信息学科教学改革等方面起到了引导和推进作用。 大学生电子竞赛题目以模拟电子、数字电子、可编程逻辑器件及单片机技术为核心, 涉及电子仪器仪表、通信、高频无线电、自动控制等多学科内容。2007 年电子设计竞赛组委会专家指出: 电子设计竞赛的发展趋势将以模电、数电、FP2GA 为重点。因此, 对于参赛队员来说要获得较好的成绩, 选择合适的题目并进行培训至关重要。笔者针对以FPGA 为核心的竞赛题目特点及竞赛元器件要求, 设计制作了竞赛电路板, 组成框图如图1 所示。 图1

[单片机]

基于FPGA实现VLIW微处理器的设计与实现

超长指令字VLIW(Very Long Instruction Word)微处理器架构采用了先进的清晰并行指令设计 。VLIW微处理器的最大优点是简化了处理器的结构,删除了处理器内部许多复杂的控制电路 ,它能从应用程序中提取高度并行的指令数据,并把这些机器指令均匀地分配给芯片中的众多执行单元 。本设计是针对VLIW微处理器的基本功能设计实现的,是针对64位指令字和192位数据进行操作处理,主要功能是将指令和数据分别划分到3个并行操作单元中,在执行单元中根据3个并行指令控制,对3个并行操作单元的数据进行并行处理,同时对操作处理数据进行存储处理管理。由于篇幅所限,只是将取指令单元、译码单元、执行单元、写回单元和寄存器堆这5个单元的

[嵌入式]

使用CPLD实现QWERTY键盘

随着手机及其他便携手持装置的功能不断增加,设计的取舍平衡亦日趋精细。文本信息与网络浏览等流行功能都要求更多的数据输入,而这对于传统的双音多频 (DTMF) (0-9, #, *) 键盘会比较困难。使用这种键盘要求多端数据输入,输入效率低而且容易出错。

图 1 – QWERTY 键盘(摩托罗拉 A630)

使文本输入更为方便的一个方法是使用 QWERTY 键盘(见图 1)。这种键盘采用 40 个或更多按键,而 DTMF 手机通常采用 12 个。当然,多出的按键会使手机体积变大,用到的电子组件也更多。

然而,文本信息用户可能乐意以体积换取 QWERTY 键盘,因为文本输入大为简便了,而且两个大拇指都可以用来输入文

[嵌入式]

OpenCL助攻 FPGA挺进软体定义资料中心

OpenCL让现场可编程闸阵列(FPGA)进军软体定义资料中心(SDDC)更添助力。因应云端产业近来吹起软体定义资料中心发展热潮,FPGA业者积极推出可支援OpenCL设计工具的新一代解决方案,让软体工程师可直接于FPGA上进行编程,以加速软硬体整合,并打造符合实际应用需求的资料中心系统。 Altera资深副总裁暨总经理Jeff Waters表示,该公司已推出能支援OpenCL设计工具的FPGA产品,加速软体定义资料中心的开发。 Altera资深副总裁暨总经理Jeff Waters表示,资料中心的建置将朝以下方向迈进,亦即降低联网速度的延迟、减少能源与冷却系统使用、优化中央处理器(CPU)负载,以及强化资料撷取与分

[嵌入式]

基于CPLD的开放式四轴运动控制器的设计

摘要: 一种基于PC机的开放式四轴运动控制平台的软、硬件组成及设计方法。采用CPLD简化了平台硬件结构,利用PC机的资源实现了“软运动控制”功能。系统具有结构开放、使用方便、成本低廉、性能可靠等特点,可以灵活地实现定制应用。

关键词: 开放式系统 运动控制器 CPLD

作为运动控制的核心部件,运动控制器普遍采用16位或32位微控制器,其灵活的系统集成方式和高速的指令执行速度提高了运动控制性能、改善了控制系统的精度、增强了系统构成的灵活性。如DeltaTau公司的PMAC系列、MEI公司的XMP系列的产品,均采用了高速数据信号处理器(DSP)和现场可编程门阵列(FPGA)技术,一般可以控制1~8个

[应用]

Adaboost算法的FPGA实现与性能分析

Adaboost 算法是Freund 和Schapire 于1995 年提出的,全称为Adaptive Boosting。它是 Boosting 算法的改进,意为该算法通过机器训练与学习不断自适应地调整假设的错误率,这 种灵活性使得Adaboost 算法很容易与实际应用联系起来。2001 年,微软研究院的P.Viola 提出了基于Haar 特征的Adaboost 算法 ,创造性地将积分图的概念引入到人脸检测的特征 计算当中,由于此算法使用了大量尺寸不一的矩形作用来表征人脸。并且该算法中用以检测 人脸的分类器是采用的级联结构,按照由弱到强的顺序组织的,其优点在于按照统计概率, 在图像检测的一开始就能够将大部分不包含人脸的区域排除在

[嵌入式]

技术文章—2D NoC可实现FPGA内部超高带宽逻辑互连

Achronix 最新基于台积电(TSMC)的7nm FinFET工艺的Speedster7t FPGA器件包含了革命性的新型二维片上网络(2D NoC)。2D NoC如同在FPGA可编程逻辑结构上运行的高速公路网络一样,为FPGA外部高速接口和内部可编程逻辑的数据传输提供了超高带宽(~27Tbps)。 图1 Speedster 7t FPGA结构图 NoC使用一系列高速的行和列网络通路在整个FPGA内部分发数据,从而在整个FPGA结构中以水平和垂直方式分发数据流量。NoC中的每一行或每一列都有两个256位的、单向的、行业标准的AXI通道,可以在每个方向上以512Gbps(256bit x 2GHz)的传输速率运行。

[嵌入式]

由可编程逻辑器件与单片机构成的双控制器

摘要: 介绍一种利用可编程逻辑器件CPLD与单片机AT89C51串行双向通信而构成的双控制器。

关键词: CPLD AT89C51 串行通信

在传统的控制系统中,人们常常采用单片机作为控制核心。但这种方法硬件连线复杂,可靠性差,且单片机的端口数目、内部定时器和中断源的个数都有限,在实际应用中往往需要外加扩展芯片。这无疑对系统的设计带来诸多不便。

现在有很多系统采用可编程逻辑器件CPLD作为控制核心。它与传统设计相比较,不仅简化了接口和控制,提高了系统的整体性能及工作可靠性,也为系统集成创造了条件。但可编程逻辑器件的D触发器资源非常有限,而且可编程逻辑器件在控制时序方面不如单片机那样方便,很多

[应用]

汽车电子的革新与FPGA-24页

汽车电子的革新与FPGA-24页 嵌入式网络那些事:LwIP协议深度剖析与实战演练

嵌入式网络那些事:LwIP协议深度剖析与实战演练

京公网安备 11010802033920号

京公网安备 11010802033920号