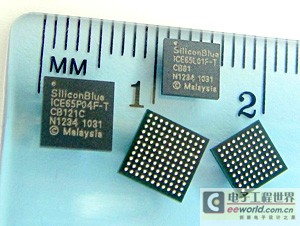

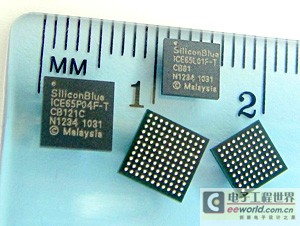

SiliconBlue Technologies宣布推出iCE65 mobileFPGA™系列的两款新元件封装。拥有1,280个逻辑单元的iCE65L01元件如今采用5x5毫米、81球BGA封装(拥有63个用户输入/输出引脚);拥有3,520个逻辑单元的iCE65P04元件则采用6x6毫米、121球BGA封装(拥有95个用户输入/输出引脚)。

如今的手机工程师面临着一项艰巨的挑战。他们必须每年推出一款拥有创新和差异化功能的新手机。不幸的是,如今的应用处理器需要花2至3年的时间进行开发,并且仍有可能不包含工程师需要的功能。此外,这些新功能要求大量的逻辑和更多的输入/输出量,而这些可能是应用处理器无法提供的。通过使用SiliconBlue的iCE65 mobileFPGA元件,设计师可以通过补强他们现有的应用处理器来为他们的手机增添新功能,从而在竞争高度激烈的移动市场上实现快速创新。

SiliconBlue首席执行官Kapil Shankar说:“根据我们在手机市场的经验,为了装备丰富的功能,工程师通常需要高逻辑容量和最大的输入/输出量同时实现在一个小尺寸的封装内。连同我们已经取得广泛成功的晶圆级芯片尺寸封装(WLCSP),这些新元件必将成为实现陀螺仪、加速计和双显示器等众多功能所需要的产品。”

关键字:BGA FPGA SiliconBlue 手机应用

引用地址:

SiliconBlue BGA封装的最高逻辑容量FPGA

推荐阅读最新更新时间:2024-05-02 21:08

集系统级FPGA芯片XCV50E的结构与开发

摘要:VirtexE系列是XILINX公司生产的新型FPGA芯片,可用来进行数十万逻辑门级的系统设计和百兆赫兹级的高速电路设计。文中介绍了XCV50E芯片的结构特性、设计流程和配置过程,给出了具体的电路图和配置流程图。

关键词:FPGA 可配置逻辑块 设计流程 配置

XCV50E是XILINX公司VirtexE系列系统级FPGA芯片中的一员。其主要资源有71693个系统门、65536位块内存和176个用户I/O口(其中包括83对差分I/O口)。

主要特性有:1.8V超低核心电压、支持20种高速总线标准、八个全数字延迟锁定环、0.18微米6层金属工艺、支持IEEE 1149.1边界扫描。VirtexE系列FPGA芯片具有卓越

[半导体设计/制造]

基于FPGA的步进电机控制系统的设计方案

0 引言

步进电机是将电脉冲信号转变为角位移或线位移的开环控制电机,输入脉冲总数控制步进电机的总旋转角度,电机的速度由每秒输入脉冲数目所决定,因此易实现机械位置的精准控制。而且由于步进电机价格低廉、可控性强等特点,使其在数控机床传送控制等自动控制领域中得到了广泛的应用。但随着技术的发展以及企业生产的要求,步进电机传统的以单片机等微处理器为核心单元的控制系统暴露出了如下缺点:控制策略单一不利于实现人机交互,而且控制电路复杂、控制精度低、生产成本高,系统稳定性不够,步进分辨率低、缺乏灵活性,低频时的振荡和噪声大,而且受步进电机机械结构和空间的限制,步进电机的步距角不可能无限的小,难以满足高精度开环控制的需求。由于FPGA编程方式简单

[嵌入式]

机器学习成长速度惊人,FPGA和ASIC芯片有望成为新主力

在2016年初,机器学习仍被视为科学实验,但目前则已开始被广泛应用于数据探勘、计算机视觉、自然语言处理、生物特征识别、搜索引擎、医学诊断、检测信用卡欺诈、证券市场分析、语音和手写识别、战略游戏与机器人等应用领域。在这短短一年的时间内,机器学习的成长速度超乎外界预期。下面就随网络通信小编一起来了解一下相关内容吧。 Deloitte Global 最新的预测报告指出,在 2018 年,大中型企业将更加看重机器学习在行业中的应用。和 2017 年相比,用机器学习部署和实现的项目将翻倍,并且 2020 年将再次翻倍。 目前,有越来越多的类型开始丰富“AI芯片”这个新名词,包括 GPU、CPU、 FPGA 、 ASIC 、TP

[网络通信]

基于FPGA的计算机防视频信息泄漏系统设计

假如显示终端为数字微镜DMD(Digital MicromirrorDevice)显示器。该显示器将计算机每个像素点的图像信号经过数字光处理DLP(Digital Light Processing)后,存入SDRAM双向缓存器,当一帧图像接收完毕时,内部数据处理电路同时激发各像素点对应的微镜运动,完成一帧图像的显示。DMD显示器峰值数字驱动电压不超过33.5V,电磁辐射很低,且各微镜片同时驱动,形成相互干扰的向外辐射信号,解码难度极大,从而使其成为无信息泄漏的显示器。此时,视频电缆的辐射在整个视频通路的辐射中就占主导地位。如果在视频信号经过视频电缆传输到显示器之前就对其进行处理,则可以有效地降低电磁辐射和信息泄漏。 1 视频信息泄

[应用]

FPGA的时代到了!

从28纳米到3D堆叠,FPGA身价突然翻涨,不再是过去那个扮演配角的被支配角色,反而由于其功能大跃进、重要性大增,目前在许多应用中,已经逐渐成为支配系统运作的主角。而现阶段FPGA的三大发展方向:28纳米、3D堆叠,以及SoC系统化,也成为FPGA制霸市场的决胜关键。 FPGA从配角变主角 FPGA市场对于28纳米的争霸,已经从几年前的蓝图布局,到产品试制,到目前已正式量产,也宣告FPGA真正走入了28纳米制程的新阶段。主要厂商包括Altera、Xilinx、Lattice等,纷纷端出28纳米FPGA大餐喂饱市场那张饥渴的大嘴。28纳米与FPGA划上等号,只要拥有28纳米产品,就象征了该厂家所拥有的技术实力与研发创新,而端不

[嵌入式]

基于FPGA的IJF数字基带编码的实现

1 引言 20世纪80年代初,加拿大渥太华大学的费赫教授(K.Feher)领导的科研小组发明了IJF-OQPSK调制技术。IJF-OQPSK中文名称叫做无码间干扰和抖动-交错正交相移键控。他是现代数字恒包络调制技术中新型的调制技术之一。 进行这种调制时,首先要对数字基带信号进行IJF编码,将其变换成一种无码间干扰和抖动、频谱主瓣窄、具有快速滚降的基带波形,然后再用OQPSK调制。这样,调制后的基带信号就具有了以下特点:以调波的相位平滑连续,而且每个号码内的相位变化不会超过π/2,以调波的包络近于恒包络,频谱主瓣窄,高频滚降快,带外能量低。 2 IJF编码原理 在数字传输系统中,与误码率有直接关系的是接

[嵌入式]

基于FPGA的IRIG-B(DC)码解码

摘要:在分析了IRIG-B(DC)码码型特点的基础上,提出了一种IRIG-B(DC)时间码解码的设计方法。该方法由少量外围电路与一片现场可编程门阵列(FPGA)芯片组成,来实现对IRG-B(DC)码的解码、1 PPS信号输出、实时时间显示以及串行异步通信。与传统的方法相比,该设计方案具有体积小、成本低、工作稳定等优点,完全能够替代传统的B码机箱的功能。 关键词:IRIG-B(DC);FPGA;硬件描述语言;串行通信 随着电力自动化水平的提高,电力对时间的同步要求越来越迫切、时间同步的精度要求越来越高。采用GPS全球卫星定位系统的时间同步功能,是提高电力生产和管理自动化水平、确保运行质量的一条最佳途径。国家电力公司、各大电网

[嵌入式]

基于ARM的FPGA加载配置实现

0引言 基于SRAM工艺FPGA在每次上电后需要进行配置,通常情况下FPGA的配置文件由片外专用的EPROM来加载。这种传统配置方式是在FPGA的功能相对稳定的情况下采用的。在系统设计要求配置速度高、容量大、以及远程升级时,这种方法就显得很不实际也不方便。本文介绍了通过ARM对可编程器件进行配置的的设计和实现。 1 配置原理与方式 1.1配置原理 在FPGA正常工作时,配置数据存储在SRAM单元中,这个SRAM单元也被称为配置存储器(Configuration RAM)。由于SRAM是易失性的存储器,因此FPGA在上电之后,外部电路需要将配置数据重新载入到片内的配置RAM中。在芯片配置完成后,内部的寄存器以及I/O管脚必

[应用]

汽车电子的革新与FPGA-24页

汽车电子的革新与FPGA-24页 嵌入式网络那些事:LwIP协议深度剖析与实战演练

嵌入式网络那些事:LwIP协议深度剖析与实战演练

京公网安备 11010802033920号

京公网安备 11010802033920号