摘要:为进行高精度信号源的设计,同时降低设计成本,以Cyclone II系列低端FPGA为核心,利用直接频率合成技术,对正弦信号等数据进行1/4周期压缩存储到ROM中,在外部时钟频率为50 MHz,实现了正弦信号源的设计,同时,实现三角波、锯齿波、矩形脉冲及2-ASK、2-PSK和2-FSK等数字调制信号,系统还具有扫频、指定波形次数等功能。仿真结果表明,信号源精度高,频率调整步进可达0.034 92 Hz,频率范围为0.034 92 Hz~9.375 MHz,制作成本低,功能丰富。

0 引言

近年来电子信息技术飞速发展,使得各领域对信号源的要求不断提高,不但要求其频率稳定度和准确度高,频率改变方便,而且还要求可以产生任意波形,输出不同幅度的信号等。DDFS技术是自上世纪70年代出现的一种新型的直接频率合成技术。DDFS技术是在信号的采样定理的基础上提出来的,从“相位”的概念出发,进行频率合成,不但可利用晶体振荡的高频率稳定度、高准确度,且频率改变方便,转换速度快,便于产生任意波形等,因此,DDFS技术是目前高精密度信号源的核心技术。

1 DDFS技术原理及相关参数计算

DDFS技术的原理:将对正弦信号(或其他信号)的采样量化数据存入ROM存储器中,在时钟的控制下,依次或隔一定步进读取ROM中的数据,再通过D/A转换芯片转换成模拟信号,进一步经后级的低通滤波器、功率放大电路等来实现频率合成。其主要的组成部分包括相位累加器、数据存储ROM表、D/A转换、低通滤波器及功率放大电路等。

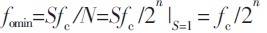

根据DDFS原理,DDFS主要参数包括正弦信号的采样点数N,最高输出频率fomax,最低输出频率fomin及频率分辨率△fo等。本设计要产生1 Hz~10 MHz范围内,步进为1 Hz的正弦信号,参数计算如下:

1)输出频率通式fo  ,N为采样点个数,S为步进长度。

,N为采样点个数,S为步进长度。

2)输出最高频率fomax  ;根据奈奎斯特采样定理,1个周期至少采样两个点才能保证原信号的频率信息。而实现工程应用中一个周期至少采样16个点或更多点,以保证输出信号的质量。输出最高频率要达10 MHz,所需的系统时钟信号频率fc为160 MHz。由于本文使用的外接晶振为50 MHz,则必须使用CycloneII系列FPGA自带的数字锁相环(PLL)对输入时钟进行倍频,以达到所需的时钟频率160 MHz。可取3倍频到150 MHz。此时系统输出的最高频率为:fomax=150 MHz/16=9.375 MHz。虽然通过提高锁相环的倍频数,可进一步提高工作频率,从而可以产生更高的输出信号频率,但由于在进行DDFS模块设计时,其所能工作的最高频率将制约着倍频数。

;根据奈奎斯特采样定理,1个周期至少采样两个点才能保证原信号的频率信息。而实现工程应用中一个周期至少采样16个点或更多点,以保证输出信号的质量。输出最高频率要达10 MHz,所需的系统时钟信号频率fc为160 MHz。由于本文使用的外接晶振为50 MHz,则必须使用CycloneII系列FPGA自带的数字锁相环(PLL)对输入时钟进行倍频,以达到所需的时钟频率160 MHz。可取3倍频到150 MHz。此时系统输出的最高频率为:fomax=150 MHz/16=9.375 MHz。虽然通过提高锁相环的倍频数,可进一步提高工作频率,从而可以产生更高的输出信号频率,但由于在进行DDFS模块设计时,其所能工作的最高频率将制约着倍频数。

3)输出最低频率fomin  要做到fc/N=1 Hz,则N=2n=150M,n=log2(150 M)=[27.16]=28。即ROM中的采样数据为150M点,对应的寻址ROM的地址位数据长度为28位。

要做到fc/N=1 Hz,则N=2n=150M,n=log2(150 M)=[27.16]=28。即ROM中的采样数据为150M点,对应的寻址ROM的地址位数据长度为28位。

4)频率分辨率△fo △fo=fc/2n,已知ROM的地址位至少为28位,本设计中取32位,这样所得的fomin及△fo为150M/232=0.03492 Hz。

5)ROM数据1/4周期压缩 ROM的寻址地址位长度为32位,即所需的ROM单元数将为232个。但ROM中并不需要存储这么多数据点,因为数据重复量非常大,只需存入一定量的点即可。本设计中,根据正弦信号周期内的数据特点,对周期正弦信号的(0,π/2)区间进行1 024点的采样,进行12位的量化并存入ROM。这相当于对(0,2π)区间进行了4 096个点的采样,ROM数据量压缩为1/4。此时,相位累加器输出地址位相应修改为30位。这样以来,在进行数据输出时,对(π,2π)区间的数据要做取补的运算。因为在这个区间上正弦信号数据为负值。

6)ROM地址位长度 通过数据压缩,ROM的地址只需10位,此时,只需要对相位累加器的30位地址位输出值,取高10位用于ROM寻址即可。

7)步进位长度 步进最大应为232/24=228,即为28位的二进制数。

2 DDFS的FPGA实现

本设计中DDFS模块的设计原理图如图1所示。主要包括地址发生单元(相位累加器)、ROM存储单元、补码转换电路及一些数据延时单元组成。工作每一个部分均采用VHDL语言进行描述并生成模块以便在顶层文件中进行调用。

图1 DDFS的FPGA实现

1)相位累加器(地址发生单元) 设计思路为根据输入的STep值,计算出1/4周期采样的点数m,然后在时钟作用下进行计数,当计数值达m个时,说明一个象限内已经取完点,此时象限控制字自加1,计数变量重新置零,此时依次产生了如下(0,Step,…,(m-1)Step)的30位二进制地址。截取此地址位的高10位即可用于对ROM空间的寻址。根据正弦信号的特点,下一象限产生的地址应该为:((m-1)Step,(m-2)Ste-p,…,0),依此类推。且象限控制字自加。

2)ROM存储单元 ROM存储单元的数据可以通过Matlab进行计算获得,并将其存储为dds_sin.mif。也可采用其他高级语言来获得ROM存储数据。

3)补码转换电路 (0,π)数据直接输出,(π,2π)象限的数据应进补码运算。对此补码电路稍作修改,即可同时输出相位正好相反的两路正弦信号。

4)数据延时单元 为了使地址单元输出的象限控制字等与异步ROM配合工作,应对相应的数据进行延时,以保证输出数据的正确。本设计中对相位控制字延了一个时钟周期。

3 DDFS设计模块性能及所占资源分析

1)DDFS模块时序分析 首先应当分析DDFS模块的最大时钟频率fmax,因为它决定着系统能否工作在150 MHz或更高的时钟频率。通过Qu-artusII6.0自带的Timing Analyzer Tools时序分析,本设计中的DDFS模块的fmax=179.18 MHz,高于150 MHz。故本设计理论上可输出的正弦信号的最高频率可达11.198 MHz。

2)DDFS模块资源分析 本设计使用的是FPGA为Ahem公司的CycloneⅡ系列芯片EP2C5Q208C8,所设计的DDFS模块所占片上资源逻辑单元仅为2%,所占的数据存储空间为12 288 bits,约占总的数据存储空间119 808 bits的10%。可见,通过对ROM存储表进行数据后,DDFS模块所占片存储资源较少。因此,FPGA上ROM资源允许调用若干DDFS模块来完成各种功能模块,如2-PSK、2-FSK、2-ASK等数字调制。

4 系统性能仿真与测试

以DDFS模块为基础,本设计实现了两组反相的正弦信号、余弦信号、三角波信号、锯齿波、2-PSK、2-FSK、2-ASK等数字调制信号、扫频及任意次波形输出等功能。

在本设计中,仿真主要通过QuartusII6.0自带的Simulator Tool来进行数据仿真。从仿真图上可验证该设计的正确性。同时,通过Qu-artusII6.0自带的Signal TapⅡ逻辑分析仪来进行逻辑功能的硬件验证。

1)基本正弦信号输出 在本设计中同时产生两组信号,一组为正弦信号,另一组与之反相。图2是步进长度设定为(50 000 000)10时的正弦信号Signal Tap II采样图,其频率分别为fo=582.076 6 kHz。此时输出信号为可产生的最高频率。从所获得的输出信号的波形上看,频率较低时,曲线稳定且光滑;频率较高时,波形失真也并不大,可以通过后级滤波网络进行波形的进一步平滑。且频率稳定度相当高。

图2 S= (50 000 000)10时的正弦信号Signal Tap II采样图

在外部时钟50 MHz的频率下,可以获得的最高频率约为3.125 MHz,最低频率及频率步进可以低至11.64 MHz。当对外部时钟信号倍频至150 MHz后,最高输出频率可以达到9.375 MHz,最低频率及频率步进可以低至34.925 MHz。进一步提高频率及模块性能,能获得更大频率范围的信号。

另外,从图中可以看出,实际上地址输出信号是一组频率为正弦信号频率两倍的三角波信号。可见,在产生正弦信号输出的同时,还可以产生一组2倍频的三角波输出信号,只需取地址位的高12位作为输出即可。

2)2-ASK、2-FSK、2-PSK数字调制信号 要产生2-ASK、2-FSK、2-PSK等数字调制信号比较容易。只需将数字基带信号在其传输时钟信号的作用下,逐位输入模块,用基带数字信号的‘1’和‘0’来选择不同幅度、频率或相位的正弦信号输出即可。

2-ASK信号:用3.125 MHz的信号表示数字信号的‘1’,用输出幅度为0表示数字信号的‘0’。

2-FSK信号:用3.125 MHz的信号表示数字信号的‘0’,用582.077 kHz的信号表示数字信号的‘1’,如图3所示。

图3 2-FSK信号字调制信号

2-PSK信号:用初始相位为0的正弦信号的‘1’,用初始相位为180°的信号表示数字信号的‘0’。如图4所示。

图4 2-PSK信号字调制信号

3)扫频功能 扫频功能的实现是通过改变步进来实现的。每产生一个周期的正弦信号以后,将步进递加,为便于观测,设计中设置S初始值为(50 000 000)10,步进递增幅度为(10000000)10,实现了扫频功能,扫频起始频率为582.077 kHz。扫频步进约11*15 kHz,扫频信号如图5所示,同时可以提供各频率信号的同步信息。只要改变步进初始值及递增幅度即可完成更宽扫频范围及扫频步进更佳的扫频信号。事实上,FM信号也可以通过对输出信号的步进的控制来加以实现。

图5 扫频信号

5 硬件电路的实现

设计的最终目的是为了用硬件实现电路,因此,还要设计输入步进设置及模式选择的键盘模块、频率设置数据显示模块等VHDL程序模块;后级的低通滤波网络,功率放大电路等等。完成这些工作,即可完成一个完整的DDFS信号源的设计与制作。

6 结束语

本文的创新点为对DDFS设计进行优化,充分利用Cyclone II系列FPGA的片上资源,产生了最高频率可达9.312 5 MHz.最低频率分量及频率分辨率低至MHz量级的正弦信号。通过进一步优化DDFS各模块的性能,如减少相位累加器、数据取补码等模块的运算时间,进一步提高系统工作的最高频率;进一步优化后级滤波网络的特性等,就可以获得性能曲线更平滑,输出频率更高,带负载能力更强的优质的信号源。同时还可以增加FFT算法模块,对信号进行频谱分析等其他功能。

上一篇:基于FPGA的高效FIR滤波器设计与实现

下一篇:基于FPGA的AD9910控制设计

推荐阅读最新更新时间:2024-05-02 21:19

汽车电子的革新与FPGA-24页

汽车电子的革新与FPGA-24页 控制系统计算机辅助设计 — MATLAB语言与应用

控制系统计算机辅助设计 — MATLAB语言与应用

京公网安备 11010802033920号

京公网安备 11010802033920号