距离测量是测试技术中的一项基本测试技术,其几乎贯穿于工程实践的每个领域。在军事航天领域,由于其特殊的需求,对测距系统的量程、实时性和精度要求越来越高,而扩频测距由于其抗干扰能力强、精度高、作用范围广、隐蔽性好、适应性强、全天候等优势,在测距系统中得到了重视。

扩频测距也称伪码测距,它是采用一个较长周期的PN码序列作为发射信号,将它与目标反射或转发回来的PN码序列的相位进行比较,即比较两个码序列相差的码片数,从而看出其时间差,换算出发射机与目的地之间的距离。如果码片选得很窄,即码速率做得很高,那么就可以完成高精度的测距。但随着码速率的提高和码周期的加长,传统的捕获时间将达到不可容忍的地步,所以需要考虑快速捕获算法。

由扩频码的自相关函数可知,只有在t’=(t-τ)时,扩频解调输出V(t)的信号最大。根据τ就能算出两地的距离 ,c为电磁波传播速度。

,c为电磁波传播速度。

由于计算两序列的自相关函数 需要用循环卷积代替自相关函数来计算扩频测距系统中的码片偏移,可以节省运算时间(大约为1/114),加快捕获过程。设x(n),y(n)分别为现有发射PN码与反射回来的PN码,序列长度为N,对它们分别做N点FFT,记

需要用循环卷积代替自相关函数来计算扩频测距系统中的码片偏移,可以节省运算时间(大约为1/114),加快捕获过程。设x(n),y(n)分别为现有发射PN码与反射回来的PN码,序列长度为N,对它们分别做N点FFT,记

可知R(m)为现有发射PN码与反射回来的PN码之间的相关值序列,长度为N,可知当R(m)中最大值的序列号减1即为码片差。

1 仿真方案设计

首先由m序列发生器产生出两路序列长度为N的PN码,其中一路经过延时模块以后与另一路分别进入FFT模块进行FFT运算,将进行FFT后的两组数据运算后进入IFFT模块得出序列组,由序列组得出两路序列之间的码片偏移数,从而算出其时延。系统总体框图如图1所示。

[page]

[page]

2 主要模块仿真结果

2.1 PH码产生模块

本设计选取的PN码为63位,本征多项式为x6+x+1。该PN码产生器由VHDL语言编写,其仿真结果如图2所示。

2.2 FFT转换模块

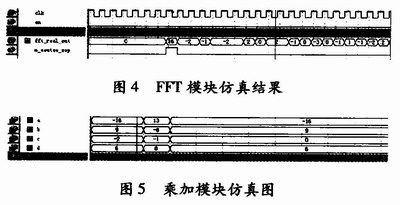

该模块是本设计的核心模块,由输入缓冲器、FFT运算器、控制器构成,完成对数据的FFT变换。将PN码发生器产生的数据存入输入缓冲器中,在控制器的控制下,FFT运算模块从输入缓冲器中读取出数据值进行FFT变换,然后得出输出数据。图3所示为FFT模块的输入输出关系。fft_imag_out,fft_real_out分别为输出数据的实部、虚部和修正因子,m_soutoe_sop为输出数据的起始位。

2.3 计算模块

设两路信号进行FFT后的数据为

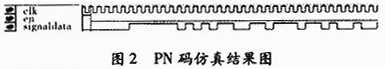

可见对进行FFT变换后需要进行的运算处理其实质是一个乘加,一个乘减和一个加法运算,其中乘加运算仿真结果如图4、图5所示。

[page]

[page]

2.4 判断模块

判断模块的主要功能是对IFFT后的序列的最大值进行判断,得出其最大值所在的序列号减1就为其码片差τ。clk为时钟信号,rest为开始信号,data_in为输入数据,data_out为输入数据data_in中最大值所在的序列号减1。图6为判断模块仿真结果。

2.5 系统总设计图及仿真结果

本设计采用自顶向下的设计方法,利用VHDL语言描述出扩频测距快速捕获的各个功能模块。图7所示为总体仿真结果,图中fft_imag_ outf,fft_real_outf为ifft后的数据,data_out为输出数据,由此可见,仿真结果与设定的τ=3一样,验证了本设计的可行性。

3 结束语

采用FFT代替自相关函数计算扩频系统中的码片偏移可节省硬件计算时间。经过硬件的优化设计与仿真,在Altera Straix II系列FPGA上,时钟频率达到109.1 MHz,捕获时间和计算时间大约在2μs,捕获时间提高。此外,由于扩频技术可以极大地抑制突发干扰和脉冲干扰,所以扩频测距比起传统的测距方法,如激光测距,超声测距等方法能适用于更恶劣的环境,如卫星测控,而由于使用快速捕获技术,可进一步提高实时性,在对测距实时性要求更高的引信技术中也可以采用。

关键字:FPGA 扩频测距 距离测量 伪码测距 PN码

引用地址:

基于FPGA的扩频测距快速捕获仿真研究

推荐阅读最新更新时间:2024-05-02 21:24

FPGA的可重构测控系统应用设计的研究

1 可重构测控系统的提出 测控系统一般是指基于计算机实现数据采集和控制的系统。测控系统在工业现场控制、家庭数字化管理、通信和网络等方面应用广泛,并不断向低成本、高速、高性能、智能化、开放化方向迈进。但现代测控系统在设计和应用中仍然面临不少的难题: ①设计速度难以适应产品更新换代的快速变化。一般测控系统的设计都是针对某个特定的任务,从设计到投入使用的周期至少1~2年,甚至长达4~5年。因此,在设计阶段堪称先进的方案往往在投入使用伊始就已落后了。 ②设计方案功能固定,通用性差,难以满足不同层次、不断变化的用户需求。测控系统设计针对具体用户,配置各异,通用性较差。如何满足不同用户、不同层次的需要,尤其是多任

[嵌入式]

“最大”的芯片,都长什么样?

人类一直致力于把芯片从大做小。无论是卷制程,还是把它塞到各种可穿戴装备里,在有限的空间里发挥更多性能永远都是芯片行业的金科玉律。 而事实上,我们也会放开芯片的面积,追求更高的性能和能效比。那么,不同芯片中,哪些企业做成了最大? 付斌|作者 电子工程世界(ID:EEworldbbs)|出品 82.4cm²的图像传感器 还记得那个刷爆朋友圈的“网红球”吗? 对,就是美国内华达州拉斯维加斯斥资23亿美元,花费7年时间建造的“Vegas Sphere”。它高112米、最宽157米,一举刷新世界纪录,成为世界上最大的球形建筑,也因为其巨大的视觉冲击力,也成了打卡的标志物。今年的CES,便是从这里拉开序幕。

[嵌入式]

基于DSP和FPGA的机器人声控系统设计与实现

1 引言

机器人听觉系统主要是对人的声音进行语音识别并做出判断,然后输出相应的动作指令控制头部和手臂的动作,传统的机器人听觉系统一般是以PC机为平台对机器人进行控制,其特点是用一台计算机作为机器人的信息处理核心通过接口电路对机器人进行控制,虽然处理能力比较强大,语音库比较完备,系统更新以及功能拓展比较容易,但是比较笨重,不利于机器人的小型化和复杂条件下进行工作,此外功耗大、成本高。

本次设计采用了性价比较高的数字信号处理芯片TMS320VC5509作为语音识别处理器,具有较快的处理速度,使机器人在脱机状态下,独立完成复杂的语音信号处理和动作指令控制,FPGA系统的开发降低了时序控制电路和逻辑电路在PCB板所占

[嵌入式]

东亚LTE设备需求强劲 FPGA喜迎4G商机

东亚地区长程演进计画(LTE)设备需求,驱动现场可编程闸阵列(FPGA)业者营收攀升。2014年中国大陆及台湾陆续启动LTE商转,带动庞大的LTE设备购置及基础建设投资潮,深耕通讯领域有成的FPGA业者也趁着这波潮流搭上顺风车,大发LTE财。 赛灵思(Xilinx)亚太区销售与市场副总裁杨飞表示,中国大陆于2013年底发放LTE营运牌照后,业界都在引颈期盼这个全球最大的内需市场将为LTE供应链带来一波新气象;果不其然,2014年中国大陆三大电信营运商陆续启动LTE商转,加上台湾LTE网路也随后开通,两岸的LTE设备投资、采购潮更发挥了加乘效应。 杨飞进一步指出,两岸的LTE网路陆续启动商转后,基地台设备、基础建设的

[嵌入式]

利用可编程逻辑实现高性能的罪犯抓捕系统

由于高科技工具成为抓捕罪犯的武器中越来越关键的部分,因此执法机构和安全专业人员不断寻求更快更方便的数据收集和解读方式就不足为奇了。针对这一领域的应用越来越复杂,必须适应不断演变的要求,并把成本控制在机构的有限预算范围之内。鉴于此,具有高性能、灵活性和高成本效益等优势的可编程逻辑(PLD)解决方案无疑是一种理想的解决方案。 两个大学生团队利用FPGA和嵌入式软核处理器开发了两个抓捕罪犯系统的原型,一个是带无线自动追踪摄像机的警车支持系统,一个是防止安全系统被突破的指纹识别系统。 盯住可疑对象不放-即使是高速情况下 当追踪行动启动时,警官只有很短的时间用来激活警笛、向控制中心作汇报并与其他巡逻队通信。由于这些事情的发

[安防电子]

一种基于FPGA的RFID无线通信系统的实现

随着计算机技术的迅速发展,电子信息技术越来越快地普及到各行各业的应用中去。传统的物流信息采集工作方式是通过工作人员将票物进行核对,然后将票上的数据输入到计算机中。这一过程费时费力,并且可能由于各种人为过失造成各种各样错误数据的存在,影响所采集信息的可靠性。而自动识别技术利用计算机进行自动识别,增加了输入的灵活性与准确性,使人们摆脱繁杂的统计识别工作,并且大大提高了物流信息采集的工作效率。目前,由沃尔玛、麦德隆等大超市一手推动的RFID应用,为零售业带来包括降低劳动力成本、商品的可视度提高,降低因商品断货造成的损失,减少商品偷窃现象等好处。其可应用的过程包括:商品的销售数据实时统计,补货,防盗等。本文利用RFID技术,用FPGA

[嵌入式]

基于多种EDA工具的FPGA设计

摘要: 介绍了利用多种EDA工具进行FPGA设计的实现原理及方法,其中包括设计输入、综合、功能仿真、实现、时序仿真、配置下载等具体内容。并以实际操作介绍了整个FPGA的设计流程。

关键词: FPGA 仿真 综合 EDA

在数字系统设计的今天,片上系统(SoC)技术的出现已经在设计领域引起深刻变革。为适应产品尽快上市的要求,设计者必须合理选择各EDA厂家提供的加速设计的工具软件,以使其产品在本领域良性发展。FPGA设计是当前数字系统设计领域中的重要方式之一。本文以多种EDA厂家工具为基础,系统介绍FPGA设计的流程。

1 数字逻辑划分与FPGA内部结构

图1所示为数字逻辑权状分类图,由其可

[半导体设计/制造]

CEVA 和FLEX LOGIX宣布成功推出首款具有嵌入式 FPGA 的 DSP 芯片

CEVA 和FLEX LOGIX宣布成功推出首款具有嵌入式 FPGA 的 DSP 芯片以支持灵活/可更改的指令集架构 Flex Logix® EFLX嵌入式 FPGA 为 CEVA-X2 DSP 指令扩展实现可重构计算功能,以支持要求严苛且不断变化的工作负载 可重构计算解决方案、架构和软件的领先供应商Flex Logix Technologies, Inc.与全球领先的无线连接和智能传感技术及集成IP解决方案的授权许可厂商CEVA, Inc.(纳斯达克股票代码:CEVA)宣布成功推出世界上第一个集成CEVA-X2 DSP指令扩展接口的 Flex Logix EFLX® 嵌入式FPGA (eFPGA)芯片

[嵌入式]

![]() ,c为电磁波传播速度。

,c为电磁波传播速度。![]() 需要用循环卷积代替自相关函数来计算扩频测距系统中的码片偏移,可以节省运算时间(大约为1/114),加快捕获过程。设x(n),y(n)分别为现有发射PN码与反射回来的PN码,序列长度为N,对它们分别做N点FFT,记

需要用循环卷积代替自相关函数来计算扩频测距系统中的码片偏移,可以节省运算时间(大约为1/114),加快捕获过程。设x(n),y(n)分别为现有发射PN码与反射回来的PN码,序列长度为N,对它们分别做N点FFT,记

[page]

[page]

[page]

[page]

汽车电子的革新与FPGA-24页

汽车电子的革新与FPGA-24页

京公网安备 11010802033920号

京公网安备 11010802033920号