前言

随着科技的发展,信号处理系统不仅要求多功能、高性能,而且要求信号处理系统的开发、生产周期短,可编程式专用处理器无疑是实现此目的的最好途径。可编程专用处理器可分为松耦合式(协处理器方式,即MCU+协处理器)和紧耦合式(专用指令方式,即ASIP),前者较后者易于实现,应用较广。本文就是介绍一款松耦合式可编程专用复杂SoC设计实现,选用LEON3处理器作为MCU,Speed处理器作为CoProcessor。

LEON3及Speed

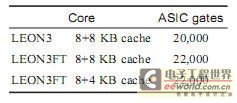

LEON3是由欧洲航天总局旗下的Gaisler Research开发、维护,目的是摆脱欧空局对美国航天级处理器的依赖。目前LEON3有三个版本(如表1),其中LEON3FT(LEON3 Fault-tolerant)只有欧空局内部成员可以使用。LEON3 (basic version)是遵循GNC GPL License的开源处理器,和SPARC V8兼容,采用7级Pipeline,硬件实现乘法、除法和乘累加功能,详细特性请参考相关技术文档[1]。

表1 LEON3的不同版本

目前,LEON3处理器因为开源、高性能、采用AMBA总线易扩展及软件工具完备等因素,在国内外大学(如UCB、UCLA、Princeton University等)及科研院所的科研活动中得到广泛应用。

Speed(又名GA3816)是一款我国自主研发、处于同时代国际先进水平、可重构、可扩展的面向FFT、IFFT、FIR及匹配滤波应用的信号处理器,其内部结构如图1所示,具有以下特点[2~4]:

1)Speed在追求运算速度的同时兼顾通用性,通过设置64位控制字,器件内部资源可根据不同应用进行重组;

2)可以实现FFT、IFFT、FFT-IFFT、FIR、滑窗卷积等运算,峰值运算能力达256亿次浮点乘累加/秒;3)由160个实数浮点乘法累加运算器组成40个复数乘法累加器阵列,1Mbit的双口SRAM,8个512×32bit系数ROM,两个直角到极坐标转换电路,两个对数变换电路及其它辅助电路和控制电路。

图1 Speed的内部模块结构

Speed传统的工作方式是通过片外FPGA输入控制信号和待处理数据,这不仅增大了PCB板级布线、调试的工作量,而且FPGA不能用C等高级语言编程,算法改动起来不灵活。另一方面,随着半导体工艺、微电子技术的发展,大规模的复杂SoC实现技术逐渐成熟,因此有必要将板级FPGA + Speed改进为芯片级MCU + Speed,这样既能实现真正的可编程增大灵活性,又能加快用户开发信号处理系统的速度。利用AHB实现通信

为了实现可编程,需要将C/C++程序表达的信息经过编译器、LEON3处理器、AHB总线、DMA控制器和必要的HDL代码,转化成Speed能够识别的信息,进入Speed模块中,如图2。其中AHB总线是LEON3 Core和Speed Core结合的关键。

图2 实现软件可编程的过程

AHB总线及AHB控制器

AMBA总线是一种应用广泛的层次化总线结构,有高速的AHB和低速APB之分,其中AHB是一种流水式高速总线结构,地址和数据总线相互独立,可挂载16个Master和Slaver设备,常用来组织和连接高性能模块,如处理器、DMA控制器、协处理器等[5~7]。AHB总线的核心是AHB控制器,主要包括仲裁器,译码器和多路复用器,其中仲裁器选择AHB Master,而译码器选择AHB Slave,实现写数据WDATA和读数据RDATA分开,如图3所示。

DMA控制器

DMA是指设备直接对计算机存储器进行读写操作的方式。这种方式下数据的读写无需CPU执行指令,也不经过CPU内部寄存器,而是利用系统的数据总线直接在源地址和目的地址之间传送数据,达到极高的传输速率。DMA控制器一方面可以接管总线,即可以像CPU一样视为总线的主设备,这是DMA与其它外设最根本的区别;另一方面,作为一个I/O器件,其DMA控制功能正式通过初始化编程来设置。当CPU对其写入或读出时,它又和其它的外设一样成为总线的从属设备。本文中为了实现DMA和AHB密切配合,即启动DMA后大量原始数据通过AHB总线从数据存储器进入Speed模块,需要DMA控制器内部包含AHB Master模块,如图4所示。另外需要说明的是,LEON3为了实现AHB上设备的plug&play需要在0xFFFFF000-0xFFFFF800地址空间添加设备信息[8~9],所以DMA 控制器和Speed协处理器亦要如此,以便LEON3的软硬件协调一致。在C语言实现DMA时,向DMA的控制寄存器写入相应的信息,即可启动DMA传输,如图5所示。

图4 DMA与AHB Master的关系

关键字:LEON3 SoC

引用地址:

基于LEON3处理器和Speed协处理器的复杂SoC设计实现

推荐阅读最新更新时间:2024-05-02 21:28

百度采用Marvell的ARM架构服务器SoC

百度拥有世界上第一个采用ARM架构服务器的大数据中心。这位中国搜索引擎的龙头老大将会采用Marvell的32位Marvell Armada XP SoC。 这标志着ARM服务器SoC迈出了X86芯片主导市场的第一步。ARM家族标榜着低功耗和高能效。 很多观察者表示,目前的Marvell提供的拥有Calxeda技术的32位芯片的市场机遇还很有限,因为很多软件都是基于64位编码的。AMD、Applied Micro, Cavium, Nvidia, 三星和高通等多达9家的企业正在考虑赶在2014年能够出货64位的ARM 服务器SoC. Marvell也开发了一系列的遵循IPMI2.0标准的服务器管理软件。据称,这套系统将比X86

[半导体设计/制造]

NXP推出Wi-Fi 6E三频段SOC,充分释放6GHz频谱潜力

恩智浦半导体宣布推出全新的CW641 Wi-Fi 6E三频段片上系统(SoC),为可在6GHz频段运行的新一代Wi-Fi 6设备奠定基础。鉴于传统2.4GHz和5GHz频段的拥堵程度不断加剧,美国FCC以及世界其他地区批准了用于6GHz频段的1.2GHz未授权频谱,这将为Wi-Fi格局带来巨大转变。恩智浦推出了一款全新的Wi-Fi 6E设备,旨在充分利用这一6GHz频段,并通过提高吞吐量、容量、可靠性和降低延迟来扩展Wi-Fi容量。 CW641专为接入点和服务提供商网关而设计,可在全新的6GHz频段提供超过4Gbps的速度和多用户性能,提高容量和降低延迟,从而显著改善Wi-Fi用户体验。通过在网关平台上添加6GHz功能,

[嵌入式]

基于SOC单片机的pH值检测与控制

0 引言 随着科技的进步和工农业生产的发展,水产养殖这一传统的行业也在向工厂化和智能化方向发展。水质监控仪器的设计是实现工厂化水产养殖的关键设备。其中pH 值就是多因子水环境中一个重要的因子,本文设计了基于SOC 单片机C8051F020 的pH 值的检测电路,并通过控制算法实现了对多因子水环境中pH 值的控制调节。 1 硬件电路设计和pH 测量原理 本设计采用高速SOC 单片机C8051F020 既能提高仪表可靠性又能提高系统性能。C8051F020是集成的混合信号片上系统,具有与MCS-51内核及指令集完全兼容的微控制器,除了具有标准8051 的数字外设部件之外,片内还集成了数据采集和控制系统中常用的模拟

[单片机]

MIPS首家授权培训中心登陆上海,不让ARM独美!

工业标准处理器架构与内核供应商MIPS科技日前宣布,已指定位于上海的双实科技公司作为其中国首家MIPS授权培训中心。自4月份开始,双实科技将提供关于系统级芯片(SoC)和板级系统(SoB)的专业培训。培训使用业界标准的MIPS架构及低成本的MIPS-Based开发板,培训对象为中国的职业工程师和研究生。 MIPS科技与双实科技还将共同举办一系列特别针对中国市场的技术研讨会。首届研讨会将于3月16日-17日在上海浦东软件园举行,将介绍MIPS科技的公司发展和动向、基础架构和内核及目标市场。介绍讲座对所有听众免费。研讨会的听众将包括IC设计者、嵌入式系统工程师和电子工程与计算机系(EECS)教师。其他研讨会计划在北京和深圳举行。有关

[嵌入式]

葡萄科技的PaiBand手环采用Nordic Semiconductor的nRF51822 SoC

挪威奥斯陆 – 2016年12月2日 – Nordic Semiconductor宣布,位于上海的科技公司葡萄科技的新型PaiBand儿童成长手环选择Nordic多次获奖的nRF51822低功耗蓝牙(Bluetooth® low energy,前称为蓝牙智能)系统级芯片(SoC)。 与设计用于防止儿童走失或防止与父母走散的其它儿童可穿戴产品不同,PaiBand关注的是儿童成长,强调的是运动和健康,并能够为父母提供反馈,帮助他们更好地了解孩子的健康和成长状况。戴在手腕上的PaiBand监测活动、心率和睡眠,通过Nordic的nRF51822 SoC低功耗蓝牙解决方案将数据自动无线同步到蓝牙4.0(及之后版本)智能手机和平板电脑上

[物联网]

Nordic 在低功耗蜂窝物联网SoC中部署使用CEVA DSP IP

高度集成的nRF91 SoC集成CEVA内核支持多模LTE-M / NB-IoT通信 CEVA,全球领先的智能和互联设备的信号处理平台和人工智能处理器IP授权许可厂商 (纳斯达克股票交易所代码:CEVA), 宣布Nordic Semiconductor已经获得授权许可,在其nRF91®系统级芯片(SoC)中部署使用CEVA DSP技术以实现低功耗蜂窝物联网连接。这个多模LTE-M/NB-IoT SoC通过位于核心的CEVA DSP来确保实现所需的超低功耗和高效性能以满足多种蜂窝物联网用例,包括可穿戴设备、资产跟踪器、智慧城市、智能计量和工业物联网。nRF91 SoC构成了Nordic的nRF91低功耗蜂窝物联网系统级封装(Si

[网络通信]

联发科 SoC 跑分造假?现在的跑分还能信吗?官方这样说

现在的手机跑分,真的是不能信。 手机产商、芯片厂商越来越追求芯片的跑分数值,Benchmark (基准性能测试)逐渐成为衡量设备性能的重要标准。 但在一味追求分值的同时,厂商们也逐渐深陷“分值禁锢”之中,近期的联发科,就是如此。 联发科芯片 benchmark 造假 事情的开始,要从 OPPO Reno3 说起。 外媒 Anandtech 发现,搭载 P95 CPU 的欧洲版 OPPO Reno3 Pro 的跑分数值比搭载性能更强大的最新 Dimensity 1000L CPU 的国行版 Reno3 的高,这引起了 Anandtech 的质疑。 由此,Anandtech 分别使用匿名版(可帮助分值作弊)和常

[手机便携]

Atmosic SoC显著提高TraceSafe AllSafe腕带续航时间

Atmosic Technologies和TraceSafe宣布,TraceSafe已经为AllSafe腕带选择了Atmosic的M2解决方案。Atmosic称,M2片上系统(SoC)具有低功耗,可延长安全腕带的电池寿命,还支持远程连接,以支持连接到远程网关。 当企业和娱乐设施重新开放之后,会有大量人员聚集,然而时至今日,COVID-19仍然对健康构成威胁,因此需要追踪设备和执行通知系统。TraceSafe正通过其端到端、设备到云的解决方案将其AllSafe设备和系统带到这些场景中。 TraceSafe与Atmosic合作,将基于蓝牙5.0的M2解决方案集成到每个腕带中,以实现设备到设备的连接,从而实现追踪人员功能。

[物联网]

电动汽车SOC估算方法

电动汽车SOC估算方法 Verilog HDL数字集成电路设计原理与应用

Verilog HDL数字集成电路设计原理与应用

京公网安备 11010802033920号

京公网安备 11010802033920号