摘要:本文用FPGA 设计 LED显示屏接收控制系统,着重研究系统硬件设计方案,进一步解决了 LED大屏幕数据的灰度控制、外扩存储器的性能要求及实现方式。用 QuartusII 软件开发各个模块, QuartusII 软件提供的人性化的界面操作,很多模块都可以在系统内直接实现, 方便实用。

LED屏早在60年代就已出现,但直到 90年代中期,才出现了全彩屏,该技术近年的价格已有了很大的降幅,分辨率也有了很大的改善。对于视频来说,LED屏的低分辨率表现性能良好。平常看到 LED屏的分辨率与电脑显示器的分辨率是差不多的。LED 彩色显示大屏是室外显示大屏中用的最多的,是公认的室外大型显示屏中最值得发展的产业,LED 屏以其高亮度、长使用寿命更胜一筹。与 LCD 相比,LED屏播放视频时的响应速度更快,亮度更高。与电子发射显示器相比,LED制造更简单。与 OLED相比,LED技术更成熟。总之,LED 显示以其得天独厚的优势占据了高分辨率视频显示市场。本文设计的基于FPGA的大屏幕LED点阵显示系统处理数据更快、存储量更大。 一、接收卡控制系统的总体方案设计

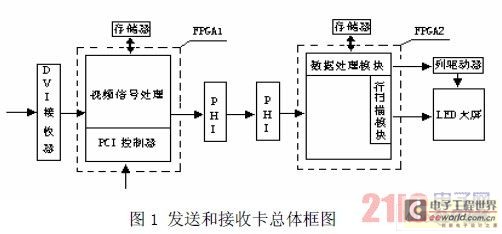

如图 1所示,视频数据通过 DVI 接口传给 FPGA1,进行分辨率的切换和显示区域的选择以及信号的反伽码矫正,通过网络传输给接收卡的 FPGA2,通过 FPGA2 进行数据的缓存,灰度控制以及行扫描和列驱动功能。

接收卡接收的是 DVI 传给 FPGA1,经 FPGA1 处理后的数据。在 FPGA2 内部还要进 行数据处理,处理要达到的目标:(1)数据能在 LED 屏幕上分区显示;(2)256 灰度级屏幕大小:256*800。

(一)灰度实现方案的选择

采用专用驱动芯片 BHL2000来控制 LED显示点阵,其内部自动有灰度控制电路。

BHL2000是一块专门用于 LED 扫描和驱动的高性能室外屏室内屏通用的专用集成电路。BHL2000 芯片对 LED 点阵的灰度采用占空比的调制方式并接受 8 位并行灰度脉宽宽度与灰度数据值成正比,图像数据存储容量为 32*16*8 比特,数据输入扫描与数据输出扫描独立,控制系统结构简单。

专用芯片与通用芯片相比有它独特的特点,专用驱动芯片内部有SRAM,输出时恒流控制。LED 显示效果更好,灰度实现简单,容易控制,为以后的扩展使用打下良好的基础。

(二)存储器方案设计

存储器实现方案有六种:(1)FIFO 实现;(2)双口 RAM 实现;(3)SDRAM 实现(4)SRAM 实现;(5)FLASHROM 实现(6)FPGA 内部开存储器来实现。

根据 LED 显示屏所要实现的 800*256分辨率的指标,还有灰度级控制方式,选用 SRAM来实现接收数据的缓存。因为其容量大,速度快,地址方便控制,可以进行跳地址读写数据,方便数据分区取出。[page]

二、接收卡控制系统单元模块设计

(一)时钟控制模块

1. 行计数时钟和扫描控制信号

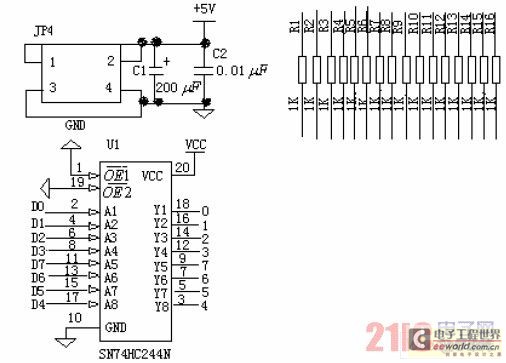

采用行扫描的,必须产生行扫描控制信号。如图 2所示的row[4..0]是行扫描控制信号,用它接一个 2-4 译码器和四个 3-8 译码器来产生 32个行选信号,构成 1/32 扫描方式的显示屏。Hclk为行计数时钟,也可以称为行锁存时钟。

图2 行驱动模块原理图[page]

2. 移位时钟模块

移位时钟CP信号的产生,根据屏幕分辨率 256*800,刷新频率为60HZ,扫描方式为 1/32,则移位频率为 32*800*60=1.5MHZ。其中 32为扫描方式,32行共用一列驱动模块。60为刷新频率,所以移位时钟 CP 用时钟分频电路来实现即可。

3. 灰度控制时钟

由于采用 BHL2000专用驱动芯片,其灰度控制时钟是通过计算由 FPGA产生的。根 据32*32 的点阵,其刷新频率为 60HZ 则点频为 60*32*32=60KHZ ,其行频为点频 /32=2KHZ ,所以灰度控制时钟频率为256*2k=512KHZ。

(二)存储器控制模块

根据 LED显示屏的大小,可以确定存储器的容量和读写速度,存储采用分色顺序方式存储。存储最少存一帧的数据,容量为 256*800=200KB,选六片容量为256K的SRAM 即可。由于调试时选用的是32*32的点阵屏,不需要这么大的容量,只是在 FPGA 内部实现了SRAM,为了方便看 LED显示的结果,就在 FPGA 实现了ROM,里面固定的存储了一些信息,证明 LED的显示是否和ROM 里的内容一样。

(三)显示屏的驱动单元

1. 行驱动模块 三、FPGA 开发流程

系统程序设计是采用的 Verilog语言输入方式,设计所用的软件为 QuartusII软件。

Altera 公司的 QuartusII 设计软件提供最全面的 FPGA, CPLD 和结构化 ASIC 设计流程,结合多种可直接进行设计应用的知识产权(IP)内核,可以使设计效率 有很大提高。该软件提供完整的多平台设计环境,拥有 FPGA 和 CPLD 设计的所有 阶段的解决方案,可以很好的满足特定设计的需要。

本文作者创新点:大屏幕 LED点阵显示系统采用可编程逻辑器件 FPGA来实现,可以实现在系统可编程(ISP),用户可以在自己设计的目标系统中或电路板上重构逻辑器件编程或反复改写,从而实现了硬件设计与修改软件化,缩短了开发周期,经济效益明显,增加了设计灵活性,使得整个系统的性能得以进一步提高。

上一篇:基于FPGA的单片机外围接口电路设计

下一篇:FPGA在洗片机控制系统中的应用

推荐阅读最新更新时间:2024-05-02 22:19

汽车电子的革新与FPGA-24页

汽车电子的革新与FPGA-24页 Verilog HDL数字集成电路设计原理与应用

Verilog HDL数字集成电路设计原理与应用

京公网安备 11010802033920号

京公网安备 11010802033920号