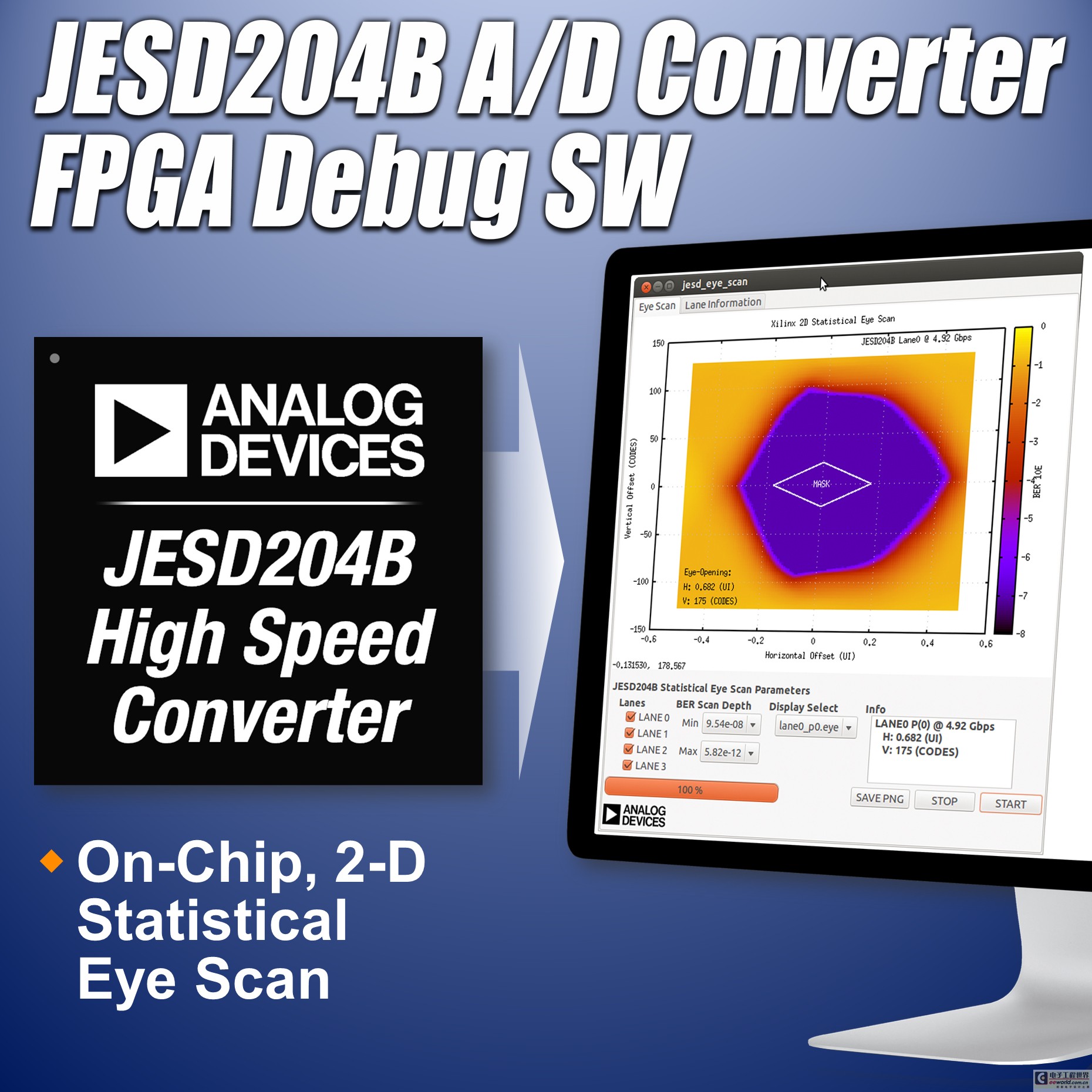

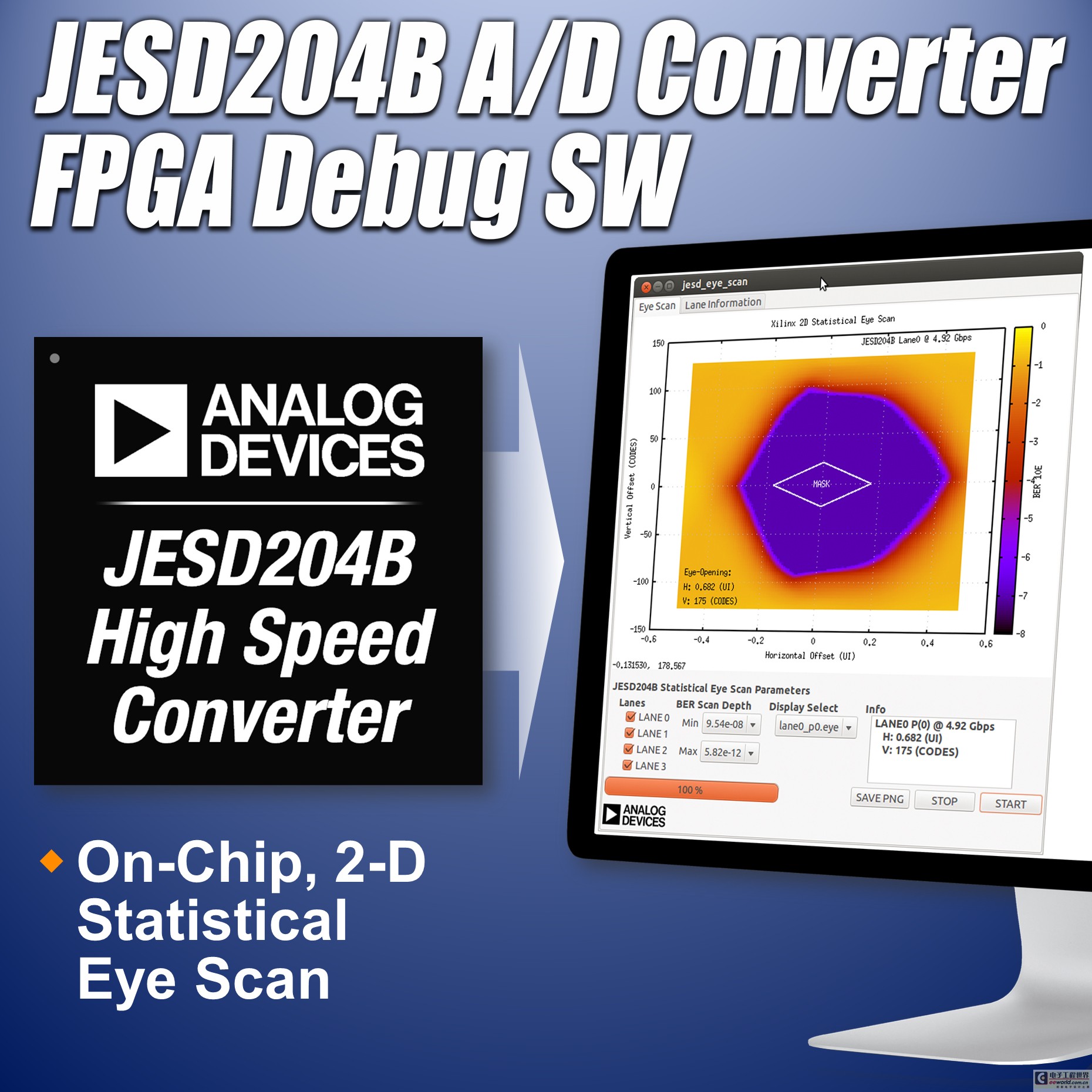

Analog Devices, Inc. (NASDAQ:ADI),全球领先的高性能信号处理解决方案供应商,今天发布了一款基于FPGA的参考设计及配套软件和HDL代码,该参考设计可降低集成JESD204B兼容转换器的高速系统的设计风险。该软件为JESD204B Xilinx收发器调试工具,可支持312.5Mbps至12.5Gbps的JESD204B数据转换器至FPGA串行数据接口和Xilinx® Inc., 7系列FPGA及Zynq®-7000全可编程SoC。它随ADI转换器免费提供,通过提供片内二维统计眼图扫描,帮助雷达阵列、软件定义无线电以及其他高速系统的设计人员更快地验证采用千兆收发器的JESD204B数据转换器至FPGA设计的信号完整性。

Analog Devices, Inc. (NASDAQ:ADI),全球领先的高性能信号处理解决方案供应商,今天发布了一款基于FPGA的参考设计及配套软件和HDL代码,该参考设计可降低集成JESD204B兼容转换器的高速系统的设计风险。该软件为JESD204B Xilinx收发器调试工具,可支持312.5Mbps至12.5Gbps的JESD204B数据转换器至FPGA串行数据接口和Xilinx® Inc., 7系列FPGA及Zynq®-7000全可编程SoC。它随ADI转换器免费提供,通过提供片内二维统计眼图扫描,帮助雷达阵列、软件定义无线电以及其他高速系统的设计人员更快地验证采用千兆收发器的JESD204B数据转换器至FPGA设计的信号完整性。

• 下载参考设计:http://www.em.avnet.com/en-us/design/drc/Pages/Analog-Devices-Linux-JESD204B-Eyescan-Software.aspx

• 观看关于JESD204B模数转换器、FPGA和眼图扫描原理图的视频:http://videos.analog.com/video/products/analog-to-digital-converters/2534598195001/High-Speed-ADC-FMC-Development-Board-with-JESD204B/

• 了解有关Xilinx FPGA的更多信息:www.xilinx.com/jesd204

• 通过中文技术论坛EngineerZone™联系工程师和ADI产品专家:http://ezchina.analog.com/community/data-converters

• 更多有关产品信息,请致电亚洲技术支持中心:400 6100 006, 或发送邮件至 china.support@analog.com , 也可点击ADI官方微博http://weibo.com/analogdevices ,或通过手机登录m. analog.com 或 www.analog.com了解最新产品等信息。

• 更多ADI产品及应用视频,请访问:http://videos.analog.com/category/chinese/

Xilinx高速I/O产品经理Revathi Narayanan表示:“ADI的JESD204B Xilinx收发器调试工具提供了片内眼图扫描功能,能以统计手段确定FPGA内部信号的完整性,是测试和测量流程的有效补充。其他技术均针对FPGA封装的外部,并在Xilinx自动增益控制和均衡器模块处理之前采集信号,而ADI则利用Xilinx收发器片内眼图扫描功能,使开发人员可以监控FPGA内部JESD204B链路上的信号完整性和设计裕量,从而获得更加准确的结果。”

ADI的参考设计直接从7系列IBERT内核中的片内Rx裕量分析功能收集数据,并在FPGA或者ARM®双核Cortex™-A9 MPCore™处理器之一的内部管理本地数据,在HDMI显示器上显示数据,或者通过以太网将数据送至远程监控站。一般地,其他扫描工具在片外测量信号,需要使用昂贵的测试和测量设备,或者需要通过JTAG传回数据,以便在实验室的主机/开发电脑上查看。

“实时”数据采集功能可监控设备健康状态

替代型扫描工具一般通过生成伪随机位流(PRBS)的方式来测量高速数据链路,而系统会在封闭开发环境中校验该伪随机位流的位级正确性。这种方式并不描述设计的实际表现,也不说明设计是否可能濒临失败。ADI的参考设计使用流向FPGA的真实JESD204B串行数据来测量链路的稳健性。通过这种利用“实时”数据的方式,即使已在现场部署设计之后,也可监控信号的保真度,从而在产品的寿命周期内进行实时、预见性维护。

关键字:调试软件 ADI FPGA

引用地址:

JESD204B FPGA调试软件加快高速设计速度

推荐阅读最新更新时间:2024-05-02 22:48

基于FPGA的卷积码的编/译码器设计

卷积码是Elias在1955年最早提出的,稍后,Wozencraft在1957年提出了一种有效译码方法,即序列译码。Massey在1963年提出了一种性能稍差,但比较实用的门限译码方法,由于这一实用性进展使卷积码从理论走向实用。而后Viterbi在1967年提出了最大似然译码法,该方法对存储器级数较小卷积码的译码很容易实现,并具有效率高、速度快、译码器简单等特点,人们后来称其为维特比算法或维特比译码,广泛应用于现代通信中。本文主要论述了基于Xilinx公司的FPGA的卷积编码器及相应的维特比译码器的研究,并在幸存路径存储与译码输出判决方面提出了改进算法,从而使译码器结构得到简化。 1 卷积码的编码原理与实现 卷积

[嵌入式]

FPGA工程师应如何挑选ADC和DAC

将具有信号处理功能的FPGA与现实世界相连接,需要使用模数转换器(ADC)或数模转换器(DAC) 一旦执行特定任务,FPGA系统必须与现实世界相连接,而所有工程师都知道现实世界是以模拟信号而非数字信号运转的。这意味着需要在模拟信号域与数字信号域之间进行转换。针对手头工作选择恰当的FPGA时,用户面临着林林总总的选择,在为系统选择正确的ADC或DAC时也是如此,玲琅满目。

选择时首先要确定转换信号所需的采样频率。这个参数不仅将影响转换器的选择,同时也会影响对FPGA的选择,这样才能确保器件能够满足所需的处理速度及逻辑封装要求。转换器的采样频率至少为信号采样频率的2倍。因此,如果信号的采样频率为50MHz,则转换器采样频率至少

[电源管理]

ARM在线升级FPGA程序方法(逆向工程)

为什么写该文 公司有款产品采用FPGA做处理器,需要 远程升级 不使用烧写器,通过网络对其升级。领导提议既然程序是存储在外部存储器上的,那么能否通过EPCS4与ARM SPI 总线通信连接刷新FPGA程序呢?于是就有了下文的实践。 要实现该功能有几种方式: 1. 解析编译出的FPGA下载文件jic、pof,将解析后的内容烧录到EPCS4中。但是否这两种文件格式公开存储结构呢?芯片厂商是否对此保密? 2. 直接读取EPCS4的程序,烧录到另一块EPCS4中。但是否读取的EPCS4内容以及根据FPGA序列号做了加密呢? 权衡任务安排时间,选择第二种方案,毕竟就算第一种方案可行,也需要设计第二方案的读写操作。 可喜

[单片机]

基于热敏电阻的温度检测系统(上篇):设计挑战和电路配置

简介 本系列文章分为上下两篇。上篇首先讨论基于热敏电阻的温度测量系统的历史和设计挑战,以及它与基于电阻温度检测器(RTD)的温度测量系统的比较。文中还会简要介绍热敏电阻选择、配置权衡,以及Σ-Δ型模数转换器(ADC)在该应用领域中的重要作用。下篇将详细介绍如何优化和评估基于热敏电阻的最终测量系统。 热敏电阻与RTD 正如文章“如何选择并设计理想RTD温度检测系统”中所讨论的,RTD是一种电阻值随温度变化的电阻器。热敏电阻的工作方式与RTD类似。RTD仅有正温度系数,热敏电阻则不同,既可以有正温度系数,也可以有负温度系数。负温度系数(NTC)热敏电阻的阻值会随着温度升高而减小,而正温度系数(PTC)热敏电阻的阻值会随着

[模拟电子]

ADI公司数模转换器改善电视观赏体验

中国,北京 Analog Devices, Inc.(ADI),全球领先的高性能信号处理应用半导体解决方案供应商,近日推出一款数模转换器AD9162,它能把未来的电视体验带给当今的家庭观众,支持观众在更多频道上以史无前例的传输和下载速度享受超高清(UHD)和4K电视。新型数模转换器AD9162代表着一次行业突破,可为宽带和无线服务运营商提供业界最高的带宽和动态范围,无需高成本的大规模架构或转换器设计变更便可满足消费者不断增长的高质量、不间断数据和视频流需求。 ADI公司数模转换器改善电视观赏体验 16位、12 GSPS AD9162转换器具有同类最佳的2.5 GHz带宽,超过有线电视行业DOCSIS 3.1标准规定的1.7

[模拟电子]

基于FPGA和MCU的CAN-VME总线转换设计

为了扩展VME总线和CAN总线的应用范围,充分利用两种总线的不同传输特点,采用了模块设计方法,提出一种基于FPGA和MCU的总线转换方案。该方案给出了FPGA与上位VME总线部分的VME总线接口设计,利用MCU控制CPLD扩展的多通道CAN节点完成CAN总线部分的设计,还给出软件实现上的重点、难点和流程。实现了两种不同总线的转换,满足了工业环境对两种总线混合使用的要求。 CAN(Controller Area Network控制器局域网)以其高性能、高可靠性以及独特的设计等优点,为分布式控制系统实现各节点之间实时、可靠的数据通信提供了强有力的支持。CAN总线突出的可靠性、实时性和灵活性显示了它突出的优势,成为公认的最有前途的总线

[单片机]

面向高效、快速瞬态响应的汽车和工业用品的直通升压控制

简介 升压电源拓扑结构在汽车和工业电子领域越来越受欢迎。许多系统都需要稳定的输入轨,其上游电源输入轨电压可能会有显著变化。升压变换器可用于显著提高应用的通用性。利用升压变换器,可以将新的电子设备无缝连接至任何供电轨,且无需重新设计前端或使用多个版本来覆盖各种供电场景。升压控制器还支持对输入电压下降具有高度抑制性的电子器件。这主要与汽车电子设备相关,因为汽车电子设备的供电轨电压在低温启动期间会明显下降。 LTC7804可简化升压变换器的设计,同时不会对其先进的性能产生不利影响。LTC7804的主要特性为:低静态电流、单输出同步整流、高达40 V的宽输入电压范围(输出电压可达36 V)、展频(SSFM)以及适用于高效、低电磁

[电源管理]

一种并行存储器系统的FPGA实现

摘 要: 介绍一种可在现代小卫星上应用的高(低)位交叉并行存储系统,并给出了该存储系统控制器的FPGA实现。该系统的应用将极大地增强星上计算机的数据通信和图象处理的能力,并提高整个系统的可靠性。

关键词: 现代小卫星 星载计算机 并行存储系统 FPGA 硬件描述语言

现代小卫星,通常指80年代以后发展起来的小卫星。它建立在微电子技术,计算机(包括软件)、微型光学和机械、轻型复合材料及高精机械加工的基础上,是航天高技术发展的产物。虽然现代小卫星的体积和重量很小,成本和风险都很低,但由于选用了高新技术,整个小卫星的容量和性能,即小卫星的功能密度是很高的。而且小卫星组成星座可拓宽全新的应用领

[应用]

Analog Devices, Inc. (NASDAQ:ADI),全球领先的高性能信号处理解决方案供应商,今天发布了一款基于FPGA的参考设计及配套软件和HDL代码,该参考设计可降低集成JESD204B兼容转换器的高速系统的设计风险。该软件为JESD204B Xilinx收发器调试工具,可支持312.5Mbps至12.5Gbps的JESD204B数据转换器至FPGA串行数据接口和Xilinx® Inc., 7系列FPGA及Zynq®-7000全可编程SoC。它随ADI转换器免费提供,通过提供片内二维统计眼图扫描,帮助雷达阵列、软件定义无线电以及其他高速系统的设计人员更快地验证采用千兆收发器的JESD204B数据转换器至FPGA设计的信号完整性。

Analog Devices, Inc. (NASDAQ:ADI),全球领先的高性能信号处理解决方案供应商,今天发布了一款基于FPGA的参考设计及配套软件和HDL代码,该参考设计可降低集成JESD204B兼容转换器的高速系统的设计风险。该软件为JESD204B Xilinx收发器调试工具,可支持312.5Mbps至12.5Gbps的JESD204B数据转换器至FPGA串行数据接口和Xilinx® Inc., 7系列FPGA及Zynq®-7000全可编程SoC。它随ADI转换器免费提供,通过提供片内二维统计眼图扫描,帮助雷达阵列、软件定义无线电以及其他高速系统的设计人员更快地验证采用千兆收发器的JESD204B数据转换器至FPGA设计的信号完整性。

汽车电子的革新与FPGA-24页

汽车电子的革新与FPGA-24页 控制系统计算机辅助设计 — MATLAB语言与应用

控制系统计算机辅助设计 — MATLAB语言与应用

京公网安备 11010802033920号

京公网安备 11010802033920号