物联网跨越多个应用领域,根据最终应用领域的不同,设计团队的要求可能会大相径庭。功率,性能和成本是芯片设计的优先事项,而汽车和航空航天/国防等应用领域则还需要考虑功能安全性,在其他领域,信息安全性是关键或现场可升级性的需求。

验证,原型设计和软件开发是这些领域和设计要求中的共同点。为了允许进行嵌入式软件开发,通常认为早期的验证技术太慢,而使用虚拟平台(例如QEMU)进行的抽象有时不够准确。

长期以来,基于FPGA的原型设计一直是芯片诞生前软件开发的首选平台。以Cadence Palladium Z1企业仿真平台之类的工具中的硬件仿真相类似,它可以将执行性能从MHz级别扩展到100 MHz,而且成本更低,从而可以将其交给软件团队的更多开发人员。

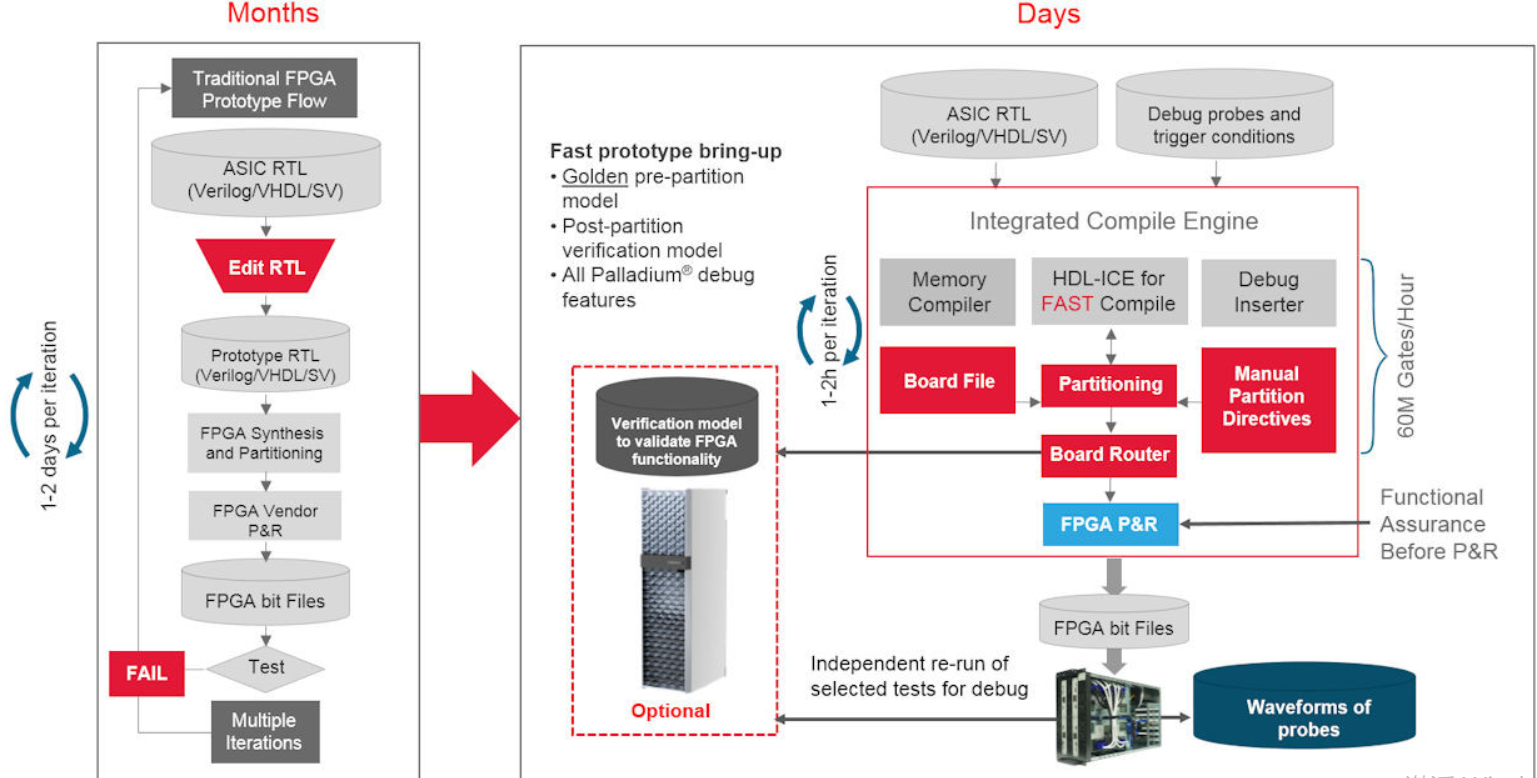

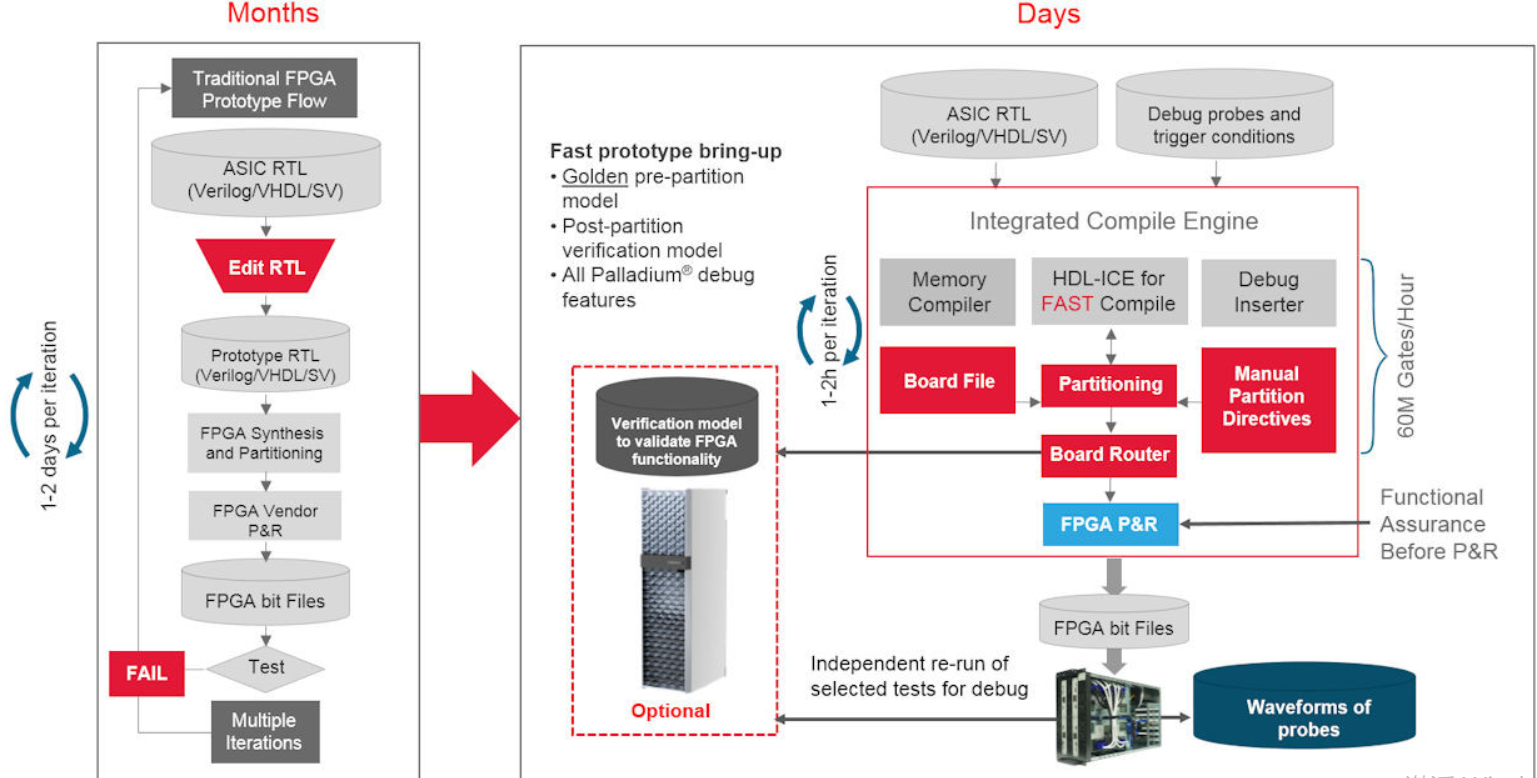

传统上,基于FPGA的原型的障碍一直是其启动过程,有时要花几个月的时间才能将其提供给软件开发人员。原因是需要将ASIC设计从其实际的芯片重新映射到FPGA提供的结构中,这需要重新映射设计的各个部分。

原型验证流程

对于初学者来说,ASIC中的存储器需要映射到FPGA中可用的资源,或者映射到拥有特定附加存储器(例如DDR)的子卡。处理ASIC的时钟可能是一场噩梦,在PCB和FPGA上更复杂的设计中要同步10多个时钟。跨多个FPGA进行设计划分并非易事,通常需要使用低压差分信号(LVDS)技术在同一引脚上复用多个信号。

传统上,规模较大的公司都有原型开发团队,专门研究设计团队正在开发的RTL版本并将其映射到FPGA中。但是,随着设计复杂性的提高,执行上述所有任务变得越来越困难。

借助基于Protium S1 FPGA的原型验证平台,Cadence重新开发了原型验证流程,并专注于将原型制作时间从数月缩短至数周甚至数天。通过实现Palladium Z1仿真与基于FPGA的Protium S1 FPGA原型之间的一致性,以及将某些前端仿真重新用于原型。

复杂的手动内存建模已使用仿真中已知的内存模型自动完成;编译流程负责FPGA之间的分区和时钟同步。可以在仿真中验证要映射到FPGA架构中的网表,从而节省宝贵的布局布线时间。在基于FPGA的原型中发现缺陷的速度比仿真快大约5倍,因此可以促进仿真更好的调试功能。

关键字:Cadence 原型验证

引用地址:

基于FPGA的Cadence Protium S1原型验证平台

推荐阅读最新更新时间:2024-11-19 23:23

Cadence放弃收购Mentor

经过几轮收购提议后,Cadence放弃了16亿美元收购Mentor的计划。 “Mentor与Cadence进行磋商合作失败,致使Cadence放弃了收购计划”,Cadence说。但是Mentor公司说Cadence最近发布的消息与两家公司之前的磋商是不一致的。 Mentor公司说:“Cadence在交易资金上存在问题”,除此之外,今天的联邦贸易委员会将第二轮收购议案予以推迟。 6月份,Cadence向Mentor董事会提议以每股16美元现金的方式收购Mentor,但是Mentor拒绝了这项提议。 Cadence发表声明称:Mentor进一步的拒绝收购议案。“对Mentor的股东来说这是个不幸的消息,但是

[焦点新闻]

S2C 日前宣布其Verification Module技术(专利申请中)已可用于其基于Xilinx的FPGA原型验证系统中。V6 T

莱迪思半导体公司近日宣布,随着针对电源管理的Power 2 You指南的出版和广泛地被采用,莱迪思将于2011年10月在全球举办Power 2 You系列研讨会。研讨会的内容为综合实践和技术介绍,结合基本的设计原则,先进的可编程电源和平台管理的概念,以及实际的电源和平台管理应用实例。 研讨会的议题将包括:

• 可靠的电压监测和复位产生 • 定序,监控和复位分配 • 整合了热插拔控制器与定序和监测 • 转换模拟DC- DC转换器至数字点负载(POL)稳压器 • 针对大电路板的电源管理和故障

莱迪思的电源和平台管理专家将亲临研讨会,研讨会是免费的,但需要预先登记。每个与会者将收到一份研讨会材料的副本,以及针对电源管理的P

[嵌入式]

Cadence落户南京市浦口区,成为继引进台积电后的又一龙头项目

11月13日,电子设计自动化(EDA)与半导体知识产权(IP)的领先供应商美国楷登电子( Cadence )与南京市浦口区人民政府正式签署战略合作备忘录以及投资协议。据悉, Cadence 项目是南京市浦口区继引进 台积电 之后在集成电路设计领域引进的又一个龙头性项目,历经两年的洽谈,在多方的共同努力下,今天终于签约落地。下面就随手机便携小编一起来了解一下相关内容吧。 南京市江北新区管委会常务副主任、浦口区区委书记瞿为民先生致辞表示,此次签约仪式标志着南京市浦口区与 Cadence 双方的战略投资进入实质性阶段。南京江北新区是江苏省唯一的国家级新区,浦口是江北新区的重要承载地,而集成电路已经成为我们重点培育的新兴技术

[手机便携]

Cadence推出新一代视觉/成像DSP内核Tensilica Vision P5

Cadence设计系统公司(NASDAQ: CDNS) 今天发布新一代Cadence Tensilica Vision P5数字信号处理器 (DSP),一款旗舰级的高性能视觉/成像DSP内核。相比上一代IVP-EP成像和视频DSP,新款成像和视觉DSP核在执行视觉任务时可实现高达13倍的性能提升和超过5倍的功耗降低。 Tensilica Vision P5 DSP为需要超高内存和并行运行的应用程序全新开发,支持要求高像素和高帧率的复杂视觉处理程序。它可用来卸载主CPU的视觉和成像功能,从而提升数据处理能力并降低功耗。因此,终端用户可以受益于这一理想的DSP功能,包括可增强图像和视频、立体声和3D成像、深度图处理、机器人

[半导体设计/制造]

Cadence与三星加速开发3纳米混合信号设计

楷登电子(美国 Cadence 公司,NASDAQ:CDNS)今日宣布,与 Samsung Foundry 合作开发已经验证的 Mixed-Signal OpenAccess 工艺设计开发包(PDK)技术文件,支持从 28FDS 到基于 GAA 的 3 纳米工艺等三星制程技术。 Mixed-Signal OpenAccess PDK 可以确保 Cadence® 的定制化工具和数字设计工具在三星工艺技术环境下无缝运行,帮助双方共同客户缩短产品上市时间。Mixed-Signal OpenAccess PDK 将提高数据中心、网络、5G、移动、工业及汽车应用混合信号设计的生产效率。 与面向三星工艺技术的 Mixed-Signal Ope

[手机便携]

EDA“病”了——将走向何处?

EDA“病”了。当业界最大EDA公司——Cadence出现了许多自身造成的问题时,整个EDA生态系统都病了。 我们曾经拥有一个健康的EDA世界。在过去,有很多EDA的新闻工作者;Gartner报道EDA信息;华尔街的大公司都会有分析师来做EDA资讯;很多投机资本家会为EDA初创公司投资;每个季度,都会有一个启动项目公布于世或是得到一个极具吸引力的估价。EDA使半导体设计得以民主化,并将其从大型半导体公司的腹地推向系统公司、初创公司和无晶圆厂设计公司。那时候,EDA产业的生活是美好的,整体产业的利润是可观的。 世界上高达3万亿美元的电子工业很大程度依赖于世界上4000亿美元的半导体工业,而半导体,却又依赖着一个

[焦点新闻]

Cadence携手Arm交付首个基于低功耗、高性能Arm服务器的SoC验证

系统公司和半导体公司现可在基于Arm的服务器上部署Cadence Xcelium 并行逻辑仿真平台。 楷登电子(美国Cadence 公司 NASDAQ:CDNS)今日与Arm联合发布基于Arm® 服务器的Xcelium™ 并行逻辑仿真平台,这是电子行业内首个低功耗高性能的仿真解决方案。 在芯片制造之前, SoC芯片功能正确性验证占用了整个项目70%的EDA软件使用资源,这一需求促进了数据中心的增长。运行于ARM服务器的Xcelium仿真可带来功耗显著降低和仿真容量的显著提升,可执行高吞吐和长周期测试,缩减了整个SoC验证的时间和成本。 作为Cadence验证套件(Cadence Verification Suite)的

[嵌入式]

Cadence全新Tensilica Vision Q6 DSP IP助力提升视觉与AI性能

基于全新、更快的处理器架构,第五代Vision Q6 DSP将在智能手机、监控摄像头、汽车、AR/VR、无人机和机器人领域大展身手 中国上海,2018年4月12日 – 楷登电子(美国 Cadence 公司,NASDAQ: CDNS)今日正式推出Cadence® Tensilica ® Vision Q6 DSP。该DSP基于速度更快的新处理器架构,面向嵌入式视觉和 AI 技术量身打造。第五代Vision Q6 DSP的视觉和AI性能较上一代Vision P6 DSP提高达1.5倍,峰值性能下的功耗效率提高1.25倍。Vision Q6 DSP为智能手机、监控摄像头、汽车、增强现实(AR)/虚拟现实(VR)、无人机和机器人领域

[嵌入式]

Cadence Allegro 16.6实战必备教程

Cadence Allegro 16.6实战必备教程 零基础学电子与Arduino:给编程新手的开发板入门指南

零基础学电子与Arduino:给编程新手的开发板入门指南

京公网安备 11010802033920号

京公网安备 11010802033920号