引言

在基于FPGA的图象采集显示系统中,常常需要用到大容量、高速度的存储器。而在各种随机存储器件中,SDRAM的价格低、体积小、速度快、容量大,是比较理想的器件。但SDRAM的控制逻辑比较复杂,对时序要求也十分严格,使用很不方便,这就要求有一个专门的控制器,使系统用户能很方便地操作SDRAM。为此,本文提出了一种基于FPGA的SDRAM控制器的设计方法,并用Verilog给于实现,仿真结果表明通过该方法设计实现的控制器可以在FPGA芯片内组成如图1所示的SDRAM接口,从而使得系统用户对SDRAM的操作非常方便。

SDRAM简介

SDRAM器件的管脚分为控制信号、地址和数据三类。通常一个SDRAM中包含几个BANK,每个BANK的存储单元是按行和列寻址的。由于这种特殊的存储结构,SDRAM有以下几个工作特性。

● SDRAM的初始化

SDRAM在上电100~200μs后,必须由一个初始化进程来配置SDRAM的模式寄存器,模式寄存器的值决定着SDRAM的工作模式。

● 访问存储单元

为减少I/O引脚数量,SDRAM复用地址线,所以在读写SDRAM时,先由ACTIVE命令激活要读写的BANK,并锁存行地址,然后在读写指令有效时锁存列地址。一旦BANK被激活后只有执行一次预充命令后才能再次激活同一BANK。

● 刷新和预充

SDRAM的存储单元可以理解为一个电容,总是倾向于放电,因此必须有定时的刷新周期以避免数据丢失。刷新周期可由(最小刷新周期÷时钟周期)计算获得。对BANK预充电或者关闭已激活的BANK,可预充特定BANK也可同时作用于所有BANK,A10、BA0和BA1用于选择BANK。

● 操作控制

SDRAM的具体控制命令由一些专用控制引脚和地址线辅助完成。CS、RAS、CAS和WR在时钟上升沿的状态决定具体操作动作,地址线和BANK选择控制线在部分操作动作中作为辅助参数输入。由于特殊的存储结构,SDRAM操作指令比较多,不像SRAM一样只有简单的读写。

SDRAM控制器的设计实现

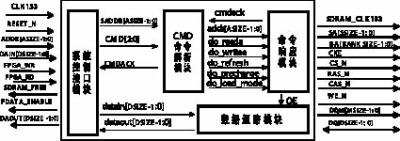

● 总体设计框图和外部接口信号

SDRAM控制器与外部的接口示意图由图1给出,控制器右端接口信号均为直接与SDRAM对应管脚相连的信号,此处不做介绍。控制器左端的接口信号为与FPGA相连的系统控制接口信号,其中,CLK133为系统时钟信号,RESET_N为复位信号,ADDR为系统给出的SDRAM地址信号,DAIN是系统用于写入SDRAM的数据信号,FPGA_RD和FPGA_WR为系统读、写请求信号(1为有效,0为无效),SDRAM_FREE是SDRAM的空闲状态标示信号(0为空闲,1为忙碌),FDATA_ENABLE是控制器给系统的数据收发指示信号(为0时,无法对SDRAM进行数据收发;为1时,若是系统读操作,则系统此时可从DAOUT接收SDRAM的数据,若是写操作,则系统此时可以通过DAIN发送数据给SDRAM)。

SDRAM控制器的结构组成如图2所示,包括系统控制接口模块、CMD命令解析模块、命令响应模块、数据通路模块共四个模块。系统控制接口模块用于接收系统的控制信号,进而产生不同的CMD命令组合;CMD命令解析模块用于接收CMD命令并解码成操作指令;命令响应模块用于接收操作指令并产生SDRAM的操作动作;数据通路模块则用于控制数据的有效输入输出。

SDRAM控制器设计的状态机实现原理如图3所示,包含了9个状态,其中从Precharge到Mode set为SDRAM上电后的初始化过程,其余状态为SDRAM的正常读写及刷新操作过程。

● 各模块的设计

(1) 系统控制接口模块

该模块内含了初始化机制和系统指令分析机制。初始化机制不仅要完成对SDRAM的初始化配置,还要完成对控制器的初始化配置,使控制器与外部SDRAM的工作模式一致。其过程如下:由计数器控制在系统上电200μs左右后,先进行SDRAM的初始化配置工作,由一个Precharge all bank指令完成对所有BANK的预充,接着是多个Refresh指令,然后是模式配置指令LOAD_MODE ,完成SDRAM的工作模式设置。之后进行控制器的初始化配置工作,先发出指令LOAD_REG1给控制器载入模式字,再发出LOAD_REG2指令载入控制器的刷新计数器值,完成控制器初始化配置。

上述初始化过程结束后,系统指令分析机制才可接收并分析系统的读写信号和地址信息,以及从下个模块反馈回来的CMDACK信号,并产生对应的CMD命令和SADDR地址信息给CMD命令解析模块。通过程序设置,实现了根据初始化配置的参数来确定在读写到特定时刻发出Precharge或者Refresh的CMD指令,从而简化了系统的控制。而每当收到CMDACK为1时,表示CMD指令已经发出并有效,此时就要发出NOP命令(CMD=000)。要说明的是,SADDR是分时复用的,在初始化载入模式时,SADDR用以传输用户自己定义的模式字内容;而在正常的读写期间,SADDR作为地址线传输SDRAM所需的行、列和块地址。此外,系统指令分析机制会根据控制器对SDRAM的操作处于什么样的状态,而反馈SDRAM_FREE和FDATA_ENABLE信号给系统用户。

(2) CMD命令解析模块

该模块对CMD指令进行判断,其结果就是输出相应的操作指令信号给命令响应模块。例如,CMD为001时,则会输出do_read信号为1,CMD为010时,则会输出do_write信号为1,在同一时刻,只会输出一种有效的的操作指令。

此外,该模块内含用以预设某些模式参数的模式寄存器,主要包括三类:第一类是SDRAM模式控制寄存器,在LOAD_MODE指令时,将该寄存器的值送入SDRAM的模式寄存器中,以控制SDRAM的工作模式。第二类是SDRAM控制器的参数寄存器(LOAD_REG1),使得SDRAM控制器的工作方式与外部的SDRAM器件的工作方式匹配。第三类是SDRAM的刷新周期控制寄存器,该寄存器预设用户定义的自动刷新计数值,用于SDRAM的刷新周期预设。上述三类寄存器的预设值都是系统控制接口模块在初始化时通过SADDR传送给来的。

(3) 命令响应模块

该模块的作用是根据从CMD命令解析模块得到的操作指令,做出符合SDRAM读写规范的操作动作,来进行用户期望的操作;给出数据选通信号OE,来控制数据通路模块(写操作时OE为1,读操作时OE为0)。此外,该模块把系统非复用的地址ADDR处理为SDRAM复用的地址,分时送给SA、BA。程序中地址复用方法为:

assign raddr = ADDR[ROWSTART + ROWSIZE -1:ROWSTART] //raddr为行地址

assign caddr = ADDR[COLSTART + COLSIZE -1:COLSTART] //caddr为列地址

assign baddr= ADDR[BANKSTART +`BANKSIZE -1:BANKSTART]//baddr为BANK地址

(ROWSTART、COLSTART、BANKSTART分别为行、列、块在ADDR中的起始位)

在程序中,WRITEA和READA的CMD指令实际隐含了ACTIVE命令,所以该模块在收到do_write或do_read指令后,会先进行激活动作,经过初始化配置规定的CAS延迟时间之后再进行读写动作。例如初始化时,模式字规定CAS=2,BURST LENGTH=PAGE,则从命令接口模块收到do_write=1后,会先做出激活动作并给出行地址(发出RAS_N=0,CAS_N=1,WE_N=1,SA=raddr),过2个时钟延迟后,再做出写动作并给出列地址(发出RAS_N=1,CAS_N=0,WE_N=0,SA=caddr)。

此外,收到各类操作指令后,该模块会反馈给CMD命令解析模块cmdack信号为1,并最终反馈到系统控制接口模块的CMDACK信号为1,如果没有收到任何操作指令,则cmdack=0,CMDACK信号为0。

(4) 数据通路模块

该模块受OE信号的控制,使数据的进出和相应的操作指令在时序上同步。OE为1时,数据可由DQ脚写入SDRAM,OE为0时,数据可从SDRAM的DQ脚读出。

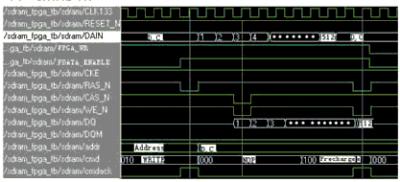

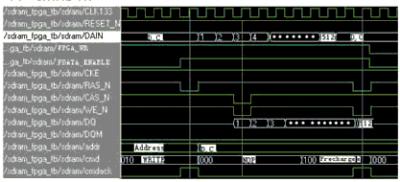

控制器的使用及仿真时序---根据系统设计对SDRAM读写要求的不同,对控制器进行简单的参数修改(主要是初始化时模式内容字的设置),即可使对SDRAM的控制符合自己的要求。该控制器使得系统对SDRAM的操作非常简单。以写操作为例,初始化结束后,只要SDRAM空闲,系统就会收到SDRAM_FREE有效信号,此时可以发出FPGA_WR指令,同时给出ADDR地址信息,在收到反馈的FDATA_ENABLE有效后,系统将数据通过DAIN写到SDRAM中去,即完成写操作,系统无须关心SDRAM的刷新和预充。仿真时序图如图4、图5和图6所示,在写和读时序中,CAS=2,BURST LENGTH=PAGE,DC表示无关(Don’t care)。

仿真结果表明,该控制器可以使得系统对SDRAM的控制非常简单、方便。

结束语

在实际应用中,使用ALTERA公司的Cyclone FPGA器件进行设计,设计输入采用Verilog来完成,实现了上述的SDRAM控制器接口电路。此外,由于采用了参数化设计思想,对特定容量的SDRAM的特定工作模式而言,只要根据其器件参数进行设定,该控制器就可以适用特定SDRAM的特定工作模式,具有一定的通用性。

上一篇:嵌入式系统中软件优化的低功耗研究

下一篇:TI低成本、高性能家用与车载音频 DSP

推荐阅读最新更新时间:2024-05-02 20:25

汽车EPS控制器测试系统研究和设计

汽车EPS控制器测试系统研究和设计 硬件架构艺术:数字电路的设计方法与技术

硬件架构艺术:数字电路的设计方法与技术

京公网安备 11010802033920号

京公网安备 11010802033920号