1 引 言

数字复接就是把两个或两个以上的支路数字信号按时分复接方式合并成单一的合路数字信号。按照各低次群时钟的情况,复接有3种方式:如果各输入支路数字信号相互同步,且与本机定时信号也同步,那么调整单元只需调整相位,这就是同步复接;如果输入支路数字信号不同步且与本机定时信号也异步,那么调整单元就要对各支路信号进行频率和相位的调整,使之成为同步信号,这就是异步复接;如果输入支路数字信号的生效瞬间相对于本机对应的定时信号是以同一标称速度出现,而速度的任何变化都限制在规定的容差范围内,这种就是准同步(PDH)复接[1],本文研究的就是基于CPLD的PDH通信二次群复接器。

2 二次群复接的基本原理

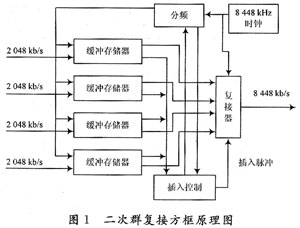

二次群复接就是把4个2 048 kb/s的信号复接成1个8 448 kb/s的二次群数字信号,其原理图如图1所示。

复接器由缓冲存储器、插入控制电路、时钟发生器、分频器和复接器组成。时钟产生器提供8 448 kHz时钟;分频器对8 448 kHz进行4分频,以获得2 112 kHz的读出时钟;缓冲存储器和插入控制电路用来进行码速调整,把标称速度相同实际有容差的4个2 048 kb/s的支路都调整到2 112 kb/s上,使他们同步;复接器是将4个已经同步的支路信号复接成1个8 448 kb/s的二次群信号[2]。

2.1 数字复接方法

数字复接方法有3种:按位复接、按码字复接、按帧复接。由于后两者所需缓冲存储器的容量较大,目前应用的很少。故本文采用按位复接,其示意图如图2所示。

图中,a,b,c,d是4个支路信号,e是复接后的二次群信号。复接过程如下:首先轮流取4个基群的第1位码,之后再轮流取第2位码,依此类推。可以看出,复接后每位码的宽度只是原来支路每位码宽度的1/4,即容量增加了4倍,基群话路信号的容量为30个话路,复接后为120路。这种方法简单易行,所需缓存器的容量最小,现有的复用设备多采用这种方式。缓冲存储器的容量由式(1)决定:

式中u为复接单位的比特数,m为被复接的基群数,这里,u=1,m=4,1 b是先写进去以便读出的存储起始量,由此可得:

可见,缓冲存储器的容量取2 b就够了[1]。

2.2 码速调整帧结构

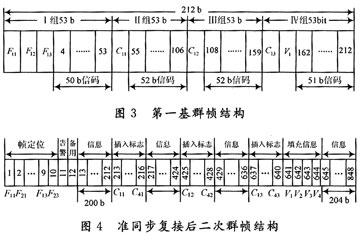

由ITU-T建议G.724推荐的准同步复接二次群帧结构如图3、图4所示。

二次群帧长为848 b,一帧分为4组,每组为212 b,这212 b的分配,4个基群相似,以第l基群为例,帧结构如图3所示。将212 b分为4组,每组53 b。第Ⅰ组的1,2,3三个码位,供插入复接器帧同步码用,以F表示;然后是50 b的信息码;Ⅱ,Ⅲ,Ⅳ组的第1位码用作标志信号,用C表示;第Ⅳ组的第2个码位就是码速调整的码位,用V表示,需要插入时,就在这个位置上插入一个不带信息的脉冲,不需要插入时,这个码位仍传信息码;Ⅱ、Ⅲ、Ⅳ组的其他位置都是信息码。4个基群的第1~3个码位复接在一起,共12位,其中前10位作为复接器的帧同步码,第ll位为告警指示,第12位作为备用。4个基群的插入标志信号码和码速调整比特,复接后又分别连在一起。具体复接帧结构图如图4所示。复帧包含的比特内容如下[1]:

(1) 帧定位10 b,表示为F11F12~F13F23,码型为1111010000;

(2) 公务2 b,其中1 b(11位)用来向对端发出告警指示;另外1 b(12位)留作国内使用;

(3) 支路信息820 b,第Ⅰ组为200 b(13~212),第Ⅱ组为208 b(217~424),第Ⅲ组为208 b(429~636),第Ⅳ组为204 b(645~848);

(4) 码速调整4 b,表示为V1,V2,V3,V4(641~644位),各基群l b,共4 b;

(5) 插入标志12 b,以C表示,填充脉冲4 b。为了使接收端能知道是否有插入及插在何处,在复接发端发出插入指令的同时需要发出插入标志信号,以告知分接器有插入。现在常用的办法是定位插入。在这里规定:第1基群第1位插入标志C11在213位插入,第1基群第2位插入标志C12在425位插入,第1基群第3位插入标志C13在637位插入。由此可知:

C11C21C31C41 (213—216)是第l位插入标志;

C12C22C32C42 (425—428)是第2位插入标志;

Cl3C23C33C43 (637—640)是第3位插入标志;

插入标志信号是3位,采用3位码来组成插入标志信号,可提高标志信号的可靠性。用“111”表示有插入,用“000”表示无插入。当C11C12C13为“111”时,表示在641时隙的脉冲是插入脉冲;当C11C12C13为“000"时,表示在641时隙的脉冲是信息码[1]。

3 数字复接电路VHDL程序设计及仿真

基于以上的原理介绍,可以知道PDH数字复接器一般由分频器、缓冲存储、插入控制、合路器等几部分组成,这里我们使用VHDL进行模块化编程,把整个复接系统设计成3部分:分频器、码速调整控制器(实现缓冲存储以及码速相位的调整插入)、合路器。原理框图如图5所示。

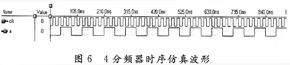

3.1 分频部分仿真波形

分频器是将8 448 kHz的时钟4分频得到2 112 kHz的时钟,给码速调整提供读出时钟。其时序仿真波形如图6所示。

3.2 码速调整部分程序设计及仿真波形

正码速调整就是将被复接的低次群的码速都提高,使其同步到某一规定的较高的码速上。以二次群复接为例,二次群由4个一次群合成,一次群码率为2 048 kb/s,二次群的码率为8 448 kb/s,因此,可以根据复接帧的要求,插人相应的脉冲数目,将基群速率调整为2 112 kb/s,然后将4个支路合并,就可以得到1路码元速率为8 448 kb/s的二次群。采用脉冲插入同步的正码速调整的原理示意图如图7所示。

基群输入速率为2 048 kb/s的数字信号到一个缓冲存储器,读出时钟频率则是码速调整后的速率2 112 kb/s,所以存储器处于“快读慢写”的状态。从图7(a)和图7(b)可以看出,第一个脉冲经过一段时间后读出,第二个脉冲的读出所经过的时间比前者要短,因读出速度比写入速度快,以后的写入与读出时间差,即相位差越来越小,当相位差小到一定程度时,由相位比较器(缓冲存储器中)发出插入请求,要求插入脉冲控制电路发出一个插入指令,停止一次读出,同时插入一个脉冲,如图中虚线位置所示。插人脉冲不携带信息,在接收端应把他去掉,为此,发送端在插入脉冲的同时,必须发出一个标志信号告知接收端哪些是插入脉冲,以便把他去掉以恢复原始信号。

接收端收到发送端的标志信号后,他连同信号一起经过一个标志信号检出电路而被检出,因而产生一个“消插信号”,把写入脉冲禁掉一个,如图7(c)所示。这时,数码与原来的数码次序一样,但时间间隔是不均匀的,因此在接收端必须从图7(c)中提取时钟,通过锁相环的环路作用来将已去掉插入脉冲的数码流均匀化。4个基群支路的速率都调整到2 112 kb/s后,再复接成二次群[1]。码速调整生成器件及其时序仿真波形如图8所示。

3.3 复接(合路)部分程序设计及仿真波形

图中d1,d2,d3,d4依次为输入的低次群支路信号,quik8448为复接后的二次群输出信号,在8 448 kHz读出时钟的下降沿触发。在4个时钟周期内依次读取输入信号d1,d2,d3,d4为“1100'’,下一个为“1001”,依次类推,最终的输出为“1100 0110 1001 1111…”。

3.4 综合电路

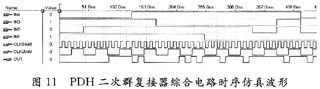

综合以上的各个模块,可以得到综合电路来实现二次群复接功能,具体的实现框图如图10所示。

时序仿真波形如图11所示。图中,IN1,IN2,IN3,IN4分别是4路2 048 kb/s的支路信号,0UT为复合后输出的8 448 kb/s二次群复接信号。输出信号前面10位为帧定位比特(1111010000),11、12位是公务比特,这里设为“00”,从13位开始为信息比特,根据2 048 kHz时钟依次读人输入信号,根据读出时钟8 448 kHz读出复合后二次群信号为“1010 1110 1110 1111…”。由仿真结果可以看出系统的设计与仿真与理论预测相符。

4 结 语

数字复接技术不仅仅是与信源编码、数字传输、数字交换相并列的专门技术,而且还是网同步中的帧调整,线路集中器中的线路复用以及数字交换中的时分接续等技术的基础,因此,数字复用技术是数字通信中的一项基础技术[3]。

以往的PDH复接电路中,系统的许多部分采用的是模拟电路,因此有很大的局限性。而本文实现的基于CPLD技术的PDH复接器就打破了这些局限性,具有设计周期短、修改方便、不受现有专用芯片功能的限制、可靠性和集成度高等优点,是目前系统设计者们的优先选择。随着可编程逻辑器件性能不断提高,开发系统不断完善,可编程逻辑器件在电予工程设计中的应用必定越来越广泛。

上一篇:一种用CPLD实现的短帧交织器设计

下一篇:Spartan-3A DSP 揭示数字信号处理新趋势

推荐阅读最新更新时间:2024-05-02 20:35

通信基础以及汽车总线技术概述

通信基础以及汽车总线技术概述 21年电赛题目合集

21年电赛题目合集 Verilog HDL数字集成电路设计原理与应用

Verilog HDL数字集成电路设计原理与应用

京公网安备 11010802033920号

京公网安备 11010802033920号