数据采集是自动测试系统的主要功能之一,而在一些应用领域,比如超声、医疗电子中,信号的频率范围不同会要求采样率的不同。有时,为了配合信号处理算法,甚至要求采样率在一定范围内随意设定。而且,这些应用通常要求多个通道并行采集,甚至是差分单端方式可选择的输入。针对这些要求,我们提出了一种最多可达12通道的同步并行多通道数据采集方案。该方案能实现的最高采样率为10MS/s,存储深度2×32M×16bit(2个SDRAM),垂直分辨率14bit,可编程增益为1、2、5、10、100五个等级。

设计方案的确定

图1 系统原理框图

图2 信号输入方式选择电路

信号调理电路设计

在本设计中,信号调理电路包括输入方式选择电路和增益选择电路。此部分中,高输入阻抗、低输出阻抗的普通运算放大器构成的电压跟随器会对前后电路进行隔离,避免后级多路开关的导通阻抗影响前级电路。输入端加两个二极管,提供±15V的钳位电压,形成过压保护。多路开关选择DG409,它是4通道差分多路开关,具有较低的导通阻抗和低功耗和低泄漏电流。信号的输入方式有四种:0输入、单端正极输入、单端负极输入和差分输入,通过DG409正好可以选择这四种输入方式,电路如图2所示。

选择一种输入方式后,经过两级可编程增益仪表放大器AD8250,可以实现增益值可选1、2、5、10、100五个等级。AD8250有两个增益控制端A0、A1,写这个两个位,能选择增益值,并通过W/R锁存状态值,从而保证该增益的稳定。本设计通过在FPGA内部设计串行传输逻辑,将数据写入CPLD,然后控制选择信号的输入方式和写AD8250增益控制位。增益选择电路如图3所示。

图3 增益选择电路

数据采集与控制电路设计

A/D转换器是数据采集系统的核心,对A/D器件的选择往往影响到整个系统的性能指标。为了实现8通道并行同步采样可以采用两种方案。一是采用8个独立的A/D转换器,这样不仅成本比较高,而且难以实现8通道同步采样,绘制PCB板的时候也有很大的困难。第二种方式就是本设计的方法,采用一个AD9252来满足最多8个通道的并行同步采样要求。本设计通过NIOSII软核处理器向AD9252发送控制字,以实现8通道并行同步采样。首先,输出14bit的LVDS信号到FPGA,经由串并转换逻辑输出14bit并行数据,再通过仲裁逻辑实现不同通道数据存储位置的不同,最后通过两片SDRAM的乒乓操作实现连续数据采集和传输。

本设计数字控制部分由FPGA和外扩的CPLD共同合作完成。由于设计需要大量的引脚资源,而FPGA的引脚资源有限,所以在FPGA外部通过SPI总线接口外接一片CPLD,从而控制8个通道的输入方式选择和增益选择。FPGA内部嵌入一个NIOSII软核,负责数据采集、数据传输和输入方式以及增益的选择控制。下面详细分析一下这三个数字控制电路的实现方法。

1信号输入方式和增益选择控制逻辑的实现

FPGA和CPLD之间通过串行总线通信。通过在FPGA内部构建一个8bit地址总线,8bit数据线的RAM块,用来存储输入方式和增益选择控制数据。8bit地址线的前三位用来控制通道号,后五位控制所在通道的20种选择状态(4种输入方式,5种增益选择)。8bit数据的前两位是输入方式的选择码,后六位是增益选择码。在FPGA内构建一个地址计数器来进行通道的选择数据提取,该计数器的时钟频率是SPI控制器时钟的32倍。

在CPLD中构建一个48bit的串并转换逻辑,把输入方式选择码和增益选择码送到相应的引脚,从而实现信号输入方式和增益选择控制逻辑的实现。

2数据采集和传输控制逻辑的实现

本设计在FPGA内部设计逻辑如下:

读取ADC串行LVDS数据流,然后通过串并转换逻辑把串行数据流变成并行数据流;

内部设计SDRAM的控制逻辑,实现数据的存储,通过内部的仲裁逻辑实现不同通道的数据存储按照一定的时序存储在SDRAM中;

判断第一个SDRAM已经满后,通过片选切换逻辑把数据存储在第二个存储器中,同时通过DMA方式把数据传输到上位机。

图4 控制逻辑框图

图4是FPGA内部控制逻辑框图。

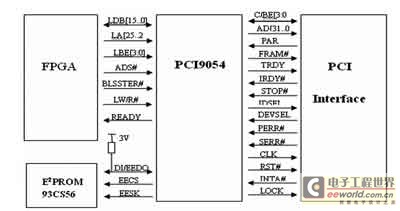

3 PCI接口电路设计

本设计采用PCI总线作为数据总线连接采集模块和上位机进行通信,用以实现数据的分析处理和历史显示等功能。

由于设计中的采集模块需要工作在连续采集系统中,所以当存储器存满之后,需要快速输出通道将数据通过PCI接口传输出去。本设计采用DMA的方式传输数据,这样做既可以不占用CPU资源,又能实现快速的数据传输。我们选用了使用比较稳定的专用PCI接口芯片PCI9054作为总线控制器和上位机通信。该芯片符合PCI2.2总线规范,支持低成本从属适配器PCI时钟为0~33MHz,理论的数据传输速率可达132Mb/s,实际速率为60Mb/s。

图5 PCI接口电路

本设计中,PCI9054被配置为从模式,用FPGA作为主控制器实现数据的传输控制。PCI9054有三种总线操作模式:M模式、C模式和J模式。M模式主要是配合MPC850/MPC860处理器使用的,主要用在电信领域。J模式用来满足接口设计比较复杂的情况,C模式主要为通用模式。本设计采用C模式,接口电路如图5所示。

FPGA按照PCI9054的读写时序设计读写控制逻辑,接收上位机传来的命令,对电路进行相应的设置后,启动ADC采集数据,然后将采集到的数据送到SDRAM中;当一个SDRAM满后产生一次中断,将已经满SDRAM的地址线映射到PCI9054的本地数据线上,同时通过本地主控方式配置PCI9054的DMA控制器,通过DMA方式将SDRAM中准备好的数据上传。本设计使用了14位的本地数据总线和24位地址总线进行数据传送和地址译码控制。

结语

通过充分考虑设计中可能出现的各种影响信号质量的因素,设计了过压保护电路。通过选用合适的元件减少了电路板设计复杂程度,以及成本的最优化。经过实际测试,模块很好地达到了本文所提及的技术指标,具有很高的实用性。

硬件电路主要包括信号调理电路、信号输入方式选择电路、程控增益电路、A/D转换、数据存储、触发控制以及PCI接口几个部分。8个通道输入的模拟信号经信号调理电路调理后,进行单端变差分的转换(前端也可以是直接输入的8路差分信号),由多路开关选择输入方式后,再通过两级可选择增益放大器进行增益控制,最后进入ADC转换成相应的数字信号。而逻辑控制单元在接收到采集命令后,会根据相应的触发方式启动ADC进行采样,再将采样得到的数据通过FPGA内部串并转换逻辑和数据输出仲裁逻辑存储到SDRAM中准备上传。本设计的采集极限指标是8个通道同时同步采集,最大采样速率是单通道10MS/s,连续采样存储时间最大可以达到3.2s。上位机通过32位的数据总线采用查询、中断或者DMA方式将采集的数据读取到内存中进行后期的数据处理和分析。系统的基本结构如图1所示。

关键字:数据采集 PCI模块

引用地址:

8通道并行数据采集PCI模块的设计

推荐阅读最新更新时间:2024-03-30 22:22

基于DSP与FPGA的蓝牙数据采集系统设计

数据采集系统广泛地应用于工业、国防、图像处理、信号检测等领域。DSP处理器是一种高速的数字信号处理器,蓝牙技术作为一种低成本、低功耗、近距离的无线通信技术,已广泛应用于许多行业和领域 。本设计采用了DSP与FPGA协同控制处理,并用蓝牙传输代替有线电缆传输,有效地解决了DSP和FPGA单独处理的不足与有线电缆传输的弊端,大大提高了数据采集处理能力,拓宽了系统在环境较为恶劣或特殊场所的应用。 1 系统硬件设计 1.1系统总体设计 基于DSP与FPGA的蓝牙数据采集系统由下位机和上位机两部分组成。其中下位机主要由前端传感器、信号调理电路、ADC模数转换电路、DSP与FPGA协同处理模块以及蓝牙模块组成,主要完成前端数据的

[嵌入式]

多通道同步数据采集及压缩系统的设计方案

1 引言 现代遥测系统中为了尽可能少地占用传输时间和存储空间,在有限的信道容量内传输更多的有用信息,采用数据压缩技术,有助于降低功率和带宽要求,改善通信效率。这里提出一种基于DSP与CPLD的多通道同步数据采集与压缩系统设计方案,该系统应用于遥测多路噪声数据,其中多通道同步数据采集可实现同时测量信号。并进行相关分析后,得到信号间的相关信息,而DSP内嵌的数据压缩算法实现其数据压缩的功能。 2 系统的硬件结构 2.1 系统设计思路 图1为系统设计的硬件框图。基于CPLD和DSP的多通道同步数据采集及压缩系统主要由数据采集模块、数据处理模块以及数据接口模块3部分构成。前端由传感器输人的模拟信号经信号调理

[嵌入式]

一个单片机串行数据采集/传输模块的设计

在微机测控系统中,经常要用到A/D转换。常用的方法是扩展一块或多块A/D采集卡。当模拟量较少或是温度、压力等缓变信号场合,采用总线型A/D卡并不是最合适、最经济的方案。这里介绍一种以GNS97C2051单片机为核心,采用TLC2543 12位串行A/D转换器构成的采样模块,该模块的采样数据由单片机串口经电平转换后送到上位机(IBM PC兼容机)的串口COM1或COM2,形成一种串行数据采集串行数据传输的方式。经实践调试证实:该模块功耗低、采样精度高、可靠性好、接口简便,有一定实用价值。 1 主要器件介绍 1.1 TLC2543串行A/D转换器 模块采用TI公司的TLC2543 12位串行A/D转换器,使用开关电容逐次逼近技术

[单片机]

一款基于AD9650的高速数据采集系统设计

随着数字信号处理技术的发展,越来越多的信号处理环节可以通过后端的软件处理完成,但这反而使得电子设备对前端数据采集系统的要求不断提高。因为后端软件的处理效果归根结底依赖于数据中所包含的信息量,只有提高数据采集的动态性能,才能保障后端处理的效果。长期以来,在数据采集领域,高速大动态范围 ADC 系统的设计与实现始终是研究的热点。当雷达工作在高杂波的电磁环境中,探测对象的RCS或多普勒信息非常微弱时,就对设计实现高速大动态范围数据采集系统提出了迫切的需求。 目前,国内对高速大动态范围 ADC 数据采集系统设计主要依赖于芯片的指标而缺乏系统的研究和总结。本设计旨在通过优化系统设计,结合动态性能优越的模数转换芯片,实现一个高速大动态范围数据

[电源管理]

用于数据采集的超高性能差分输出可编程增益仪表放大器

数据采集系统和可编程逻辑控制器(PLC)需要多功能的高性能模拟前端,以便与各种传感器进行接口,来精确、可靠地测量信号。根据传感器具体类型和待测电压/电流幅度的不同,信号可能需要放大或衰减,从而匹配模数转换器(ADC)的满量程输入范围,以供进一步的数字处理和反馈控制。

数据采集系统的典型电压测量范围是从 ±0.1 V 到 ±10 V 。通过选择正确的电压范围,用户间接的更改系统增益,使模数转换器 (ADC) 输入端的采样电压幅度最大,进而最大程度地提高信噪比 (SNR) 和测量精度。在典型的数据采集系统中,需要衰减的信号与需要放大的信号分别通过不同的信号路径进行处理,这通常导致系统设计更为复杂,需要额外的器件,并且

[电源管理]

液压油缸内壁参数测量数据采集处理系统

液压传动在车辆、起重运输机械、工程机械、矿山设备及其他机械中具有广泛的应用。油缸作为液压传动中不可或缺的组成部分,其内径各参数的精度,将直接对传动系统的性能产生影响。 对类似于油缸内壁的孔径测量方法,一般分为直接测量法和间接测量法。直接测量法是利用两点或三点定位,直接测量出孔径的方法。其常用测量工具包括内径干分尺、万能测长仪、卧式测长仪等,通用长度测量工具和内径测微仪、柔性坐标测量机等专用的孔径测量工具,但此类测量方法效率低、误差大,且不易用于深孔径和高精度产品的在线测量。间接测量法是利用三点定一圆原理,测出被测孔圆周上任意三点的坐标值,然后根据相关算法,求出圆心坐标,再换算出孔径尺寸和其他参数。此类方法效率高、误差

[测试测量]

16位ADC提供19位分辨率的电路设计

许多数据采集系统都要求高精度和快速采集数据,以便允许该系统能够检测小信号并且能将更多的传感器通道*在同一系统。传感器通道越多,系统的外形就能够越小,成本和功耗也越低。远程光通信和医用设备(例如,CT扫描仪)即得益于快速和高精度的数据采集系统。在光功率系统(例如,激光泵)中,需要不断监视其功率水平。在这种数据采集系统中,对于需要≥90dB动态范围的输入激光功率,其激光控制环路响应时间要求具有1MSPS的采样率。在CT扫描仪中,数据采集系统必须具有16 b到22 b的分辨率,以便处理通过各种人体组织的宽动态范围的X射线信号。该系统需要大量的光检测器(较多的数据采集通道)和高精度数据采集以提高图像分辨率。 以上两个例子说明了系

[模拟电子]

用实时时钟芯片DS1305启动数据采集系统

摘要:介绍串行时钟芯片DS1305的功能、结构及其利用DS1305设计的电源开关电路,可使数据采集系统平时处于关闭状态。定时开启时系统上电,进行数据采集;一次工作结束时关闭开关,系统断电。

关键词:DS1305 低功耗 数据采集

引言

对于许多便携式数据采集系统,需要长时间无人看管地工作,如在石油钻井下、输油管道等场所。一般需要间隔数小时进行一个采集,这样系统大部分时间处空闲状态。虽然现在低功耗单片机的睡眠状态提供了降低功耗的一种方法,但低功耗不等于没有功耗,系统长时间工作时不得不考虑功耗的问题。

为进一步节省功耗,我们在研制一数据采集系统时,利用实时时钟芯片DS1305设计一电源开关电路。利用该开关电路,可使系统在空头时

[应用]

深入理解Linux驱动程序设计 (清华开发者书库) (吴国伟 姚琳 毕成龙)

深入理解Linux驱动程序设计 (清华开发者书库) (吴国伟 姚琳 毕成龙) 零基础学电子与Arduino:给编程新手的开发板入门指南

零基础学电子与Arduino:给编程新手的开发板入门指南

京公网安备 11010802033920号

京公网安备 11010802033920号