1 系统设计方案

1.1 动态存储测试

所谓存储测试技术,是指在对被测对象无影响或影响在允许范围的条件下,在被测体内置入微型存储测试仪器,现场实时完成信息快速采集与存储,事后回收记录仪,由计算机处理和再现被测信息的一种动态测试技术。

1.2 测试系统总体设计

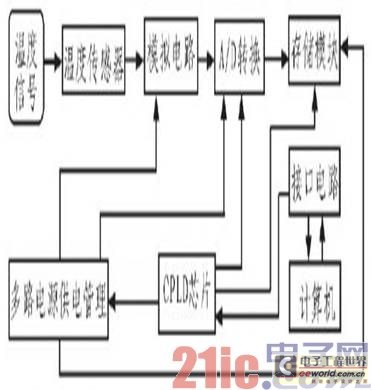

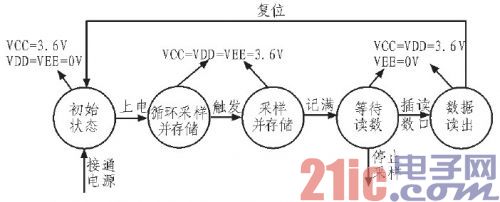

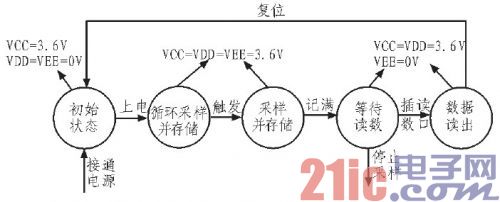

本次设计的温度测试系统,主要是利用CPLD来实现。温度传感器将外界温度信号转换为微弱的电压信号,通过模拟电路部分将输入信号进行放大和滤波,再经过A/D转化电路把模拟信号转换为数字信号,然后经过FIFO存入存储器,计算机通过接口电路对数据进行读取。温度测试系统的原理框图如图1所示。其中,A/D转换器、FIFO、存储器和电源管理模块都是由CPLD控制。

图1 温度测试系统的原理框图

2 关键技术

2.1 主控芯片CPLD的选择

在本次设计中使用Xilinx公司生产的XCR3128作为温度测试系统的主控CPLD芯片。XCR3128有100个引脚,其中有76个I/O引脚,4个信号接口,4个全局时钟,7个VCC,8个GND,1个PORT_EN;共包含128个宏单元,VCC为3.6 V,电流限制为200mA.XCR3128封装小,功耗低,充分满足了实际需要。

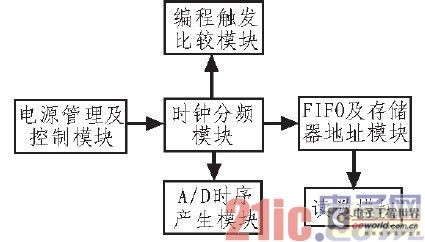

在本次设计中,控制部分主要由CPLD控制电路时序和工作模式的产生。控制功能图如图2所示,主要功能有:

1)电源管理及控制模块:该模块主要实现测试系统的电源管理及全局时钟控制,从而达到降低功耗和控制各信号初态的目的。

2)时钟分频模块:该模块主要实现对从晶体振荡器输出到CPLD的时钟进行分频,从而得到A/D转换器、存储器和FIFO需要的时序。

3)编程触发比较模块:该模块主要实现触发温度数字电平的编程,通过移位寄存器实现;数字比较部分是把A/D转换结果和所编温度数字电平值比较判断触发与否。

4)FIFO及存储器地址模块:该模块主要实现生成FIFO和存储器需要的地址,FIFO和存储器的数据读写。

5)A/D时序产生模块:该模块主要实现A/D转换器的CONVST/和读信号的时序生成。

6)读数模块:该模块主要实现读数接口的逻辑连接控制,接收计算机发送的脉冲信号,以完成数据传输的目的。

图2 温度测试系统CPLD控制功能图

2.2 温度传感器

在爆炸场等高温、高压、高冲击的恶劣环境下采集瞬时温度的动态变化对温度传感器要求很高,因此选用了美国NANMAC公司的E12钨铼侵蚀热电偶。该热电偶瞬态温度响应时间仅为几百微妙,温度范围高达2 315℃,耐压程度高达69 MPa,完全能够满足爆炸场温度测试的需要。

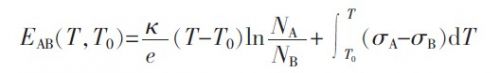

热电偶是利用导体或半导体材料的热电效应将温度的变化转换为电动势的变化,热电偶回路中产生的电动势差为:

NA、NB为材料A、B的电子密度;σA、σB为导体A、B的汤姆逊系数,K为波尔兹曼常数。

由于导体汤姆逊效应引起的电动势差相比较小,常可忽略,因此当热电偶的两种材料的特性为已知时,一端温度固定,则待测温度T是电动势的单值函数。为了使E12钨铼热电偶冷端温度固定在0℃,本次设计采用了补偿电桥法补偿冷端的温度变化。

2.3 电源管理模块

由于温度测试系统经常需要在恶劣的环境中工作,所需的能量都是靠一次性的高温电池来供给,电量有限。而温度测试系统往往要求测试过程很长,为了减小在测量过程中由于电量不足而使电路不能正常工作的可能性,就必须考虑测试系统低功耗的要求。因此设计了先进的电源管理模块,即电路在需要工作时给其供电,在不需要工作时断电,减小电路无效操作时功耗的比例。

为了减少不必要的损耗,采用了多路电源供电管理模式,分别为:VCC、VDD、VEE.VCC和CPLD相连接,存储模块部分、AD转换部分由VDD供电,运算放大器、晶振由VEE控制。

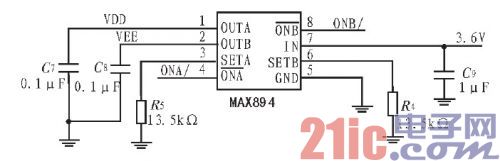

本系统中选用双通道电源开关芯片MAX894作为电源管理芯片,其供电范围为2.7~5.5 V,关断时消耗电流仅为0.1μA,两通道全部打开是消耗电流约为17 μA.在本次设计中MAX894芯片输入电源VCC=3.6 V,通过ONA/控制产生VDD=3.6 V,通过ONB/控制产生VEE=3.6V. ONA/ONB/低电平有效,由CPLD内部控制。如图3所示。[page]

图3 温度控制系统电源管理模块

电源管理模块在CPLD内部的控制部分如图4所示,ONON和OFF是电路模块的开关,TC/是CPLD外接晶振的使能端,高电平有效。当电路上电后,ONON变为高电平,ONA变为高电平,ONAN变为低电平,电源管理模块的VDD输出有效,AD转换部分和存储模块部分开始工作。由于晶振此时处于工作状态,所以TC为低电平,ONBN也是低电平,电源管理部分的VEE输出有效。当存储器的存储空间存满后,晶振停止工作,TC变为高电平,ONBN也变为高电平,所以VEE输出无效,运算放大器部分关闭。此时电路处于微功耗状态,存储器处于待读数状态。当存储器中的数据被读出后,电路可以关闭。此时除了CPLD,所有器件均被关闭。

图4 电源管理模块逻辑控制图

3 软件设计

温度测试系统的工作流程规划为5个部分:接通电源的初始状态、上电后的循环采样状态、触发后的采样存储状态、采集完后的待读数状态、数据读出及数据处理状态。温度测试系统的状态转换图如图5所示。

图5 系统状态转换图

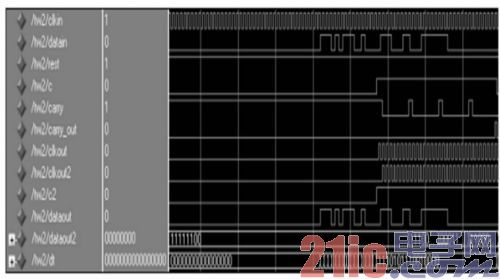

图6为测试系统的仿真时序图,通过多次软件仿真,得出正确的仿真结果,表明了本次设计的温度测试系统在理论上能够满足测试要求。

图6 系统时序仿真图

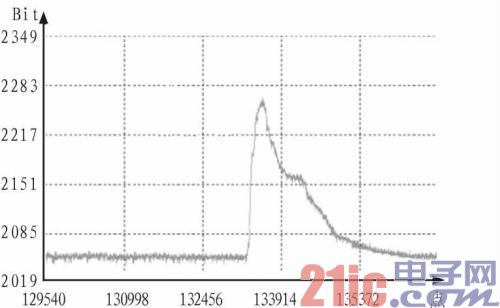

图7为实际温度测试结果图,通过VB软件处理得到。在此次实验中温度测试系统采集的数据曲线与所给环境温度的动态变化基本一致,表明本次设计的基于CPLD的温度测试系统能够可靠准确地采集数据信号。

图7 实测数据图

4 结论

本次设计的温度测试系统,采用集成度高、可靠性强、功耗较低的CPLD作为主控单元,运用耐高温高压、响应时间快的热电偶作为温度传感器,匹配先进的电源管理模块实现了测试系统的低功耗,并结合动态存储测试技术,能够应用于环境条件比较差的恶劣环境中,在可靠可信、微功耗的基础上能得到较好的实验数据。

上一篇:医疗应用中的压力测量

下一篇:基于CPLD的电磁扳机控制仪

推荐阅读最新更新时间:2024-03-30 22:50

数字电路答疑解惑与典型题解_北京邮电大学 (吴蕾、杨平乐、王诗兵、吴婷)

数字电路答疑解惑与典型题解_北京邮电大学 (吴蕾、杨平乐、王诗兵、吴婷)

京公网安备 11010802033920号

京公网安备 11010802033920号