1、控制系统概述

随着工业的发展,三坐标测量机越来越显示出其重要作用。而电机控制系统对三坐标测量机的运行有着非常重要的作用。由于FPGA可以现场可编程,可以实现专用集成电路,能满足片上系统设计(SOC)的要求,使其日益成为系统的关键部件。[1]本文介绍一种基于FPGA的电机控制系统,用于控制三坐标测量机电机运行。

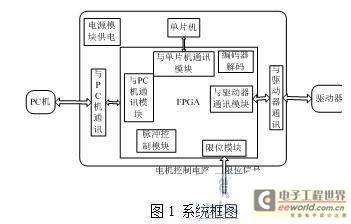

系统主要由PC机、控制电路、驱动器[2]和电机组成。系统结构图见图1。

其中PC机,由VC++实现用户界面,发出的命令由FPGA进行接收和缓存,单片机进行分析处理产生控制命令,控制命令再经过FPGA传入驱动器,控制电机运行。同时电机状态信息反馈回PC机,用于人机交互。系统中FPGA选用的是Altera公司的Cyclone系列。

2、系统功能实现

下面分别介绍FPGA实现电机控制功能的几个重要部分。

2.1编码器进行速度、位移量测量的实现方法

编码器为传感器类的一种,主要用来侦测机械运动的速度、位置、角度、距离或计数,在电机控制中用于换相、速度及位置的检出,作用十分重要。 光电编码器具有分辨率高,响应速度快,体积小,重量轻,耐恶劣环境等特点,故常被用作高精度位置检测传感器。它的精度或分辨率主要决定于每转输出的脉冲数(对增量式编码器而言)。根据控制需要,还可以利用倍频技术来提高位置检测精度。[5]本系统使用增量式编码器即增量编码盘。

增量编码盘输出信号A和B具有90°的相位差。A和B的相位关系反映了被测对象的旋转方向,若A超前于B,表明编码器是顺时针旋转的,反之,编码器为逆时针旋转。当增量编码盘的细分数为N时,增量编码盘的每一个脉冲代表的角位移为360°/N,A、B信号的频率相同,频率大小反映当前电机速度,由这两个信号就可得到电机转向、转角和转速。[6]如图2所示,在A和B的上升沿和下降沿计数器均做相应变化,得到count脉冲,在FPGA中计数,即可得到编码器输出的脉冲数,经过计算就可以得到电机一定时间内实际走过的路程或者单位时间内的速度。

本系统主要在FPGA中编程实现对编码器的硬件解码。主要程序如下:

if(shift_a==2’b01)

begin

if(b)

cnt<=#2cnt-1’b1;

else

cnt<=#2cnt+1’b1;

end

elseif(shift_a==2’b10)

begin

if(b)

cnt<=#2cnt+1’b1;

else

cnt<=#2cnt-1’b1;

end

elseif(shift_b==2’b01)

begin

if(a)

cnt<=#2cnt+1’b1;

else

cnt<=#2cnt-1’b1;

end

elseif(shift_b==2’b10)

begin

if(a)

cnt<=#2cnt-1’b1;

else

cnt<=#2cnt+1’b1;

其中,cnt为十六位寄存器,shift_a=2’b01和shiftb=2’b01分别表示A和B出现上升沿,同理如果是等于2’b10则表示下降沿。电机编码器硬件解码程序仿真模拟后效果如图3所示。图中number为FPGA计算所得的编码器输出脉冲数。

2.2脉冲控制实现运动过程

利用脉冲控制电机速度即利用脉冲频率决定电机速度。这种方法能够得到较高的运行精度,适用于三坐标机电机控制系统。首先,上位机给定运行速度,命令传到单片机,单片机进行计算,获得单位脉冲周期内需要时钟数,再将数据传入FPGA,由其相应模块处理。FPGA中相应的处理模块实现的基本原理是:根据单片机给出的时钟数进行判定。程序开始运行,开始计数周期,时钟数目不断累加,当累加数目到达单片机给定值的时候完成一个计数周期。然后计数器清零,重新开始计数,输出信号状态翻转。程序如下所示:

if(cnt>=currentSpd)

begin

puls<=~puls;

cnt<=25’h1;

end

else

cnt<=cnt+1’b1;

其中cnt为计数器,currentSpd为单片机计算所得的时钟数,puls为输出脉冲。电机运动加速的过程就是一个脉冲频率逐渐加大的过程,也就是说单位周期内时钟数量逐渐增加的过程。相应的减速过程与之相反。匀速过程则是一个以给定频率保持不变的运动过程。下图便是一个匀速、减速的仿真结果。

2.3限位和解除限位的方法

最后讲述限位及其解除方法。在电机控制过程中应用限位是一种减少事故发生的有效方法。限位功能的实现需要由限位开关实现。限位开关按其检测方式可分为接触式(行程开关)和非接触式(接近开关)。[7]本系统采用非接触式。接近开关式一种非接触式检测,当运动的金属物体接近开关的感应面而达到动作距离时,便无接触无压力的自动发出检测信号,用于驱动器,也可以将其输出信号送入控制单元,以控制系统动作。[8]电机运行过程中,如果运动轴到达限位开关,即产生限位信号,信号传到控制电路,FPGA接收限位信号,做出处理后发出停止前进信号传给驱动器,驱动器控制电机停止,避免发生碰撞危险。一旦出现限位,前进命令即被禁止,电机只能带动运行轴反方向运行,在运行轴反向运动同时单片机监测FPGA测得编码器反馈的位移值,如果判断运行轴反方向运动的位移值达到安全值,便认定限位解除,电机运行恢复正常状态。

3、总结

本文较为详细的介绍了一种基于FPGA的三坐标测量机电机控制系统。实现了较为精确的电机运行控制,实现了运行状态监测和限位,运行过程中遇到危险时能够及时停止,运动整体的安全性有了很大保障。

上一篇:超声波探伤仪保养

下一篇:基于PCI总线集成电路测试仪接口设计

推荐阅读最新更新时间:2024-03-30 22:50

嵌入式系统软硬件协同设计教程:基于Xilinx Zynq-7000 (符意德)

嵌入式系统软硬件协同设计教程:基于Xilinx Zynq-7000 (符意德) 控制系统计算机辅助设计 — MATLAB语言与应用

控制系统计算机辅助设计 — MATLAB语言与应用

京公网安备 11010802033920号

京公网安备 11010802033920号