0 引言

PCB在焊接完成后,需要对其元器件进行测试,传统的方法是将其焊离PCB板后测试,但该方法不仅麻烦、效率低,并且容易损伤电路板而极不实用;另一方法就是人工结合机器进行测试,但这需要测试人员有一定的经验,也给测试带来了一定的不确定性,使得测试结果的精准度无法达到现代电路板的可靠性要求。所以,本文研究了一种可行的、简单实用及高精度的电容在线测试电路。另外,随着EDA技术的快速发展,FPGA以其高集成度、高可靠性及灵活性等特点正在快速成为数字系统开发平台,在多种领域都有非常广阔的应用前景。本设计结合上述两特点,设计了一种基于向FPGA内植入Nios II嵌入式软核作为控制器的电容在线测试电路。

1.测试原理

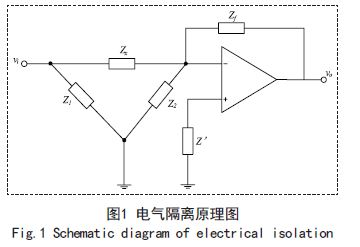

在线测试的基本思想是应用电气隔离技术,将被测元器件在电气上和与其相连的元件隔离,进而一一检测PCB板上的每一个元件。隔离方法如图1所示。

设待测元件为Zx,周围与之相连的元件阻抗等效为Z1、Z2,并将其另一端与测试电路同地。因为运放正向输入端接地,根据“虚地”原则,Z2两端等电位,都为地,即Z2被隔离;另外Vi为理想电压源时,内阻为零,Z1可视为电压源的输出负载,不影响Zx上电压降,即Z1也被隔离。即:

可见,只要确定输入,测得输出结果,就可计算出被测元件的大小。

2.电容测试电路的硬件设计

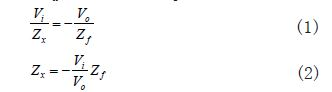

电容在线测试的硬件电路如图2所示。

R2、C1和U1共同构成一个反向积分器,为减少运放振荡的可能性,所以采用反向输入。R1的作用是使有内部相位补偿的运放开环特性与积分电路的频率特性相同,保证一定频率范围内开环增益与频率无关。Header2为被测电容的接入插槽。

Z1、Z2是与被测电容相连的干扰阻抗。被测电容同U2和R8-11一起构成微分电路。小阻值R3起限制输入电流的作用,亦即限制了R8-11中的电流。小容量C2起相位补偿作用,提高电路的稳定性。

另外,在器件的选择上,运放选用LM318,对于C1和C2,应选用绝缘电阻大的薄膜电容,不宜用铝电容或钽电容,本设计选用的是聚丙烯电容。

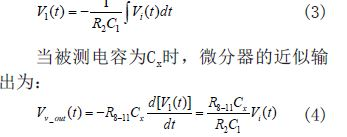

当Vi为一正弦信号时,积分器的输出为:

可见,在正弦信号的激励下,R8-11选择合适,就能得到正比于被测电容Cx的输出电压Vv_out,继而可以算出被测电容值。

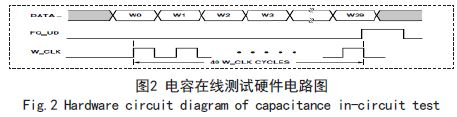

3.信号源电路

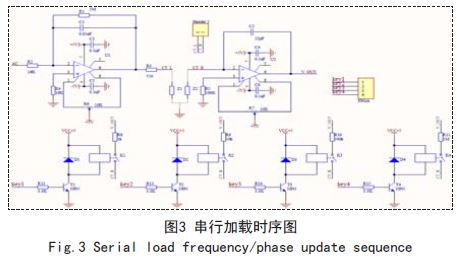

电容测试需要在测试电路输入端加交流信号,并且要求频率可调。本文采用DDS专用芯片AD9850进行交流信号源的设计。AD9850内部有40位控制字,其中32位用于频率控制,5位用于相位控制,1位用于电源休眠控制,2位用于选择工作方式。这40位控制字可以通过并行或串行方式接入到控制器FPGA,本文采用串行装载控制字,以节约I/O口,图3为控制字的串行加载时序图。

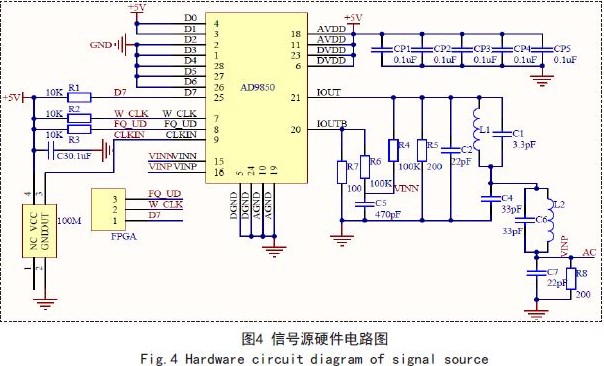

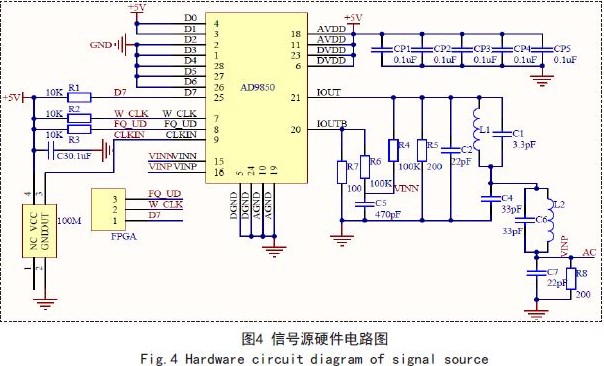

串行输入方式,在W_CLK上升沿把数据位D7的一位数据串行输入,当输入40位后,用一个FQ_UD脉冲即可更新输出频率和相位。图4为DDS硬件电路图。

其中,D0~D7为八位数据输入端口,给内部寄存器装入40位控制数据,本文采用串行输入,所以只用到D7位与FPGA相连;CLKIN为外部参考时钟输入,本设计采用100M外部时钟输入;W_CLK为字输入信号,上升沿有效;FQ_UD为频率更新控制信号,时钟上升沿确认输入数据有效;VINP和VINN分别为内部比较器的正负输入端;IOUT为内部DAC输出端;IOUTB为“互补”DAC输出端;AVDD和DVDD采用+5V供电。IOUT输出信号经过滤波器后作为测试电路的激励信号。

4.测试结果与结论

经过上述系统设计,试验测得的结果如表1所示。

结果中*表示数据不停变化或者结果超出量程。

通过上述实测值与标准值的比较可以看出本文设计的由FPGA控制的电容在线测试系统具有多量程自动选择,测试精度高,使用方便等特点,测试范围达到0.01μF~3μF.经理论分析和试验证明,该设计具有很强的实用性和可靠性。

关键字:FPGA 电容在线测试

引用地址:

基于FPGA的电容在线测试系统设计

推荐阅读最新更新时间:2024-03-30 23:21

基于FPGA和STM32的FSMC通信

1、FSMC简介:FSMC即灵活的静态存储控制器,FSMC管理1GB空间,拥有4个Bank连接外部存储器,每个Bank有独立的片选信号和独立的时序配置;支持的存储器类型有SRAM、PSRAM、NOR/ONENAND、ROM、LCD接口(支持8080和6800模式)、NANDFlash和16位的PCCard。 2、在设计中将FPGA当做SRAM来驱动,使用库函数来实现FSMC的初始化配置代码如下: //初始化外部SRAM void FSMC_SRAM_Init(void) { FSMC_NORSRAMInitTypeDef FSMC_NORSRAMInitStructure; //定义FSMC初始化的结构体变量 FS

[单片机]

基于FPGA的USB3.0 HUB设计方案

USB总线是目前最为成功,应用最为广泛的外设接口。随着时代的进步和发展,电子产品、手持设备、超大容量的高清视频设备以及千万像素的数码相机等设备的需求越来越高,USB接口规范也需要相应地进行不断地更新和升级。USB3.0的最高理论速度达到了5Gbit/s,向需要更大电力支持的设备提供更好的支持和电力供应,它在USB2.0的基础上增加了新的电源管理功能,采用全双工数据通信,提供更快的传输速度,并且向下兼容USB2.0和USB1.1设备。USB体系主要包括三个部分:主机,设备和物理连接。主机通常是PC或者主机控制器;设备是指常用的U盘、带USB的摄像头、相机等设备;物理连接就是通常用的传输线,在USB3.0系统中,采用了对偶单纯形四

[电源管理]

RS通信编码器的优化设计及FPGA实现

引言 Reed-Solomon码首先是由Reed和Solomon两人于1960年提出来的,简称为RS码。这是一类具有很强纠错能力的多进制BCH码,既能纠正随机错误,也能纠正突发错误,也是一类典型的代数几何码。RS码一直以来都是国际通信领域研究的热点之一。 本文以战术军用通信系统的首选码RS(31,15)码为例,对生成多项式进行了优化,并采用查表法的原理极大地提高了编码器运算数据的能力,缩短了运算周期,最终利用VHDL语言编译,在FPGA中实现,得到了正确的RS编译码。 1 RS编码原理 能纠正t个错误的RS(n,k)码具有如下特性: 码长:n=2m-1符号或m(2m-1)比特;信息码元数:k=

[嵌入式]

两大两小厂商或易主或易“容” FPGA将何去何从?

如果说“变”是历史的主调,那对于FPGA业者来说,变化显然来得太快了。 Intel(英特尔)以167亿美元现金收购Altera成为旗下PSG事业部,成其物联网云管端大战略的重要一环;另一巨头赛灵思被高通收购的消息不绝于耳;继Lattice(莱迪思)以约6亿美元囊括Silicon Image之后,去年11月有中资背景的基金Canyon Bridge以13亿美元收购莱迪思;而业界亦在盛传Skyworks要将Microsemi收入囊中,以扩展业务领域。“两大两小”的FPGA厂商或易主或易“容”,背后的深意是什么?置身潮流之中的FPGA将何去何从? 加速向数据中心和AI渗透 我们看到,自收购之后,Intel在一年时间内在不断加强F

[嵌入式]

多节点大容量FPGA系统的远程升级方法

引言 多节点系统,在目前的很多电子系统应用场合都可以看到。这种多节点系统由于具有结构可扩展性、功能配置的灵活性以及便于查找故障节点等良好的可维护性得到了越来越广泛的应用。通常,多节点系统各个节点的主要硬件构成有很大的相似性。特别是近年来, FPGA这个强大的平台让多节点系统各个节点的硬件构成拥有了更广泛的通用性。尤其是随着IP核技术的推广,再加上一些功能强大的CPU核的出现,如Xilinx公司提供的PicoBlaze和MicroBlaze等,使得目前的许多系统的主要功能都可以由大容量的FPGA实现,而无需再使用比较昂贵的高性能微处理器。 对于节点系统,这将大大降低系统成本。对于由大容量FPGA构成的多节点系统,系

[单片机]

安富利电子元件部率先在亚洲举办Xilinx SpeedWay设计研讨会

吸引了10个市场23个城市的1200余人参加,超过预期水平 北京,2007年3月12日 - 安富利公司 (NYSE: AVT) 旗下领先电子元件分销商安富利电子元件部亚洲区(Avnet Electronics Marketing Asia) 率先在亚太地区举办了一系列Xilinx SpeedWay设计研讨会,取得了引人注目的成效,吸引了众多的参与者。这一系列研讨会包括80多次课程,在10个主要市场的23个城市先后举办,旨在为想用Xilinx现场可编程门阵列(FPGA)进行嵌入式处理、串行连接和高性能数字信号处理(DSP)的工程专业人士提供培训。 安富利电子元件部是唯一为Xilinx客户在全球举办研讨会的分销商。Sp

[焦点新闻]

FPGA为你免除微控制器停产的后顾之忧

汽车制造商收到了这样一张通知,被告知投资多年开发的,原本计划还将生产10年的微控制器将要停产,而自己还正在使用这款器件,没有什么比这再糟糕的事了。在过去几年里,半导体供应商在整合和削减产品线时,有几款曾经流行一时的微控制器和 微处理器 已被要求停产。 在过去,受到影响的制造商有两个选择:要么停产前一次性购买;要么重新设计产品。一次性购买会造成资金积压的问题。至于重新设计,如果只是单纯的线路板布局调整来支持不同的部件还算简单,但要选择一个新的微控制器系列则需要花费大量的软件编写和测试时间。

选择不同的微控制器系列时,软件兼容性是主要的障碍。大多数公司在软件的开发,测试和验证方面已经做了大量的投入。

[嵌入式]

基于FPGA的超高速雷达住处实时采集存储系统

摘要:采用服务器作为采集主控设备,利用多个硬盘组成磁 盘阵列作为存储设备,并制作了一块基于FPGA的超高速雷达信号采集PCI卡。系统以FPGA为采集的核心控制芯片,并在FPGA内部实现了64位/66MHz的PCI接口逻辑,无需专用接口芯片,简化了电路板设计,提高了系统的灵活性。该系统数据传输总速率可高达528MB/s,实时流盘速度可达150MB/s,存储容量可扩展至1000GB以上。

关键词:FPGA 超高速 实时 数据采集 数据存储

在超高速数据采集方面,FPGA(现场可编程门阵列)有着单片机和DSP所无法比拟的优势。FPGA时钟频率高,内部时延小,目前器件的最高工作频率可达300MHz;硬件资源丰富,单片集成的可用门数达

[应用]

嵌入式系统软硬件协同设计教程:基于Xilinx Zynq-7000 (符意德)

嵌入式系统软硬件协同设计教程:基于Xilinx Zynq-7000 (符意德) 零基础学电子与Arduino:给编程新手的开发板入门指南

零基础学电子与Arduino:给编程新手的开发板入门指南

京公网安备 11010802033920号

京公网安备 11010802033920号