引言

Reed-Solomon码首先是由Reed和Solomon两人于1960年提出来的,简称为RS码。这是一类具有很强纠错能力的多进制BCH码,既能纠正随机错误,也能纠正突发错误,也是一类典型的代数几何码。RS码一直以来都是国际通信领域研究的热点之一。

本文以战术军用通信系统的首选码RS(31,15)码为例,对生成多项式进行了优化,并采用查表法的原理极大地提高了编码器运算数据的能力,缩短了运算周期,最终利用VHDL语言编译,在FPGA中实现,得到了正确的RS编译码。

1 RS编码原理

能纠正t个错误的RS(n,k)码具有如下特性:

码长:n=2m-1符号或m(2m-1)比特;信息码元数:k=n-2t符号或mk比特;监督码元数:n-k=2t符号或m(n-k)比特;最小距离:d=2t+1=n-k-1符号或m(n-k+1)比特;最小距离为d的本原RS码的生成多项式一般为:

令信息元多项式为:

监督多项式为:

则码多项式为:

式中:Q(x)是g(x)整除C(x)所得的商式。所有这些原理都与二进制循环码一样,不同的仅在于运算方法。对于二进制码,码多项式各项系数只能取0或1,多项式的加减乘除是模二运算,是定义在GF(2)域上的多项式。现在码多项式各项系数可以取q=2m种不同的值,应当是定义在GF(2m)域上的多项式。[page]

2 生成多项式的优化

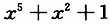

以RS(31,15)为例,n=31,k=15,可纠正错误数为t=(n-k)/2=8;以 为本原多项式,可得到GF(25)上的元素如表1所示。

为本原多项式,可得到GF(25)上的元素如表1所示。

一般的生成多项式为:

则码字多项式以 为零点。

为零点。

由于注意到:

[page]

[page]

3 RS编码器的设计

在GF(2m)域上的加法运算实际上就是每位作异或运算,由异或门组合而成即可。

由于优化了生成多项式g(x),这里只需要在ROM中存入 的乘法表即可。

的乘法表即可。

由加法模块和乘法模块组成的一级模二运算电路如图1所示。

利用ISE9.0仿真软件得到的运算一级模二运算的仿真图如图2所示。

生成的一级模二运算模块如图3所示。

[page]

[page]

依次连接多个模二运算模块,进行一步步模二运算,得到余数多项式的系数,即为RS校验码。图4为当信息码字为M时的RS编译结果。

可看到此时:

点击看原图

4 FPGA实现

通过RS编码后的数据为5×31的矩阵,形如;

将5行数据交织编码,交织度为I=5,得到(ao bo co do eo a1 b1 c1 d1 e1…a30 b30 c30 d30 e30)的形式,利用示波器从串口读出,得到波形图如图5所示。

5 结语

给出的RS编码器设计方法对生成多项式进行了优化,使得ROM中需要存入的乘法表大幅减少,模拟模二运算的步骤设计编码过程,最终烧入FPGA中,利用示波器采集到了正确的数据,证明RS编码器编码正确。本文介绍的RS编码器设计方法简单,占用资源少。

关键字:通信编码器 FPGA

引用地址:

RS通信编码器的优化设计及FPGA实现

推荐阅读最新更新时间:2024-05-02 21:11

Actel FPGA 协助LYYN AB的可视化增强技术平台大幅提高清晰度

安全性、速度、尺寸和低功耗等优势使ProASIC3 FPGA成为创新性新型视频处理平台的理想选择 Actel 公司宣布专业从事视频增强技术的瑞典LYYN AB公司已经利用Actel的ProASIC3系列现场可编程门阵列 (FPGA) 器件开发出软件和硬件视频处理平台,此举进一步显示了低功耗单芯片FPGA技术所具备的先进创新性。这个解决方案提高了视频录像的清晰度,可在雪、雾、水底淤泥和黑暗环境中提供更好的可见度。LYYN的产品主要用于遥控操作车辆 (ROV) 和飞机 (UAV) 以及便携式设备如水底摄像机和先进的监视系统等。 LYYN常务董事Andreas Ekengren 表示:“我们的创新平台是在人类视觉系统领域进行30多年

[新品]

基于STM32+FPGA的数据采集系统的设计与实现

引言 由于火控系统工作环境特殊,所需采集信号复杂多样,传统的以微控制器或PC为主的采集系统往往难以胜任。针对上述问题,提出了一种基于STM32+FPGA的数据采集系统的设计方案,该方案不仅能够完成对多路多样信号实时、精确地采集,而且具有高速信号处理和数据传输能力,具有集成化程度高、体积小、资源丰富、价格便宜等优点。 1、系统总体设计 在实际应用中,所采集的信号既有模拟信号,也有数字差分信号,并且有多通道、串并混合、数据量大等特点。为了满足需求,本文设计了图1所示的数据采集系统,它能根据需求进行6路±10V模拟信号,18路数字差分信号的采集、处理和实时传输。系统采用STM32+FPGA的组合方式,FPGA为ALTER公司的EP1

[单片机]

莱迪思新的混合信号设计软件简化了平台管理设计

莱迪思半导体公司(NASDAQ: LSCC)今天宣布推出PAC - Designer®混合信号设计软件6.1版本,更新支持莱迪思的Platform Manager™、Power Manager II 和 ispClock™器件。现在用Platform Manager器件进行设计的用户将能够访问今天宣布的Lattice Diamond® 1.3软件设计环境。PAC – Designer 6.1和Diamond 1.3设计软件工具的整合将使Platform Manager产品成为实现更先进的数字设计的选择。一个自动化的模拟环境是设计软件整合的主要优势,而以前Platform Manager设计人员没有这样的环境。 莱迪思器

[嵌入式]

比较ARM,AVR,MSP430,Coldfire,DSP,FPGA

1 我以为这样比没有意义,做嵌入式系统最大特征是 嵌入 二字,也就是说你的控制系统是嵌入于你的控制对象之中,所以首先是服从于对象的需求和特征,脱离对象空论谁好谁坏有何依据? 每个MCU都有其存在的价值,每个使用者的选择都有其道理,AVR开始时是以单时钟周期指令为卖点,相对于当时 12个时钟的经典51确实有优势,而且基于CMOS的特征,时钟越高功耗越大,所以它在能耗上似乎明显占优。 可随着技术的改进,51现在已经早就有了4时钟周期,2时钟周期乃至单时钟周期的芯片了,此时AVR的速度优势已不存在。 如果考虑最高时钟限制,读者可以比较一下,似乎AVR的速度还不如某些51快。 如果考虑开发成本,那就更难说了。 至于ARM,有其优势

[单片机]

技术文章—FPGA的单线聚合(SWA)优势

在电子系统中,用于连接电路板和各个模块之间的连接器不仅价格昂贵而且占据了电路板和系统的宝贵空间,并且它们还会降低产品的稳定性。 莱迪思开发了一种创新的方法,让系统架构师和开发人员使用尺寸极小的低功耗FPGA来大幅度减少板间和模块间的连接器数量,在增加系统稳定性的同时,降低了空间占用和成本。 拥有FPGA设计经验的开发者还能自定义该解决方案。即便没有FPGA设计经验,开发人员依然能够轻松快速完成部署。 优化连接 当今的绝大多数电子系统都包含两个及以上的电路板和/或模块。(除非另有说明,否则下文中的术语“电路板”或“板”将默认包括“模块”。) 对于系统设计师而言,经常面临的问题就是连接电路板进行数据传输。常见的解决

[嵌入式]

BBC R&D采用赛灵思FPGA设计全新摄相机后背

赛灵思公司(Xilinx, Inc.)和 BBC R&D在美国广播电视设备展 (NAB) 共同展出一种能够通过互联网协议 (IP) 网络传输专业质量视频的原型摄像机后背(Stagebox)。BBC R&D Stagebox 可以安装在任何广播质量级摄像机的背面。由于赛灵思的现场可编程门阵列 (FPGA) 中能够集成更多系统功能,因此用一根网线(光纤或 6 类线)即可取代昂贵而又繁杂的 SDI/音频/对讲和辅助设备连线。该小型设备可通过 IP 网络将视频网络连接到远程制作场所和演播室。 BBC R&D Stagebox: BBC R&D 的 Stagebox 原型摄像机后背,可以通过 IP 网络传输专业质量的视频。

[嵌入式]

Verint 解决方案助力RSPB网上社区从自建迁移到云端

客户交互企业Verint® Systems Inc.(纳斯达克股票代码:VRNT)日前宣布,Verint社区™客户英国皇家鸟类保护协会(RSPB)决定采用最新版Verint 社区*解决方案,从而实现其网上社区从自建迁移到云端的举措。该方案具备知识管理等功能,能够帮助社区成员迅速获取答案,并通过网站界面的定制化,推动自助服务在访客中的应用。 RSPB 高级数字化项目经理Keith Rangasamy表示:“我们的网上社区拥有非常忠实的用户群,他们对我们在环境保护、鸟类保护、物种恢复、野生生物以及自然保护区等方面的工作充满热情。我们希望将社区无缝迁移至云端来提升协会的客户服务水平,让RSPB的支持者享受到最佳客户体验。Verint

[安防电子]

2008新视点 低功耗是一种优势

Altera公司产品和企业市场副总裁DannyBiran 低功耗是一种战略优势 在器件的新应用上,FPGA功耗和成本结构的改进起到了非常重要的作用。Altera针对低功耗,同时对体系结构和生产工艺进行改进,使我们的高端StratixIIIFPGA能够用于高性能计算领域,而低成本CycloneIIIFPGA用于软件无线电,MaxIIZCPLD则适合便携式应用。 在生产工艺方面,Altera在很大程度上受益于和TSMC的合作。这种紧密的合作关系使Altera能够在CycloneIII中充分发挥TSMC低功耗65nm工艺技术的优势,和竞争器件相比,大大降低了功耗。我们在45nm产品开发中也取得了很大进步,将在2008年推出

[应用]

![]()

![]()

![]()

![]() 为本原多项式,可得到GF(25)上的元素如表1所示。

为本原多项式,可得到GF(25)上的元素如表1所示。

![]() 为零点。

为零点。

[page]

[page]![]() 的乘法表即可。

的乘法表即可。

[page]

[page]

汽车电子的革新与FPGA-24页

汽车电子的革新与FPGA-24页

京公网安备 11010802033920号

京公网安备 11010802033920号