提出基于FPGA设计混沌信号发生器的一种改进方法。首先,采用Euler算法,将连续混沌系统转换为离散混沌系统。其次,基于IEEE-754单精度浮点数标准和模块化设计理念,利用Quartus II软件,采用VHDL和原理图相结合的方式设计混沌信号发生器。最后,在FPGA实验系统上进行实验,在示波器上显示了混沌吸引子的相图及时域混沌信号。由于采用了基于数据选择器的面积优化方法,复用耗费逻辑资源较多的浮点运算模块,大大减少了混沌信号发生器所占用的FPGA逻辑资源。实验结果证明了该方法的有效性和通用性。

0 引言

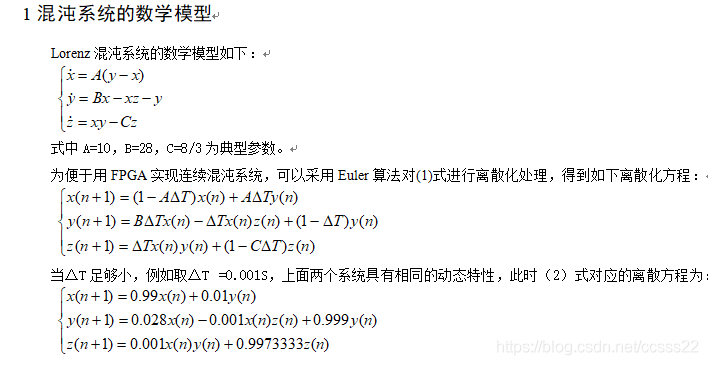

用分立元件的模拟电子电路产生混沌信号是目前最常用的方法[1,2],但元器件容易老化,系统改变不灵活,因此人们考虑能否使用数字器件(如FPGA)代替模拟元件完成相应的功能,以提高混沌保密通信系统设计的灵活性、系统的安全性和实用性。Aseeri, M.A.等人[3]提出用FPGA技术实现Lorenz混沌系统的方法。张钰等人[4]提出用FPGA技术产生多涡卷超混沌吸引子的新方法。王忠林等人[5]提出了一种基于FPGA 平台和EDA 开发工具实现混沌吸引子的方法。文献[3,4,5]所采用的均是DSP Builder技术,而不是根据IEEE-754标准用硬件描述语言来实现的,其主要缺点是不能从根本上解决时序控制等问题,在混沌同步及其在保密通信中的应用受到了限制。周武杰等人[6]提出了基于IEEE-754标准的现场可编程门阵列(FPGA)通用混沌与超混沌信号产生器设计与硬件实现的一种新方法。该方法具有通用性强的优点,并且从根本上解决了时序控制问题。但该方法中,浮点运算器模块的编程难度较高而且混沌系统占用FPGA逻辑资源较多。本文在文献[6]的基础上做了两点改进:(1)利用QuartusⅡ提供的浮点乘法器和加/减法器的兆功能函数,自定制出满足设计要求的浮点运算器模块,无需编程,减低了设计难度,提高了设计效率。(2)采用了基于数据选择器的面积优化方法,复用耗费逻辑资源较多的浮点运算模块,基于Altera EP1C3T144C8芯片(仅含有2910个逻辑单元)成功设计并实现了Lorenz、Chen、蔡氏混沌信号发生器。方便起见,本文以Lorenz混沌信号发生器设计和实现为例进行说明。

IEEE-754单精度浮点数格式[7]为32位,如图1所示。

图1 单精度浮点数格式

其中,第31位是符号位(S),第30至23位是8位的阶码(E),第22至0位是23位的尾数(F),偏移值为127,尾数有一位隐藏位。对于规格化数,0 (3)式中常数的十进制格式与IEEE-754单精度格式之间的对应关系如表1所列。 表1系统参数的十进制格式与单精度格式的对应关系 根据(3)式,用FPGA技术设计Lorenz混沌系统的主要设计理念在于将整个系统划分为若干个基本功能模块,主要包括浮点乘法器、浮点加/减法器、数据选择器、数据分配器、时序控制模块和数值转换模块等主要模块。现对其作简要分析。 3.1 浮点乘法器和浮点加/减法器 由(3)式可知,欲实现Lorenz混沌系统,离不开浮点乘法器和浮点加/减法器。利用QuartusⅡ提供的浮点乘法器和加/减法器的兆功能函数,可自定制出满足设计要求的浮点运算器模块,无需编程,简单易行,减低了设计难度,提高了设计效率。 浮点乘法器和浮点加/减法器被存放在QuartusⅡ软件的安装目录下的altera/72/quartus/libraries/megafunctions/arithmetic文件夹中,其名称分别是altfp_mult和altfp_add_sub。使用者可通过MegaWizard向导,生成实际可用的电路模块,并定义好该兆功能函数的各项参数。本设计中,浮点乘法器和浮点加/减法器均采用IEEE-754的32位单精度浮点数格式,输出反应时间均为10个clk周期,分别占用1399和697个逻辑单元。 3.2 数据选择器 由(3)式可知,进行一次完整的迭代计算,需做8次浮点乘法运算(因为0.001x(n-1)只需计算一次)以及4次浮点加法或减法运算。此外,因为Lorenz混沌系统的变量x∈(-20,20),需将其加上某个常数(如20)变为非负数,以便于单极性DA转换器输出模拟信号,所以还需做一次加法运算。显然,若不经优化,仅浮点运算器将占用1399×8+697×5=14677个逻辑单元。 为减少了FPGA芯片逻辑资源的使用量,同时也降低芯片的功耗,本设计采用了基于数据选择器的面积优化方法。其主要思想是利用速度的优势换取面积的节约,在系统工作频率允许的情况下,针对数据通路中耗费逻辑资源比较多的模块,通过多路选择的方法进行复用,以减少该模块的使用个数,达到减少资源使用,优化面积的目的。 本设计正是基于上述面积优化思想,采用了4个32位8选1数据选择器来复用浮点乘法器和浮点加/减法器各一个,最终基于Altera EP1C3T144C8芯片(仅含2910个逻辑单元)成功实现了Lorenz混沌系统。 3.3 数据分配器 数据分配器与数据选择器的功能正好相反,它用于对浮点乘法、浮点加/减法运算结果进行分配,使其分配到相应的数据寄存器进行寄存。虽然QuartusⅡ软件没有现成的数据分配器模块,但是可以通过VHDL编程自行设计实现。 3.4 时序控制模块 时序控制模块为浮点乘法器、浮点加/减法器、数据选择器、数据分配器等模块提供时序控制信号,以协调各模块有序工作。 时序控制模块采用有限状态机编程实现,由13个状态组成,为保证有足够的时间完成浮点运算,每个状态保持时间为11个clk周期。编程时,最好采用将状态寄存器、次态逻辑和输出逻辑在一个进程里描述的单进程状态机,这样输出信号被锁存后由时序器件同步输出,能够很好地改善毛刺现象。 时序控制模块的时序仿真结果如图2所示。 图2 时序控制模块的时序仿真结果 图2中, clk为时钟输入信号,reset为复位输入信号,其余为输出信号,其中sel为数据选择器和数据分配器的选择信号,mul为浮点乘法器使能信号,clk0~clk12为13个32位数据寄存器的时钟信号。由图可见,输出信号没有出现任何毛刺。 3.5数值转换模块 FPGA仅能输出数字信号,必须外接数模转换器才能实现数字信号到模拟信号的转换。本设计中使用的是10位的DA转换器THS5651。数值转换模块用于将32位单精度浮点数转换成10位的数字量,只有这样FPGA才可以和THS5651相连。 (3)式所描述的Lorenz混沌系统的状态变量x∈(-20,20),z∈(0,50)。为便于单极性DA转换器输出模拟信号,需将Lorenz混沌系统的状态变量x加上20,记为x’,则x’,z∈(0,50),其32位单精度浮点格式的阶码最大值应为10000100。 数值转换模块采用VHDL编程实现,其输入datain(31downto 0)与输出数据dataout(9 downto 0)的对应关系如表2所示。 表2 32位浮点数与10位数字量的对应关系

上一篇:MATLAB制作mif文件——正弦信号发生器2

下一篇:AD9833数字信号发生器模块

推荐阅读最新更新时间:2024-11-06 15:07

- 使用 Microchip Technology 的 MIC2012-1PCQS 的参考设计

- EFR32MG21 USB Stick

- 超级电容均压板(BW6101)已经测试

- 使用 Analog Devices 的 LT1171HVCQ#PBF 的参考设计

- LTC3265IDHC 来自单个 12V 输入的低噪声 ±15V 输出的典型应用电路

- PC性能监视器 Phat-Stats ili9341 TFT

- EM35x using Skyworks SE2432L

- LT3975 的典型应用 - 具有 2.7uA 静态电流的 42V、2.5A、2MHz 降压型开关稳压器

- LT8331IMSE 4.5V 至 80V 输入、12V SEPIC 转换器的典型应用电路

- VRP1-30E1电源模块转接板

从零开始学CPLD和Verilog HDL编程技术_通过实践的方法让初学者轻松学会CPLD系统设计技术

从零开始学CPLD和Verilog HDL编程技术_通过实践的方法让初学者轻松学会CPLD系统设计技术 基于Altera FPGA器件&Verilog HDL语言

基于Altera FPGA器件&Verilog HDL语言 控制系统计算机辅助设计 — MATLAB语言与应用

控制系统计算机辅助设计 — MATLAB语言与应用

京公网安备 11010802033920号

京公网安备 11010802033920号