电子示波器是最受欢迎的电信号测量工具,目前数字存储示波器的实时带宽超过10GHz,取样数字示波器的等效带宽达到100GHz,在实验室、车间、现场都有各种电子示波器为电信号测量提供数据。根据电子示波器的基本原理可分为模拟和数字两大类。由于模拟示波器在电路结构上比数字示波器复杂,带宽1GHz以上的电子示波器全部是数字示波器就不难理解了。当带宽超过10GHz时,取样数字示波器又具有电路结构最简单的优势,除了取样门要求最高带宽之外,其它都是低速电路,因而较易获得100GHz的等效带宽。

带宽1GHz以上的数字存储示波器和等效带宽10GHz以上的取样示波器,它们的单台售价相当昂贵。针对特定应用往往仅使用到某些频率和功能,此时,根据被测对象构建用户定制的数字存储或取样示波器是可取的方法。本文提供有关的关键器件和电路都是近年的新产品。

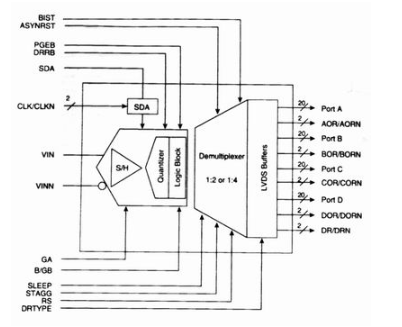

图1 取样率2GS/S的ADC芯片的结构框图

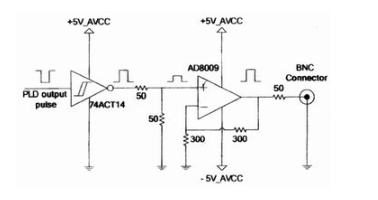

图2 双管式半桥式取样头电路

数字示波器的关键器件

数字存储示波器的关键器件——输入前端模/数转变器,通常是测量仪器公司自行设计和专用的高速集成电路,不供市售,例如TeK公司用在TDS5000等系列使用的带宽500MHz以上的ADC,由TeK和IBM共同开发制造,成本很高,只供维修时更换。直到今年Atmel公司推出AT84AS系列高速ADC,才有带宽1GHz,取样率2GS/S,分辨率10位的产品可供使用。现在,电子应用工程师可购买到高速高精度的ADC,构建数据采集系统、数字存储示波器、自动测试系统、直接射频转换器等高频电路。Atmel供应的AT84AS系列,目前有两个型号:AT84AS003和AT84AS004,前者的取样率1.5GS/S,后者的取样率2GS/S,两者完全兼容,AT84AS004的主要特征为:

·最高取样率-2GS/S

·最高分辨率-10位

·模拟输入电压和阻抗-500mv,100Ω(差分)、50Ω(单端);

·模拟输入带宽-3.3GHz

·1GHz的高频特性—有效位数7.8位,信噪比51dB,无杂波动态范围-55dB,

·调节功能-ADC增益,取样延迟,数据有效输出,超量程指示输出,1:4多工信号输出。

·供电电压—-5V,-2.2V,3.3V,2.5Vp,功率耗散6.5W

·装封—-EBGA317,25×35mm

·工作温度-0℃~90℃(民用级)-20℃~110℃(工业级)

AT84AS004芯片的结构框图如图1所示,从图1可见,输入信号Vin经取样保持电路S/H,送入量化器和逻辑电路,在时钟输入CLR,取样延迟调节SDA、图形发生器有效位PGEB、复位脉冲DRRB作用下实现A/D转换过程。获得的A/D数据输出经解多路复用器DMUX和低压差分缓冲级LVDS放大,形成4路输出端口A、B、C、D,4组输出的10位数字信号供存储器、DSP等作数据处理使用。芯片的调节信号还有内建自测试BIST,异步复位ASYNRST,增益调节GA,二进制和灰度码选择B/GB,休眠状态SLEEP等。

AT84S004芯片是目前市售频率指标最高的ADC。首先是取样率达到2GS/S,模拟输入带宽是3.3GHz。按取样原理可知,ΔF≤Fs/2即实时带宽应小于/等于取样率Fs。该芯片的Fs=2GS/s,求得△F=1GHz,即第一奈奎斯特区处在1GHz以下,第二奈奎斯特区扩展到2GHz。为避免产生波形混淆,数字存储示波器只使用第一奈奎斯特区,但是,双频通信应用时,可进入到第二奈奎斯特区,因为需为更宽的输入带宽。其次,在1GHz下的有效位数是7.8位而不是10位,由于时钟频率提高和电压比较器电平不稳,高频的分辨率会下降,从10位变成7.8位。大部分市售数字存储示波器的分辨率是8位。在高频时会低于7位。还有,芯片提供1:2和1:4的多工数字输出,对于后端数据处理非常有利,可以使用时钟较低的闪存和DSP,降低电路成本。

Atmel公司的AT84AS系列TDC仍在发展中,CMOS芯片的时钟频率可达到5GHz,表明该系列的取样率还有提高的潜力,Atmel今年已连续推出1.5GS/S和2GS/S两种ADC。Maxim公司的MAX108是8位分辨率和1.5GS/S的ADC,同样适用于数字存储示波器。

取样示波器的关键器体

取样示波器的关键器件是取样头,在原理上并非数/模转换过程而是开关过程。如果开关脉冲宽度用τ表示,等效带宽用ΔF表示,则求得ΔF=a1/τ,式中α是与开关脉冲波形有关的常数。例如,当τ=0时,ΔF =∞,亦即,开关脉冲宽度趋于零时,等效带宽趋于无限大。一般假设开关脉冲是钟形函数,此时,作为估算可取ΔF =0.35/τ,当τ=3.5ps,求得ΔF=100 GHz。

取样门电路可用桥式电路,通常采用如图2所示的双管半桥式开关电路。当输入的+LO和-LO驱动脉冲加到反向偏置的快速开关二极管对,+L0和-L0驱动脉冲分别由2PS微带线短路,产生1PS级的开关脉冲,并且对被测信号RF取样。取样获得的信号样品瞬间电荷保持在Chold电容对上,将取样电荷作处理和在慢速时间上对样品重建,即完成顺序取样的显示过程。由此可见,取样示波器在取样门实现高频高速的开关变换后,后端的信号处理可在低频低速下重建。如果后端采用数字处理,就是取样数字示波器,采用模拟处理,就是(模拟)取样示波器。

取样门的电路元器件不多,测量仪器公司按微波电路制成在陶瓷片上,密封在金属外壳内,输入RF信号和取样脉冲由小型同轴接头连接,与数字存储示波器的ADC芯片相似,取样示波器的高频高速取样头并无市售产品,近年来情况有很大变化,PSPL(皮秒脉冲实验室)公司供应带宽高至100GHz的取样头,使测量工程师构建取样示波器变得容易得多,也促进了取样技术的发展。图2实际上就是PSPL公司的通过式100GHz取样头,取样头具有如下的特性:

·取样孔径-3ps~35ps(在设计时固定)

·孔径抖动—《1ps(RMS),

·RF带宽—达到100GHz,

·RF输入动态范围—2Vp-p,

·RF阻抗—50Ω,可用SMA~1mm同轴接头,

·取样率—》10GS/S

·取样效率—60%

由上述指标可知,该取样头满足10GHz~100GHz等效带宽的测量,办法是调节取样脉冲的宽度,即取样孔径。改变图2中的微带线长度是最常用的方法,PSPL在这里采用更简便和灵活的高速反向阶跃二级管代替微带线,构成非线性短路传输线,达到取样脉冲宽度连续可调和极快速的上升边沿。取样率达到10GS/S同样是过去的取样头未曾具备的指标,传统电路采用雪崩三极管产生阶跃边沿的脉冲,再由阶跃恢复二极管整形获得10PS级的取样脉冲。这种电路的最高工作频率受雪崩三极管要进入饱和区的限制,只能在1MHz以下的重复频率运行。PSPL使用级联非饱和放大器电路将方波脉冲整形,得到高重复频率的阶跃脉冲,取样率从1GS/S提高到10GS/S。因而,PSPL的100GHz取样头既可构建等效带宽〈100的取样示波器,同时相当于取样率10GS/S的实时数字示波器。

图3 取样脉冲整形和放大电路

产生步进时基的几种方法

数字存储示波器的时基取自前端ADC时钟的倍频分频器,亦可采用后端的DAC输出,两种方法都获得时间步进扫描。取样示波器需要采用有顺序延时的取样脉冲,而不是等时的时钟脉冲,数字方法有可程控延时芯片(PDC)或时间/数字转换器(TDC),它们都有市售产品,延时增量可从10PS级至100PS级变化。后者可获得10PS级的步进延时,所谓游标延时发生器实际上是机械式游标卡尺的电学实现,游标卡尺的两块夹片的mm标度相差1/10,根据被测物体在两夹片标度测得的重合点,即可获得0.1mm的读数精度。

按游标卡尺的同样原理,利用两个振荡频率F2和F1的频差F可产生高精度的步进延时,如下式所示:

k=f2/(f2-f1)=f2/Δf 或 k=T1/(T1-T1)=T1/ΔT

式中K是两个周期的重合点,f2(T2)和f1(T1)分别是两个不同频率和相应周期,ΔT是时间差。不难看出,ΔT相当步进延时,K相当取样点数。例如,一块晶体振荡器的f1=8.000,000MHz,另一块晶体振荡器的f2=8.000,156MHz即可求得T=2.4PS,K=52,083取样点。具体电路可用通用逻辑IC构建,f2晶体振荡器经整形电路形成方波,它的上升边沿作为步进延时的参改零点,f1晶体振荡器亦整形为方波,两步频率由运算放大器作差分运算得到差频Δf,根据实际需要再作其它逻辑运算,在室温下晶体振荡器的频率稳定度优于1×10-8,两块晶体振荡器获得的总步进延时为125ns,相当于一次扫描长度。

需要步进延时的市售芯片时,可考虑ADI公司的AD9501数字程控延时发生器,从电路结构来看,它是利用DAC产生精确参考电压与斜波电压作比较,由运算放大器输出全程2.5ns至10礢扫描长度,步进延时最小10PS的可调脉冲,最高触发频率50MHz。Maxim公司的DS1023程控定时元件,电路结构是可调延时线,可配置成程控延时,脉宽调制和振荡器,步进延时分为0.25,0.5,1.0,2.0,5.0ns共5档。性能最好的MC100195程控延时芯片是安森半导体公司的产品,采用ECL工艺和面阵列封装,电路结构是多级串联门序列,具有高达1GHz的工作频率,最小步进延时20PS,最大扫描长度2.0ns还可多芯片串接,获得更大扫描长度。关于时间数字转换器的市售芯片可选产品不多,法国ESRF公司的AMS111芯片主要用于核电子测量,电路结构是可调延时线,可调步进延时范围130~160PS,动态范围2礢,工作频率80MHz,4通道输入。

最后,步进延时脉冲要整形和放大,然后送到取样头,对被测信号取样。完成开关取样的转换过程。随着RF放大器性能的进步,带宽1GHz,转换率优于6KV/礢的晶体管有多种型号,图3是一种典型的取样脉冲放大电路。

上一篇:从时域到频域-换个角度看世界

下一篇:数字示波器结构原理 数字示波器内部结构图

推荐阅读最新更新时间:2024-11-12 17:39

- AMD推出第二代Versal Premium系列产品:首款PCIe 6.0和CXL 3.1的SoC FPGA

- 红帽宣布达成收购Neural Magic的最终协议

- 5G网速比4G快但感知差!邬贺铨:6G标准制定应重视用户需求

- SEMI报告:2024年第三季度全球硅晶圆出货量增长6%

- OpenAI呼吁建立“北美人工智能联盟” 好与中国竞争

- 传OpenAI即将推出新款智能体 能为用户自动执行任务

- 尼得科智动率先推出两轮车用电动离合器ECU

- ASML在2024 年投资者日会议上就市场机遇提供最新看法

- AMD将裁员4%,以在人工智能芯片领域争取更强的市场地位

- Arm:以高效计算平台为核心,内外协力共筑可持续未来

电工电子技术实验教程

电工电子技术实验教程 控制系统计算机辅助设计 — MATLAB语言与应用

控制系统计算机辅助设计 — MATLAB语言与应用

京公网安备 11010802033920号

京公网安备 11010802033920号