目前的视频监视市场在发展过程中遇到了很多要解决的难题,包括从模拟到数字摄像机的过渡、转换到高清(HD) 视频、应用宽动态范围(WDR) 传感器,以及实现进行数据传输和控制的互联网协议(IP) 链接等。针对这些问题,本文介绍了如何采用FPGA构建IP 监视摄像机的参考设计,展示了怎样采用低成本Altera Cyclone III FPGA 构建完整的系统。

引 言

在视频监视市场领域,对更高质量视频、高分辨率以及灵活性和功能的需求促进了从模拟到数字摄像机的过渡。在定义上,高清(HD) 视频必须是数字的,因此,采用HD标准也就意味着过渡到数字传感器。HD 视频标准支持更高的帧速率和分辨率,需要H.264 等新压缩方法,促使摄像机具有更强的处理能力。

在各种照明条件( 强光和暗光、强对比度) 下都要求能够提取出所有图像内容,因此,数字摄像机采用了新一类WDR 传感器,摄像机也要求在数字域中实现动态范围压缩。摄像机中数字数据通路的另一优点是可以在摄像机内部进行“分析”处理。

IP 监视摄像机参考设计

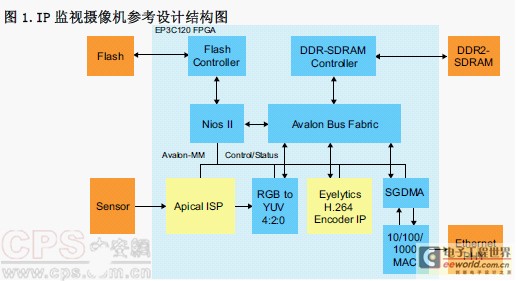

图1 所示为IP 监视摄像机参考设计的顶层结构图和硬件,它主要面向新一代HD (>1MP) WDR 传感器。IP 监视摄像机参考设计结合了Altera 以及多家合作伙伴的硬件和软件知识产权。图1.IP 监视摄像机参考设计结构图

图2 显示了参考设计的硬件平台,基于Cyclone III EP3C120 开发板。Aptina WDR 传感器像素数据被送入Apical 的图像传感器流水线(ISP)。输出数据是YUV4:2:0 格式,写入到外部DDR2 SDRAM 的帧缓冲中,它使用了Altera 视频和图像处理(VIP) 套装提供的组件。然后,使用EyeLytics 提供的内核,以H.264 格式对视频数据进行编码,支持( 在这一应用中)3 级基线/ 主要类视频流,通过以太网在远程主机上观看。散射收集直接存储器访问(SGDMA) 控制器支持Altera 三速以太网(TSE) MegaCore ?功能,将编码后的视频流通过以太网传送到远程客户端。图2.IP 监视摄像机参考设计硬件

宽动态范围传感器

Aptina MT9M033 是0.33" 720p60 WDR CMOS 传感器,主要用于监视摄像机市场。传感器和镜头组合安装在“顶板”上,通过I/O 转换板将其连接至Cyclone III EP3C120开发板。图像传感器流水线CMOS WDR 传感器没有片内图像流水线处理功能,以RAW/Bayer 格式输出图像数据,每像素为20 比特。可以采用下式来计算传感器输出的大量原始数据:20 比特/ 像素 x (1280 x 720) 像素/ 帧x 60 帧/s = >1 Gbit/s由于数据量过大,因此,很难将新一代WDR 传感器连接至监视解决方案中经常使用的ASSP。因此,FPGA 是高效处理数据的理想选择。Apical 的ISP ( 图3) 包括以下功能:

■ 去除热点像素,抑制噪声( 提供空间和时域IP 内核)。

■ 使用Apical 获奖的专利Iridix IP 内核实现单位像素高级色调映射功能

■ 高级去马赛克和颜色校正

与图4 顶部未处理的图像相比,图4 底部显示了Iridix 内核怎样从强对比度场景中尽可能多的提取出细节内容。特别是,较暗的区域并没有受到较亮区域过渡感光的影响。图4.Apical ISP 强对比度场景效应

ISP 输出可以作为参考设计的一个选项,通过Bitec DVI 输出电路板连接至CycloneEP3C120 开发板的第二个HSMC 连接器( 显示在图2 的左侧硬件中)。

视频和图像处理套装

Altera VIP 套装汇集了MegaCore 功能,设计人员可以利用它方便的开发定制视频和图像处理设计。VIP 套装含有MegaCore 功能,从颜色空间转换等简单的构建模块功能到可编程多相缩放等复杂的视频缩放功能。这些功能适合用在多种图像处理和显示应用中,例如视频监视、广播、视频会议、医疗和军事成像等。

在IP 监视摄像机参考设计中,采用了多种VIP 内核进行颜色空间转换,采用色度重新采样功能将ISP 的RGB 编码视频转换为H.264 编码器要求的YUV 4:2:0 编码输入。如图5 所示,内核连接至应用了Avalon-ST 视频协议的Avalon ?流(Avalon-ST) 接口。使用Avalon 存储器映射(Avalon-MM) 接口,Y 和C 视频分量被写入外部DDR2 存储器的帧缓冲。

在H.264 编码之前,跳过视频间隔帧,在帧缓冲写入器中,720p60 传感器帧速率被转换为720p30,而不是将其写入帧缓冲中。

视频压缩

该设计中使用的H.264 编码器( 图6) 是EyeLytics 公司提供的IP 内核,它针对监视应用进行了优化。这一内核具有很多监视功能,包括多通道支持、恒定质量速率控制、帧内/ 帧间模式、QPEL、前后关系自适应二进制算法编码(CABAC)/ 前后关系自适应长度可变编码(CAVLC),并且使用了较少的逻辑门。内核同时支持主要类和基线类。

三速以太网MAC

Altera TSE MegaCore 功能结合了10-/100-/1000-Mbps 以太网介质访问控制器(MAC)和1000BASE-X 物理编码子层(PCS),以及可选物理介质附加子层(PMA)。Cyclone IIIEP3C120 开发板包括10/100/1000 base-T 和自动协商以太网PHY,其简化千兆位介质无关接口(RGMII) 连接至TSE 功能。

Avalon 总线架构和DDR2 帧缓冲存储器采用了一块具有150 MHz 32 位数据总线的外部DDR2 SDRAM,由Altera DDR 和DDR2SDRAM 高性能II 控制器MegaCore 功能对其进行控制,它用于应用程序代码和数据存储、输入和输出帧缓冲以及H.264 编码器的中间帧缓冲。为达到时序和性能目标,Avalon-MM 总线架构是75 MHz 128 位宽。Avalon 仲裁共享功能应用于连接DDR2 存储器控制器的每一Avalon-MM 总线主机,以保证不中断的高效访问H.264 编码器的突发数据。 整个系统采用了时钟交叉桥接、定时器和并行I/O 等多种标准Avalon 组件。为简单起见,图6 并没有显示这些组件。

工具流

使用Altera SOPC Builder 工具,以完整的芯片系统(SOC) 来实现IP 监视摄像机参考设计。使用SOPC Builder,设计人员在GUI 中设定系统组件,由SOPC Builder 自动产生互联逻辑。SOPC Builder 产生定义系统中所有组件的HDL 文件,然后,顶层HDL 文件将所有组件连接起来。在Verilog HDL 中生成IP 监视摄像机参考设计,而SOPCBuilder 能够同时生成Verilog HDL 和VHDL。

ISP 和H.264 编码器可以是具有Avalon-MM 接口的SOPC Builder 组件,易于集成到Altera 具有标准外设的系统中,以及第三方IP 和设计人员自己的组件构成的系统中。SOPC Builder 含在Altera Quartus ? II 开发软件中,提供了全面的多平台设计环境,很容易满足特殊的设计需求。Quartus II 软件为FPGA 和CPLD 设计的所有阶段提供解决方案:

■ 设计输入

■ 综合

■ 布局布线

■ 时序分析

■ 仿真

■ 编程和配置

使用Altera Nios ? II 嵌入式设计套装进行软件开发。基于SOPC Builder 设计中的组件,生成电路板支持包(BSP),包括所有必须的器件驱动程序等。

软件应用

采用Nios II 嵌入式处理器来设置不同模块中的各种寄存器,同时运行RTP 堆栈,传送压缩视频。采用以太网MAC 模块来控制ISP,嵌入式处理器运行Micrium 的uC/OSII实时内核、InterNiche 技术公司的NicheStack 和RTP 堆栈,以及Altera 参考设计的视频流应用程序和网络服务器应用程序。处理器还处理ISP 的自动曝光和自动白平衡控制功能。

视频流应用程序响应H.264 编码器的中断,重新装入各种缓冲指针。重新装入功能使其能够准备要编码的下一视频帧,将刚刚编码后的帧通过以太网传送至RTP 堆栈,以便继续传输。通过网络服务器应用程序,支持ISP 进行简单的控制,使传感器在正常和WDR 模式之间切换,使能和禁止Iridix。这种控制功能具有实时显示ISP 的优势。网络服务器应用程序还支持对编码器进行配置,包括比特率和质量等,在CABAC 和CAVLC 之间进行选择。

主机软件

运行VLC 媒体播放器( 或者类似的) 的主机PC 用于查看IP 监视摄像机参考设计的流视频输出。如图7 所示,主机和EP3C120 开发套件之间需要的唯一链接是以太网电缆。

性 能

IP 监视摄像机参考设计的性能指标包括速度、延时、功耗和资源利用率。

速 度

在Cyclone III EP3C120I7 开发板上实现参考设计时,DDR 时钟频率为150 MHz,足以使用H.264 基线类或者主要类来压缩720p30 视频帧。Avalon-MM 总线架构运行在75MHz,H.264 编码器内核运行在150 MHz。DDR2 存储器控制器、Avalon-MM 总线架构以及H.264 内核通过同步半速率桥接进行连接,以减小时钟域之间的延时。Nios II 处理器和TSE 的时钟为125 MHz。采用了Nios II/F( 快速) 版的Nios II 处理器,具有8-Kbyte 指令高速缓存、8-Kbyte 数据高速缓存,并且支持浮点。

延 时

从传感器输入到ISP,直至H.264 编码器输出的延时小于两帧,它主要来自图像数据的双缓冲。在对以前的帧进行编码时总是将新输入帧写入存储器。

功 耗

参考设计总功耗包括所有的辅助模块和I/O 的功耗,达到2.7 W。表1 显示了参考设计中使用的每一主要模块的功耗。其余的700mW 来自Avalon 总线架构、颜色空间转换和参考设计的I/O 附件。

资源利用率:在Cyclone EP3C120 中实现整个参考设计时,其资源利用率为:

■ 107K 逻辑单元(LE) (90% 器件利用率)■ 410 M9K 嵌入式存储器(95% 器件利用率)■ 140 个嵌入式乘法器9 位单元(24% 器件利用率)

表2 列出了某些模块的资源利用率。

表3 列出了使用的I/O。

灵活性

基于FPGA 的体系结构非常灵活,可以进行定制,完全能够在大家都了解的标准硬件平台上实现。通过这种灵活性,可以增强和修改系统体系结构,以适应不同的系统需求。由于采用了标准HDL 来实现设计,因此,很容易提高摄像机分辨率,增加定制视频处理功能或者视频分析引擎。而且,还可以通过以太网进行远程更新。例如,把新的FPGA 编程文件发送至Nios II 嵌入式处理器,然后将文件写入闪存,从而重新配置系统或者改变传感器和ISP 设置。在单片FPGA 中集成整个IP 监视摄像机参考设计减少了芯片数量,节省了PCB 空间。不需要与外部器件进行通信,从而减少了I/O 链接,降低了动态功耗,解决了散热问题。针对个性化需求,使用不同的FPGA 图像( 例如,分辨率、帧速率和压缩选项),在一个系统设计中便能够支持多种个性化摄像机。通过纵向移植,可以在同一封装中使用不同逻辑密度的器件。而且,设计可以在任意FPGA 上实现,采用开放设计方案使设计人员能够针对最新的FPGA 进行设计,有了更新的FPGA 系列后,可以进一步提高性能,降低成本和功耗

结 论

Altera 的Cyclone III 和Cyclone IV 系列低成本FPGA 解决了目前最新IP 监视系统设计人员所面临的难题。通过IP 监视摄像机参考设计,Altera 及其合作伙伴提供了从图像采集到IP 包封的全面解决方案,使用集成在Altera SOPC Builder 工具中的系列MegaCore 功能来提供灵活的解决方案,促使产品及时面市。

上一篇:“透雾”能否成为模拟枪机的强心剂

下一篇:城市监控报警联网技术应用的新趋势

推荐阅读最新更新时间:2024-03-16 10:57

- 米尔T527系列核心板,高性能车载视频监控、部标一体机方案

- Akamai 全新视频工作流程功能强化媒体平台控制能力

- 紫光同芯推出全球首颗开放式架构安全芯片E450R 已获国密二级认证

- 品英Pickering公司携多款模块化信号开关和仿真解决方案亮相国防电子展

- 派克汉尼汾推出适用于现场监测和诊断的测量设备 Service Master COMPACT

- 连接与距离: 安防摄像头新气象—— Wi-Fi HaLow 带来更远传输距离和更低功耗

- 思特威携多款重磅产品强势亮相2023 CPSE安博会

- 双轮驱动,云天励飞推出12TOPS边缘视觉SoC

- 丰田汽车因信息泄露案接受日本行政指导 涉及241万条用户数据

- Allegro MicroSystems 在 2024 年德国慕尼黑电子展上推出先进的磁性和电感式位置感测解决方案

- 左手车钥匙,右手活体检测雷达,UWB上车势在必行!

- 狂飙十年,国产CIS挤上牌桌

- 神盾短刀电池+雷神EM-i超级电混,吉利新能源甩出了两张“王炸”

- 浅谈功能安全之故障(fault),错误(error),失效(failure)

- 智能汽车2.0周期,这几大核心产业链迎来重大机会!

- 美日研发新型电池,宁德时代面临挑战?中国新能源电池产业如何应对?

- Rambus推出业界首款HBM 4控制器IP:背后有哪些技术细节?

- 村田推出高精度汽车用6轴惯性传感器

- 福特获得预充电报警专利 有助于节约成本和应对紧急情况

【得捷电子Follow me第4期】任务源代码汇总

【得捷电子Follow me第4期】任务源代码汇总 机器人学 (蔡自兴)

机器人学 (蔡自兴)

京公网安备 11010802033920号

京公网安备 11010802033920号