摘要:结合自适应算法、CX-TB导通测试算法以及二进制计数测试序列,给出了用软件控制EPM9320LC84边界扫描链路,以输出图形并采集引脚对图形的响应,然后通过比较输出测试图形与采集测试图形的差异实现芯片I/O引脚印刷电路板故障的诊断方法。该测试图形便于实现,测试方法快捷、通用性强,诊断结果准确,故障覆盖率高。文中在以PC机作为边界扫描测试向量生成和故障诊断的基础上,对单芯片——EPM9320LC84的印刷电路板故障诊断进行了一些讨论。

关键词:边界扫描;故障诊断;测试图形

IEEE 1149.1标准规定的边界扫描技术是针对复杂数字电路而制定的。标准中的自治测试技术现已成为数字系统可测性设计的主流。在利用边界扫描技术对芯片印刷电路板进行测试时,单芯片与多芯片电路板虽有相同点,但也有不同点。因为多芯片的电路板可以将几个芯片分别作为测试向量进行发送和接收,而单芯片电路板则只需要一个集发送、接收于一体的芯片。本文在以PC机作为边界扫描测试向量生成和故障诊断的基础上,对单芯片EPM9320LC84的印刷电路板故障诊断进行了讨论。

1 EPM9320LC84的结构和性能

1.1 主要性能

EPM9320LC84是Altera公司生产的EPLD器件,它的主要性能如下:

●内含JTAG边界扫描测试电路。

●在5V电源条件下,JTAG接口可编程。

●所有的I/O均可在3.3V或5V电源下工作,并且在引脚处都有输入/输出寄存器。

●Altera MAX+PLUSⅡ 开发系统可提供软件设计支持,该开发系统可工作在486PC机、奔腾PC机、Sun SPARC工作站、HP9000系列700工作站、IBM RISC系统/6000或DEC Alpha AXP工作站上。

●利用EDIF、Verilog HDL、VHDL和其它软件可通过CAE工具(如OrCAD)提供仿真支持。

1.2 管脚说明

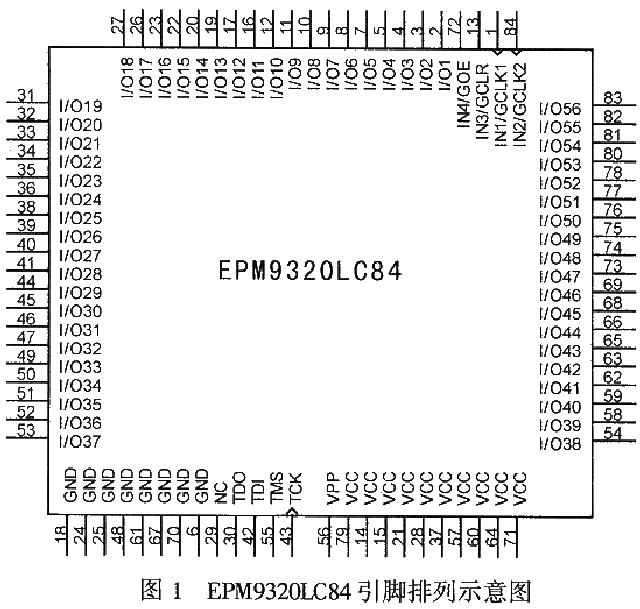

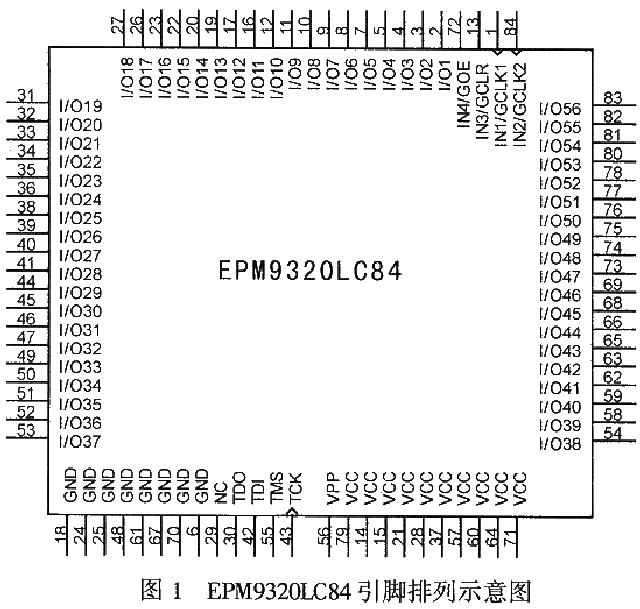

图1是EPM9320LC84的引脚图,其功能如下:

VCC、VPP:芯片电源端。

GND:芯片地端。

I/O:输入/输出引脚。

IN1~IN4:专用输入引脚。

TCK,TMS:分别为时钟测试和测试模式选择端。

:测试模式选择端。

TDI,TDO分别为测试数据输入、输出端。

其中,TCK、TMS、TDI、TDO为JTAG边界扫描接口,它们和芯片内部的边界扫描寄存器504个数据捕获寄存器,168个数据更新寄存器,一个指令捕获寄存器,一个指令更新寄存器链形成的边界扫描结构一起可用于芯片内部和外部测试。

2 测试系统配置

把ByteBlaster 下载电缆连到PC机的打印并口可实现PC机并口与JTAG接口的互连。PC机可用软件来控制边界扫描接口以完成边界扫描测试任务。

利用VC++语言可编写MFC应用程序(内容主要包括:TAP控制类、测试向量生成、发送、采集类、故障诊断类等)以达到人机交互、故障诊断、数据管理三个方面的要求。

3 数据发送与数据采集

3.1 数据发送

通过extest模式发送数据时。可在移位阶段将捕获寄存器的数据移出,同时将测试图形移入。而在更新阶段,测试图形从捕获寄存器传送到更新寄存器,再由更新寄存器驱动测试信号并将其输出至I/O引脚。对于单芯片电路板来说,无论是输入引脚,还是在引脚发送测试图形时,其控制三态均应为输出状态,即令OEJ更新寄存器为1。

3.2 数据采集

数据采集的目的是得到引脚对测试图形的响应。如果引脚正确,输出的测试图形就等于采集到的测试图形,如果引脚出现故障,两者必有差异。由于采集到的测试数据就是故障诊断的依据,所以能否正确、合理地采集到数据是数据采集的关键。单芯片电路板不像多芯片那样利用sample模式采集数据,而是仍旧利用extest模式来采集数据。

图2是利用sample模式采集数据的原理图。在捕获阶段,由OEJ和OUTJ来控制三态门状态,以使电路板上三态输入引脚为高阻状态,三态输出引脚为输出状态。由于采集的数据是引脚的实际状态,而不是引脚对输出测试图形的响应,故用sample模式不能正确地采集测试图形以用于故障诊断。

图3是利用extest模式在捕获阶段进行数据采集的示意图,图中的三态门受OEJ、OUTJ更新寄存器控制,而这两个寄存器的数值是发送测试图形时的值,三态有效。所以它所采集的数据即为引脚对测试图形的响应,可以满足采集要求。

其中,TCK、TMS、TDI、TDO为JTAG边界扫描接口,它们和芯片内部的边界扫描寄存器504个数据捕获寄存器,168个数据更新寄存器,一个指令捕获寄存器,一个指令更新寄存器链形成的边界扫描结构一起可用于芯片内部和外部测试。

2 测试系统配置

把ByteBlaster 下载电缆连到PC机的打印并口可实现PC机并口与JTAG接口的互连。PC机可用软件来控制边界扫描接口以完成边界扫描测试任务。

利用VC++语言可编写MFC应用程序(内容主要包括:TAP控制类、测试向量生成、发送、采集类、故障诊断类等)以达到人机交互、故障诊断、数据管理三个方面的要求。

3 数据发送与数据采集

3.1 数据发送

通过extest模式发送数据时。可在移位阶段将捕获寄存器的数据移出,同时将测试图形移入。而在更新阶段,测试图形从捕获寄存器传送到更新寄存器,再由更新寄存器驱动测试信号并将其输出至I/O引脚。对于单芯片电路板来说,无论是输入引脚,还是在引脚发送测试图形时,其控制三态均应为输出状态,即令OEJ更新寄存器为1。

3.2 数据采集

数据采集的目的是得到引脚对测试图形的响应。如果引脚正确,输出的测试图形就等于采集到的测试图形,如果引脚出现故障,两者必有差异。由于采集到的测试数据就是故障诊断的依据,所以能否正确、合理地采集到数据是数据采集的关键。单芯片电路板不像多芯片那样利用sample模式采集数据,而是仍旧利用extest模式来采集数据。

图2是利用sample模式采集数据的原理图。在捕获阶段,由OEJ和OUTJ来控制三态门状态,以使电路板上三态输入引脚为高阻状态,三态输出引脚为输出状态。由于采集的数据是引脚的实际状态,而不是引脚对输出测试图形的响应,故用sample模式不能正确地采集测试图形以用于故障诊断。

图3是利用extest模式在捕获阶段进行数据采集的示意图,图中的三态门受OEJ、OUTJ更新寄存器控制,而这两个寄存器的数值是发送测试图形时的值,三态有效。所以它所采集的数据即为引脚对测试图形的响应,可以满足采集要求。

4 测试算法

电路板常见故障模型有呆滞型故障、固定开路故障和短路故障。为了消除误判和混淆故障及提高诊断速度,可在算法上结合电路结构对自适应算法和CX-TB导通测试算法以及二进制计数测试序列进行改进,以对引脚全部的短路故障、呆滞故障进行完备诊断。具体步骤如下:

(1)引脚分类

电路图中的引脚可分为输入、输出、输入/输出、空闲、专用输入、地/电源、NC几类。由于专用输入引脚边界扫描结构没有更新寄存器,所以测试图形无法输出到引脚因此不能用此方法测试。而地/电源引脚、NC引脚不带有边界扫描结构所以也不能测试。故此,真正能进行测试的引脚只有前四类。可令n等于前四类引脚数目的总和。

(2)生成测试向量

按照引脚号对前四类引脚进行从小到大排序,序号为:0到n-1,然后计算log2(n+2)的值,再根据有余进一的原则算出并行测试向量个数m。为避免出现误判,可从000……1开始进行二进制计数,以形成测试向量,其行数为n,列数为m。

(3)发送测试向量

(4)采集测试结果

(5) 添加测试图形

比较测试序列与采集到的结果,确定异常行(总数W)。为避免混淆和误判故障,可进一步添加C个为全0或全1码的测试图形。

(6)故障诊断

该算法具有故障定位准确,测试周期短,测试效率高等特点。

4 测试算法

电路板常见故障模型有呆滞型故障、固定开路故障和短路故障。为了消除误判和混淆故障及提高诊断速度,可在算法上结合电路结构对自适应算法和CX-TB导通测试算法以及二进制计数测试序列进行改进,以对引脚全部的短路故障、呆滞故障进行完备诊断。具体步骤如下:

(1)引脚分类

电路图中的引脚可分为输入、输出、输入/输出、空闲、专用输入、地/电源、NC几类。由于专用输入引脚边界扫描结构没有更新寄存器,所以测试图形无法输出到引脚因此不能用此方法测试。而地/电源引脚、NC引脚不带有边界扫描结构所以也不能测试。故此,真正能进行测试的引脚只有前四类。可令n等于前四类引脚数目的总和。

(2)生成测试向量

按照引脚号对前四类引脚进行从小到大排序,序号为:0到n-1,然后计算log2(n+2)的值,再根据有余进一的原则算出并行测试向量个数m。为避免出现误判,可从000……1开始进行二进制计数,以形成测试向量,其行数为n,列数为m。

(3)发送测试向量

(4)采集测试结果

(5) 添加测试图形

比较测试序列与采集到的结果,确定异常行(总数W)。为避免混淆和误判故障,可进一步添加C个为全0或全1码的测试图形。

(6)故障诊断

该算法具有故障定位准确,测试周期短,测试效率高等特点。

5 故障诊断

由于EPM9320LC84芯片采用CMOS工艺制作,因此,它的引脚与地、电源短路分别归为呆滞于0和呆滞于1;器件引脚悬空也归为呆滞于0。其引脚互连测试图形是“与”逻辑。

具体诊断时,可比较输出测试图形与采集测试图形的差异,相同即为正常行,不同则为异常行。诊断过程如下:

●若异常行和正常行的测试向量相同,则添加测试图形令异常行并行测试向量为全0,其余行测试向量为全1,而对于发送、采集添加的测试向量,若正常行采集结果为全0,则正常行与异常行对应引脚互连。否则必有其它脚与异常行对应脚互连。

●如果异常行向量是全1,判断异常行对应引脚呆滞于1。

●如果异常行向量为全0,则可添加测试图形令所有测试向量为全1,同时发送、采集添加的测试向量,此时若异常行测试结果为全0,则异常行对应引脚呆滞于0。否则必有其它脚与该异常行对应引脚互连。

●如果两个异常行测试向量相同且为全0,则可添加测试图形以令所有测试向量为全1,同时发送、采集添加的测试向量,如果异常行为全0,则异常行对应引脚呆滞于0;如果测试结果是两行都为全1,则添加测试图形令两个异常行测试向量分别为全1和全0,其余向量为全1,再一次发送、采集添加的测试向量,如果采样结果是两个异常行为全0,则两异常行对应引脚互连;否则两异常行对应引脚无关,必有其它引脚与异常行对应引脚互连。

●如果两个异常行测试向量相同,且既非全0又非全1,则两异常行对应引脚互连。

6 结束语

利用芯片边界扫描结构,采用本文介绍的算法,不需要附加其它芯片,就能完成EPM9320LC84所有I/0引脚的印刷电路板故障诊断它所覆盖的故障包括引脚呆滞,引脚互连等。而且这种算法对多引脚互连故障也能准确诊断。其测试方法简单易行,测试时间不超过1秒,而且诊断十分准确。

5 故障诊断

由于EPM9320LC84芯片采用CMOS工艺制作,因此,它的引脚与地、电源短路分别归为呆滞于0和呆滞于1;器件引脚悬空也归为呆滞于0。其引脚互连测试图形是“与”逻辑。

具体诊断时,可比较输出测试图形与采集测试图形的差异,相同即为正常行,不同则为异常行。诊断过程如下:

●若异常行和正常行的测试向量相同,则添加测试图形令异常行并行测试向量为全0,其余行测试向量为全1,而对于发送、采集添加的测试向量,若正常行采集结果为全0,则正常行与异常行对应引脚互连。否则必有其它脚与异常行对应脚互连。

●如果异常行向量是全1,判断异常行对应引脚呆滞于1。

●如果异常行向量为全0,则可添加测试图形令所有测试向量为全1,同时发送、采集添加的测试向量,此时若异常行测试结果为全0,则异常行对应引脚呆滞于0。否则必有其它脚与该异常行对应引脚互连。

●如果两个异常行测试向量相同且为全0,则可添加测试图形以令所有测试向量为全1,同时发送、采集添加的测试向量,如果异常行为全0,则异常行对应引脚呆滞于0;如果测试结果是两行都为全1,则添加测试图形令两个异常行测试向量分别为全1和全0,其余向量为全1,再一次发送、采集添加的测试向量,如果采样结果是两个异常行为全0,则两异常行对应引脚互连;否则两异常行对应引脚无关,必有其它引脚与异常行对应引脚互连。

●如果两个异常行测试向量相同,且既非全0又非全1,则两异常行对应引脚互连。

6 结束语

利用芯片边界扫描结构,采用本文介绍的算法,不需要附加其它芯片,就能完成EPM9320LC84所有I/0引脚的印刷电路板故障诊断它所覆盖的故障包括引脚呆滞,引脚互连等。而且这种算法对多引脚互连故障也能准确诊断。其测试方法简单易行,测试时间不超过1秒,而且诊断十分准确。

引用地址:基于边界扫描的EPM9320LC84电路板故障诊断

其中,TCK、TMS、TDI、TDO为JTAG边界扫描接口,它们和芯片内部的边界扫描寄存器504个数据捕获寄存器,168个数据更新寄存器,一个指令捕获寄存器,一个指令更新寄存器链形成的边界扫描结构一起可用于芯片内部和外部测试。

2 测试系统配置

把ByteBlaster 下载电缆连到PC机的打印并口可实现PC机并口与JTAG接口的互连。PC机可用软件来控制边界扫描接口以完成边界扫描测试任务。

利用VC++语言可编写MFC应用程序(内容主要包括:TAP控制类、测试向量生成、发送、采集类、故障诊断类等)以达到人机交互、故障诊断、数据管理三个方面的要求。

3 数据发送与数据采集

3.1 数据发送

通过extest模式发送数据时。可在移位阶段将捕获寄存器的数据移出,同时将测试图形移入。而在更新阶段,测试图形从捕获寄存器传送到更新寄存器,再由更新寄存器驱动测试信号并将其输出至I/O引脚。对于单芯片电路板来说,无论是输入引脚,还是在引脚发送测试图形时,其控制三态均应为输出状态,即令OEJ更新寄存器为1。

3.2 数据采集

数据采集的目的是得到引脚对测试图形的响应。如果引脚正确,输出的测试图形就等于采集到的测试图形,如果引脚出现故障,两者必有差异。由于采集到的测试数据就是故障诊断的依据,所以能否正确、合理地采集到数据是数据采集的关键。单芯片电路板不像多芯片那样利用sample模式采集数据,而是仍旧利用extest模式来采集数据。

图2是利用sample模式采集数据的原理图。在捕获阶段,由OEJ和OUTJ来控制三态门状态,以使电路板上三态输入引脚为高阻状态,三态输出引脚为输出状态。由于采集的数据是引脚的实际状态,而不是引脚对输出测试图形的响应,故用sample模式不能正确地采集测试图形以用于故障诊断。

图3是利用extest模式在捕获阶段进行数据采集的示意图,图中的三态门受OEJ、OUTJ更新寄存器控制,而这两个寄存器的数值是发送测试图形时的值,三态有效。所以它所采集的数据即为引脚对测试图形的响应,可以满足采集要求。

其中,TCK、TMS、TDI、TDO为JTAG边界扫描接口,它们和芯片内部的边界扫描寄存器504个数据捕获寄存器,168个数据更新寄存器,一个指令捕获寄存器,一个指令更新寄存器链形成的边界扫描结构一起可用于芯片内部和外部测试。

2 测试系统配置

把ByteBlaster 下载电缆连到PC机的打印并口可实现PC机并口与JTAG接口的互连。PC机可用软件来控制边界扫描接口以完成边界扫描测试任务。

利用VC++语言可编写MFC应用程序(内容主要包括:TAP控制类、测试向量生成、发送、采集类、故障诊断类等)以达到人机交互、故障诊断、数据管理三个方面的要求。

3 数据发送与数据采集

3.1 数据发送

通过extest模式发送数据时。可在移位阶段将捕获寄存器的数据移出,同时将测试图形移入。而在更新阶段,测试图形从捕获寄存器传送到更新寄存器,再由更新寄存器驱动测试信号并将其输出至I/O引脚。对于单芯片电路板来说,无论是输入引脚,还是在引脚发送测试图形时,其控制三态均应为输出状态,即令OEJ更新寄存器为1。

3.2 数据采集

数据采集的目的是得到引脚对测试图形的响应。如果引脚正确,输出的测试图形就等于采集到的测试图形,如果引脚出现故障,两者必有差异。由于采集到的测试数据就是故障诊断的依据,所以能否正确、合理地采集到数据是数据采集的关键。单芯片电路板不像多芯片那样利用sample模式采集数据,而是仍旧利用extest模式来采集数据。

图2是利用sample模式采集数据的原理图。在捕获阶段,由OEJ和OUTJ来控制三态门状态,以使电路板上三态输入引脚为高阻状态,三态输出引脚为输出状态。由于采集的数据是引脚的实际状态,而不是引脚对输出测试图形的响应,故用sample模式不能正确地采集测试图形以用于故障诊断。

图3是利用extest模式在捕获阶段进行数据采集的示意图,图中的三态门受OEJ、OUTJ更新寄存器控制,而这两个寄存器的数值是发送测试图形时的值,三态有效。所以它所采集的数据即为引脚对测试图形的响应,可以满足采集要求。

4 测试算法

电路板常见故障模型有呆滞型故障、固定开路故障和短路故障。为了消除误判和混淆故障及提高诊断速度,可在算法上结合电路结构对自适应算法和CX-TB导通测试算法以及二进制计数测试序列进行改进,以对引脚全部的短路故障、呆滞故障进行完备诊断。具体步骤如下:

(1)引脚分类

电路图中的引脚可分为输入、输出、输入/输出、空闲、专用输入、地/电源、NC几类。由于专用输入引脚边界扫描结构没有更新寄存器,所以测试图形无法输出到引脚因此不能用此方法测试。而地/电源引脚、NC引脚不带有边界扫描结构所以也不能测试。故此,真正能进行测试的引脚只有前四类。可令n等于前四类引脚数目的总和。

(2)生成测试向量

按照引脚号对前四类引脚进行从小到大排序,序号为:0到n-1,然后计算log2(n+2)的值,再根据有余进一的原则算出并行测试向量个数m。为避免出现误判,可从000……1开始进行二进制计数,以形成测试向量,其行数为n,列数为m。

(3)发送测试向量

(4)采集测试结果

(5) 添加测试图形

比较测试序列与采集到的结果,确定异常行(总数W)。为避免混淆和误判故障,可进一步添加C个为全0或全1码的测试图形。

(6)故障诊断

该算法具有故障定位准确,测试周期短,测试效率高等特点。

4 测试算法

电路板常见故障模型有呆滞型故障、固定开路故障和短路故障。为了消除误判和混淆故障及提高诊断速度,可在算法上结合电路结构对自适应算法和CX-TB导通测试算法以及二进制计数测试序列进行改进,以对引脚全部的短路故障、呆滞故障进行完备诊断。具体步骤如下:

(1)引脚分类

电路图中的引脚可分为输入、输出、输入/输出、空闲、专用输入、地/电源、NC几类。由于专用输入引脚边界扫描结构没有更新寄存器,所以测试图形无法输出到引脚因此不能用此方法测试。而地/电源引脚、NC引脚不带有边界扫描结构所以也不能测试。故此,真正能进行测试的引脚只有前四类。可令n等于前四类引脚数目的总和。

(2)生成测试向量

按照引脚号对前四类引脚进行从小到大排序,序号为:0到n-1,然后计算log2(n+2)的值,再根据有余进一的原则算出并行测试向量个数m。为避免出现误判,可从000……1开始进行二进制计数,以形成测试向量,其行数为n,列数为m。

(3)发送测试向量

(4)采集测试结果

(5) 添加测试图形

比较测试序列与采集到的结果,确定异常行(总数W)。为避免混淆和误判故障,可进一步添加C个为全0或全1码的测试图形。

(6)故障诊断

该算法具有故障定位准确,测试周期短,测试效率高等特点。

5 故障诊断

由于EPM9320LC84芯片采用CMOS工艺制作,因此,它的引脚与地、电源短路分别归为呆滞于0和呆滞于1;器件引脚悬空也归为呆滞于0。其引脚互连测试图形是“与”逻辑。

具体诊断时,可比较输出测试图形与采集测试图形的差异,相同即为正常行,不同则为异常行。诊断过程如下:

●若异常行和正常行的测试向量相同,则添加测试图形令异常行并行测试向量为全0,其余行测试向量为全1,而对于发送、采集添加的测试向量,若正常行采集结果为全0,则正常行与异常行对应引脚互连。否则必有其它脚与异常行对应脚互连。

●如果异常行向量是全1,判断异常行对应引脚呆滞于1。

●如果异常行向量为全0,则可添加测试图形令所有测试向量为全1,同时发送、采集添加的测试向量,此时若异常行测试结果为全0,则异常行对应引脚呆滞于0。否则必有其它脚与该异常行对应引脚互连。

●如果两个异常行测试向量相同且为全0,则可添加测试图形以令所有测试向量为全1,同时发送、采集添加的测试向量,如果异常行为全0,则异常行对应引脚呆滞于0;如果测试结果是两行都为全1,则添加测试图形令两个异常行测试向量分别为全1和全0,其余向量为全1,再一次发送、采集添加的测试向量,如果采样结果是两个异常行为全0,则两异常行对应引脚互连;否则两异常行对应引脚无关,必有其它引脚与异常行对应引脚互连。

●如果两个异常行测试向量相同,且既非全0又非全1,则两异常行对应引脚互连。

6 结束语

利用芯片边界扫描结构,采用本文介绍的算法,不需要附加其它芯片,就能完成EPM9320LC84所有I/0引脚的印刷电路板故障诊断它所覆盖的故障包括引脚呆滞,引脚互连等。而且这种算法对多引脚互连故障也能准确诊断。其测试方法简单易行,测试时间不超过1秒,而且诊断十分准确。

5 故障诊断

由于EPM9320LC84芯片采用CMOS工艺制作,因此,它的引脚与地、电源短路分别归为呆滞于0和呆滞于1;器件引脚悬空也归为呆滞于0。其引脚互连测试图形是“与”逻辑。

具体诊断时,可比较输出测试图形与采集测试图形的差异,相同即为正常行,不同则为异常行。诊断过程如下:

●若异常行和正常行的测试向量相同,则添加测试图形令异常行并行测试向量为全0,其余行测试向量为全1,而对于发送、采集添加的测试向量,若正常行采集结果为全0,则正常行与异常行对应引脚互连。否则必有其它脚与异常行对应脚互连。

●如果异常行向量是全1,判断异常行对应引脚呆滞于1。

●如果异常行向量为全0,则可添加测试图形令所有测试向量为全1,同时发送、采集添加的测试向量,此时若异常行测试结果为全0,则异常行对应引脚呆滞于0。否则必有其它脚与该异常行对应引脚互连。

●如果两个异常行测试向量相同且为全0,则可添加测试图形以令所有测试向量为全1,同时发送、采集添加的测试向量,如果异常行为全0,则异常行对应引脚呆滞于0;如果测试结果是两行都为全1,则添加测试图形令两个异常行测试向量分别为全1和全0,其余向量为全1,再一次发送、采集添加的测试向量,如果采样结果是两个异常行为全0,则两异常行对应引脚互连;否则两异常行对应引脚无关,必有其它引脚与异常行对应引脚互连。

●如果两个异常行测试向量相同,且既非全0又非全1,则两异常行对应引脚互连。

6 结束语

利用芯片边界扫描结构,采用本文介绍的算法,不需要附加其它芯片,就能完成EPM9320LC84所有I/0引脚的印刷电路板故障诊断它所覆盖的故障包括引脚呆滞,引脚互连等。而且这种算法对多引脚互连故障也能准确诊断。其测试方法简单易行,测试时间不超过1秒,而且诊断十分准确。

上一篇:基于FPGA的乐曲发生器设计

下一篇:用EDA设计LED汉字滚动显示器

- 热门资源推荐

- 热门放大器推荐

Verilog HDL数字集成电路设计原理与应用

Verilog HDL数字集成电路设计原理与应用 TC913BCOATR

TC913BCOATR

京公网安备 11010802033920号

京公网安备 11010802033920号