1 引 言

VME(Versa Module Eurocard)总线是一种计算机总线结构,1981年由其生产商Motorola,Mostesk和Signe-tios三家公司组成的集团合作定义。1987年,VME总线被批准为国际标准IEEE1014-1987。VME总线系统采用主控/目标结构、异步非复用传输模式,支持16位、24位、32位寻址及8位、16位、24位、32位数据传输,最大总线速度是40 MB/s。1996年的新标准VME64(ANSI/VI-TA1-1994)将总线数据宽度提升到64位,最大数据传输速度为80 MB/s。而由FORCE COMPUTERS制定的VME64x总线规范将总线速度提高到了320 MB/s。历史上,VME总线由于其众多的功能、强大的兼容性、并行性和高可靠性一直是实时嵌入式系统的首选机型,主要应用于图像处理、军事通信、雷达信号处理等众多领域。本文基于雷达实时信号处理的需要,用FPGA实现了多DSP信号处理模板局部总线和基于标准VME总线的计算机进行通信的接口设计。

2 VME总线的功能特点

VME总线系统的功能结构可以分为4类:数据传输总线(DTB)、DTB仲裁总线、优先中断总线和实用总线。每一类都包括一条总线以及与之相关的功能模块,他们共同完成某一确定的功能。

2.1 数据传输总线

DTB信号线可以分为3类:寻址线、数据线、控制线。为了适应处理器寻址的灵活性,并对地址空问进行保护,VME总线提供6条地址修改线,选择不同的地址修改码即可实现16,24,32位的寻址变化,并对地址空间赋予特定的保护权限。控制线和地址线的不同组合可以灵活地控制数据的传送宽度和方式,如8,16,24,32位。依靠这些控制信号的互锁逻辑,VME总线进行异部传输,而不需要时钟的同步,从而可以可靠地实现不同设备之间的数据传输。当主从模块交换数据时,地址线由主模块驱动进行寻址,根据利用的地址线数目的不同,地址可以是短地址、标准地址和扩展地址,所用地址线的数目由地址修改线AM0~AM5规定。数据线D00~D31用来传输l~4个字节的数据。主模块用数据选通线DS0~DS1,字长线LWORD和地址线A01配合制定不同的数据传输周期类型。其数据长度选择的真值表和地址总线真值表如表1和表2所示。这里暂不涉及64位据和地址总线。

2.2 DTB仲裁总线

在VME总线系统中,当同时有多个模块要求使用DTB时,仲裁子系统就检测这些请求,并在某一时刻仅允许一块模板使用DTB。

仲裁总线由6条总线信号线和4组菊花链信号线组成:总线请求线BR0~BR3;总线忙线BBSY;总线清除线BCLR;总线允许输入线BG0IN~BG3IN;总线允许输出线BG0OUT~BG3OUT。菊花链信号线由每块板的总线允许输入线(BgxIN)和总线允许输出线(BgxOUT)组成。从n号插槽出来的菊花链信号线,如BGxOUT与下一板(n+1)号插槽的(BgxIN)相连。槽1的BgxIN一般由槽1的总线仲裁模块来驱动。

在VME总线仲裁系统中共有O~3四种优先级,第3优先级最高,第0优先级最低,也就是说DTB仲裁总线中总线请求,总线允许输入和总线允许输出各有4条。每个请求模块只驱动一条请求线,并接受同一级别的总线允许链路仲裁,即BRx,BGxIN,BGxOUT中x相同时才能构成一级仲裁链路。至于仲裁驱动模块对4条仲裁链路的处理,则可以采用3种不同的方式:优先法、循环法和单级法。优先级仲裁是按照4条总线请求的优先级别从最高的BR3到最低的BR0这一固定的优先顺序分配总线的。循环仲裁是按照循环优先的原则来分配总线的,在总线请求线BR(n)上某一请求模块已获准使用总线时,则下一次仲裁的最高优先级就是BR(n-1);单级仅接受BR3上的请求,并依靠BR3上的总线允许菊花链来裁判。

2.3 优先中断总线

通常仅有一个处理器处理中断,监视中断请求线(IRQl~IRQ7),IRQ7优先权最高,在响应中断时,一个地址周期产生,这个地址指示请求已被响应,中断响应线(IACK)被仲裁器改变以daisy-chain(菊花链)的方式向下传送,用IACKIN和IACKOUT信号,一个数据周期指出请求设备,并提取请求设备的状态和IV(中断矢量)。

2.4 实用总线

实用总线功能提供系统周期定时,上电初始化和故障检测功能,主要有SYSCLK(系统时钟线),ACFAIL(交流故障线),SYSRESET(系统复位线),SYSFAIL(系统故障线);系统时钟线是独立的频率为16 MHz的时钟信号,由位于1号槽的系统时钟驱动模块产生,可以作为整个系统的时间基准。另外3条信号线由l号槽的电源监控模块产生。

3 系统接口设计方案

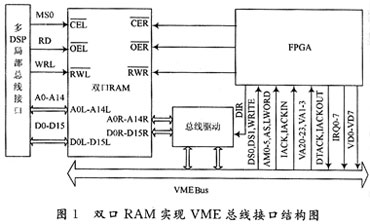

通常,设计多DSP局部总线与标准总线接口可以采用专业公司提供的接口控制芯片。例如,利用Cypress公司的VIC64桥接电路可以设计功能全面,具有完全的主模块/从模块功能的标准VME总线接口。但是如果用户开发的基于VME总线的应用模块仅作为从设备.那么就只需要具备从从模块的总线接口,这样就可以使用FPGA自行设计桥接电路,本设计结合系统需要,采用双口RAM实现数据交换,FPGA实现接口逻辑转换。接口设计方案如图1所示。

图1中DSP为Analog Devices公司TS101,4片TS101共享总线组成紧耦合系统。双口RAM为Cypress公司的高速、大容量、低功耗芯片CY7C025AV,他的容量为32 kB,数据宽度为16 b,最高访问速度达到80 MHz。FPGA为ALTERA公司的EPF10K30A。

双口RAM的左端口与多DSP局部总线相连,局部总线的MS0连接双口RAM的CEL(左端口使能),双口RAM在多DSP局部总线的地址空间映射为0X8000000~0X8007FFF。双口RAM的读写时序与普通存储器相同,可以直接与局部总线相连,DSP可以通过慢速总线传输协议访问双口RAM的地址空间。双口RAM的OEL(左端口输出使能)和RWL(左端口读写使能)分别接局部总线的RD和W/R,左端口数据线(D0L~D15L)和地址线(A0L~A14L)也分别与局部总线的数据和地址线相连。

双口RAM右端口和标准VME总线通信,由FPGA负责译码标准VME总线控制信号线产生接口控制逻辑,双口RAM的右端口数据线(D0R~D15R)和地址线(A0R~A14R)通过总线驱动器74F16245驱动后和标准VME:总线的数据和地址线相连。74F16245的使能和传输方向信号由FPGA译码产生。

标准VME总线的控制信号线与FPGA连接,由于FPGA的I/O管脚可以兼容各种电平,所以VME的控制信号线可以直接与FPGA相连。

4 FPGA接口程序的设计

FPGA中的VME总线接口程序主要由2大模块组成,一个模块是VME主机对双口RAM访问的普通I/O模块,该模块主要实现标准VME总线访问时序到双口RAM访问时序的逻辑转换,VME总线地址译码和访问模式译码,以及VME总线到双口RAM的数据地址线驱动的逻辑控制。另一个模块多DSP模板向VME主机发送中断的中断请求模块,该模块主要完成中断信号的发送,主机发来的中断认可的处理和向主机发送中断状态和识别码。

4.1 普通I/O模块的设计

普通I/O模块的程序设计采用VHDL语言状态机实现,整个过程分为5种状态:idle(空闲状态),selection(选中状态),write(写数据状态),read(读数据状态)和answer(应答状态)。

idle状态表示本模块没有被VME主机访问;selection状态表示地址和模式译码已经选中本模块,主机要访问双口RAM的地址空间;write状态VME主机正在向双口RAM写入数据;read状态表示VME主机正在从双口RAM中读出数据;answer表示本模块响应访问周期向VME主机发送数据传输应答。描述整个过程的状态转移图如图2所示。

I/O模块标准传输的过程描述为:idle状态时,地址监测划模块应处于VME总线地址译码和访问模式监测状态,本模块的访问模式为A24-D16标准数据访问模式。当VME主机输出的地址和访问模式与本模块一致时,即输入地址VA20~VA23为程序所设的地址,AM码等于3A(H),LWORD为高,VA1为低和AS为低,地址监测模块输出“从模块选中信号”,启动了从模块访问,这时模块进人selection状态。

进入selection状态后,程序监视DS0,1(数据选通信号)和WRITE(读写信号)。当DS0,DS1都为低,WRITE为高时,模块进入read状态;当DS0,DS1都为低,WRITE为低时,模块进入write状态。

当模块处于read状态时,FPGA置双口RAM的CER为低使能双口RAM,OER为低使能数据输出,RWR为高关闭写使能,使双口RAM为数据输出状态。FPGA还要打开总线驱动使能,设置总线驱动方向,使VME地址总线为输入,数据总线为输出。

当模块处于write状态时,FPGA置双口RAM的CER为低使能双口RAM,RWR为低使能写信号,OER为高关闭输出数据使能,使双口RAM为数据输入状态。FPGA还要打开总线驱动使能,设置总线驱动方向,使VME地址数据线都为输入。

为了设置“读应答使能”和“写应答使能”,模块在进入read(读数据状态)或write(写数据状态)后,都使能一个计数器计数。当计数器的计数值为某值时(此计数值可以用来调整读写周期的大小,本例中使用32 MHz时钟时,计数值为1即可),分别置“读应答使能”和“写应答使能”有效,模块进入answer(应答状态)状态。在模块进入an-swer后,程序置DTACK为低,向主机发送数据传送应答。这样,当主机向双口RAM写数据时,通知主机可以释放总线;当主机从双口RAM读数据时,通知主机数据已经稳定可以锁存数据。主机收到DTACK后释放DS0,DS1为高,AS为高;模块检测到DS0,DS1为高,AS为高后,将DTACK置高,关闭双口RAM使能和VME总线驱动,模块进入idle(空闲状态),一个标准的VME总线传输周期结束。

整个过程的仿真时序波形如图3所示:图中,“000”表示idle状态,“001”表示selection状态,“101”表示read状态,“011”表示write状态,“111”表示answer状态。

4.2 中断请求模块的设计

本模块设计采用VHDL语言编写程序,使用进程对中断产生模块的功能进行描述,即用进程中if-elsif-else语句来描述这个时序过程。

中断模块负责产生标准VME总线中断,处理VME主机中断管理模块发来的中断响应。程序设计了一个8位的内部寄存器VINT,用来控制中断信号的产生,寄存器位VINT1~7对应IRQ1~7,控制VME总线中断信号的产生和撤销,VINT0作为发中断使能位.当VINT0等于1时,程序检查VINT1~7,置相应的中断请求信号线IRQ1~7为低,便向监控该信号的VME主机中断管理模块发出了中断请求。

中断请求模块发出中断请求后,监控输入信号IACK-IN和A1~3,等待VME主机中断管理模块发来的中断响应。当检测到IACKIN为低,即开始中断号对照,检测A1~3上的值是否和本模块发出的中断号一致,如果不一致就将驱动IACKOUT输出菊花链为低,如果一致将该中断的状态/识别码放到VD0~7上,当数据稳定后,驱动DTACK为低,通知VME主机中断管理模块取走中断状态识别码,主机进入相应的中断服务程序.即完成了从模块VME总线中断的发送和响应过程。

5 结 语

用VHDL语言实现了多DSP局部总线到标准VME总线普通I/O模块和中断请求模块的设计,双口RAM的存储空间映射到工控机的存储空间的地址为0XC0410000~0XC0413FFFC。使用32 MHz时钟时.通信速率町达16 MB/s,能够满足雷达信号处理板到终端通信的要求。

上一篇:S1D13506显示控制器与AT91RM9200的接口设计

下一篇:CAN现场总线的时间信息共享技术

推荐阅读最新更新时间:2024-05-13 18:35

- 热门资源推荐

- 热门放大器推荐

-

整车控制策略开发需求分析及新能源汽车动力总成测试系统

整车控制策略开发需求分析及新能源汽车动力总成测试系统 -

浅谈电子技术在汽车自动控制中的应用

浅谈电子技术在汽车自动控制中的应用 -

ICCV2023论文汇总:Image and Video Forensics(图像和视频取证)

ICCV2023论文汇总:Image and Video Forensics(图像和视频取证) -

ICCV2023论文汇总:Fairness, Privacy, Ethics, Social-good, Transparency, Accountability in Vision(视觉中的公平、隐

ICCV2023论文汇总:Fairness, Privacy, Ethics, Social-good, Transparency, Accountability in Vision(视觉中的公平、隐 -

嵌入式网络那些事:LwIP协议深度剖析与实战演练

嵌入式网络那些事:LwIP协议深度剖析与实战演练 -

东芝1200V SIC SBD “TRSxxx120Hx系列” 助力工业电源设备高效

东芝1200V SIC SBD “TRSxxx120Hx系列” 助力工业电源设备高效 -

一起来学Cadence Allegro高速PCB设计

一起来学Cadence Allegro高速PCB设计 -

5G+MEC+V2X车联网解决方案白皮书

5G+MEC+V2X车联网解决方案白皮书

整车控制策略开发需求分析及新能源汽车动力总成测试系统

整车控制策略开发需求分析及新能源汽车动力总成测试系统 ICCV2023论文汇总:Image and Video Forensics(图像和视频取证)

ICCV2023论文汇总:Image and Video Forensics(图像和视频取证) 嵌入式网络那些事:LwIP协议深度剖析与实战演练

嵌入式网络那些事:LwIP协议深度剖析与实战演练

京公网安备 11010802033920号

京公网安备 11010802033920号