MAX7044是基于晶振PLL 的VHF/UHF发射器芯片,在300 MHz~450 MHz频率范围内发射OOK/ASK数据,数据速率达到100 kbps,输出功率+13 dBm(50Ω负载),电源电压+2.1~+3.6 V,电流消耗在2.7 V时仅7.7 mA。工作温度范围一40℃~+125℃,采用3 mm×3 mm SOT23 - 8封装。

MAX7033是一个完全集成的低功耗CMOS超外差接收器芯片,接收频率范围在300 MHz~450 MHz的ASK信号。接收器射频输入信号范围从一114 dBm-0dBm。MAX7033芯片内部包含有LNA、差分镜像抑制混频器、PLL、VCO、10.7 MHz IF限幅放大器、AGC、RSSI、模拟基带数据信号恢复等电路。工作电压+3.3 V或+5.0V,250μs启动时间,低功耗模式电流消耗<3.5μA,工作温度-40℃~+105℃,采用TSSOP-28和薄形QFN-EP* *-32封装。

MAXT044发射器芯片与接收器芯片MAX7033配套,适合汽车遥控、无键进入系统、安防系统、车库门控制、家庭自动化、无线传感器等应用。

1 基于MAX7044的发射器电路

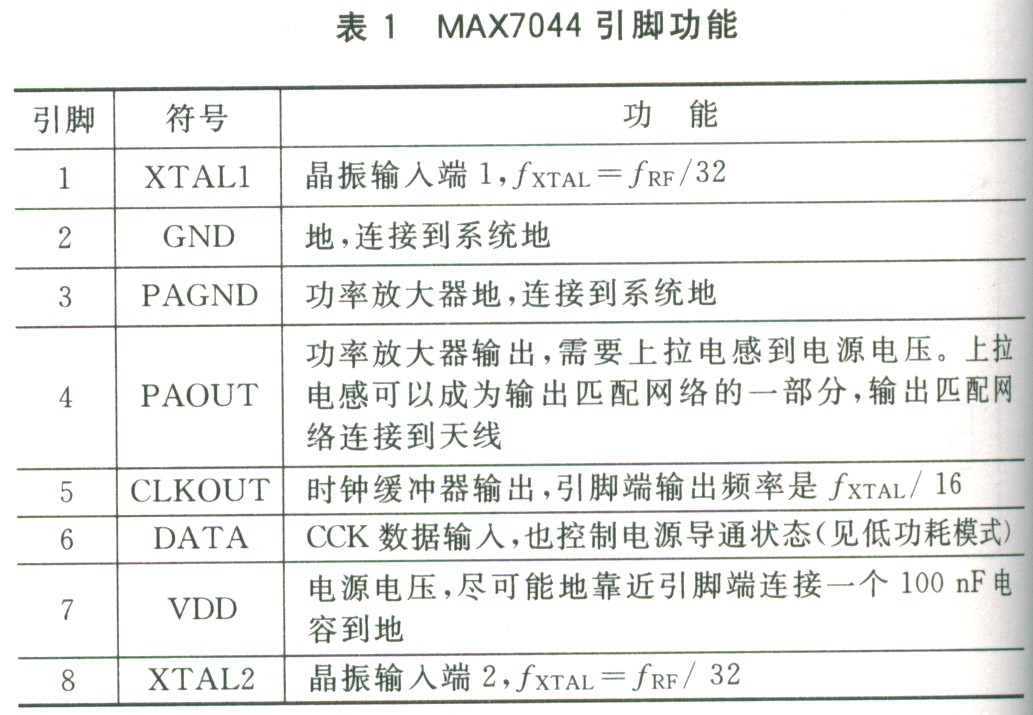

MAX7044引脚功能如表1所列。

MAX7044芯片内部包含功率放大器(PA)、晶体振荡器(crystal oscillator)、驱动器(driver)、数据有效检测电路(data activity detector)、锁定检测电路(10ck detect)、锁相环(32x PLL)、分频器(/16)等电路。

(1)低功耗模式

MAX7044有一个自动的低功耗模式(shutdown mode)控制方式。如果DATA引脚在一个确定的时间(等待时间)内没有动作,器件自动进入低功耗模式。等待时间大约是216个时钟周期,在315 MHz频率大约为6.66ms,在433 MHz频率大约为4.84 ms。进入低功耗模式的等待时间为

式中,fRF是射频发射频率。

当器件在低功耗模式时,在DATA信号的上升沿“热”启动晶振和PLL,晶振和PLL在数据发射前需要220μs的建立时间。

(2)锁相环PLL

PLL(Phase-Locked Loop)功能块包含有相位检波器,充电泵、集成的回路滤波器、VCO、异步时钟分频器、驱动器和晶体振荡器。除了晶振,PLL不需要其他外部元器件。基准频率和载波频率的关系为 fXTAL=fRF/32

在PLL锁定前,锁定检测电路防止功率放大器发射.另外,如果失去载波频率,器件将关闭功率放大器。

(3) 功率放大器

MAX7044的功率放大器(power amplitier)是一个高效率的、漏极开路、C类放大器,使用合适的输出匹配网络,功率放大器能够驱动简单的PCB环行天线和各种形式的50Ω天线。

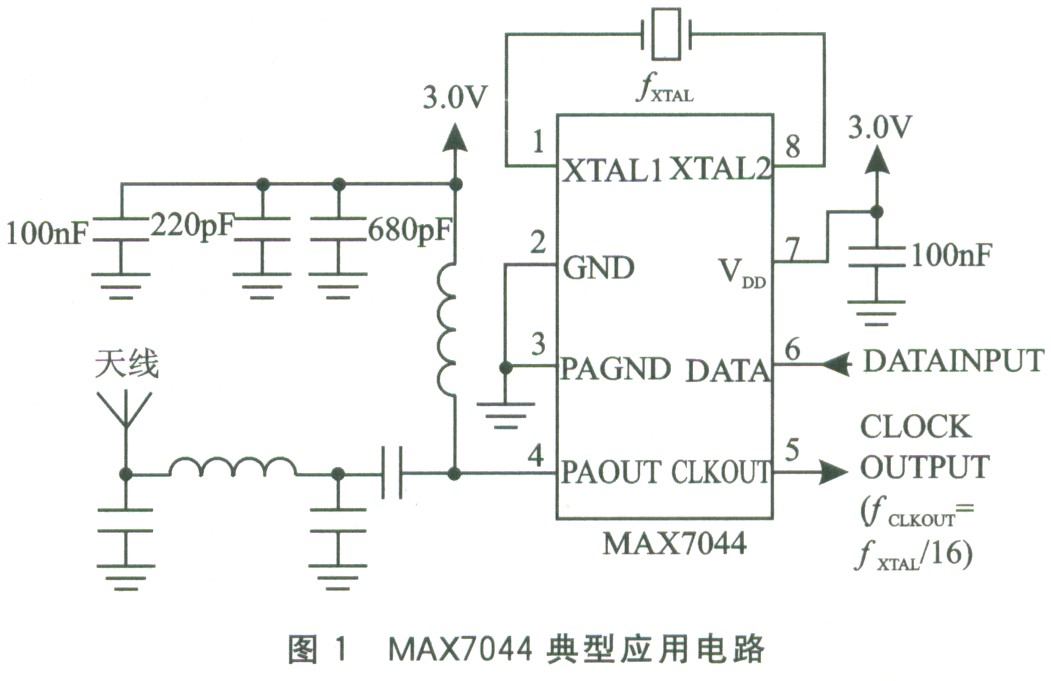

在典型应用电路中,使用电源电压+2.7 V,电路输出电平可达到+13 dBm,整个效率可以达到48%。

(4) 时钟缓冲输出

MAX7044在CLKOUT引脚端提供一个缓冲的时钟输出(buffered clock output),可供微控制器等器件使用。CLKOUT的输出频率是晶振频率的1/16。对于315 MHz射频发射频率,使用的晶振频率是9.843 75 MHz,提供的时钟频率是615.2 kHz。对于433.92 MHz的射频发射频率,使用的晶振频率为13.56 MHz,提供的时钟频率为847.5 kHz。当器件在低功耗模式时,时钟输出无效。数据发射时,在220μs时间之后,时钟输出稳定。一个MAX7044的典型应用电路如图1所示。

2 基于MAX7033的接收器电路

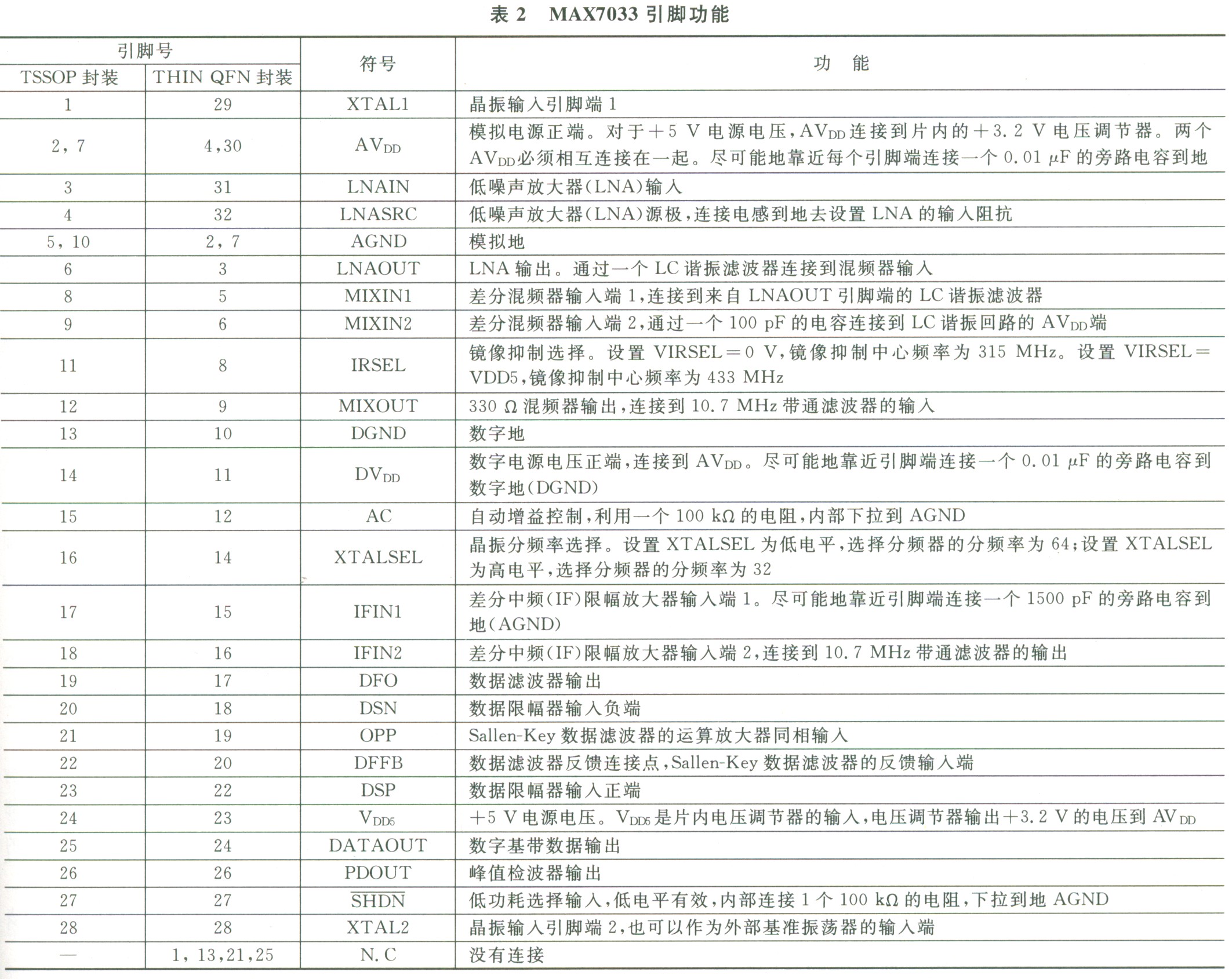

MAX7033引脚功能如表2所列。

MAX7033芯片内部包含有LNA、差分镜像抑制混频器、PLL、VCO、10.7 MHz IF限幅放大器、AGC、RSSI、模拟基带数据信号恢复等电路。

(1)电压调节器

使用单3.0~3.6 V电源电压,直接连接AVDD、DVDD和VDD5到电源电压。使用单4.5~5.5 V电源电压,连接VDD5到电源电压。片上的电压调节器(voltage regulator)产生AVDD引脚端需要的3.2 V电压。DVDD和AVDD两个引脚端必须连接在一起,尽可能地靠近DVDD和AVDD引脚端连接1个0.01 μF的旁路电容到地(AGND)。

(2)低噪声放大器LNA

LNA(Low-Noise Amplifier)是一个nMOS的共基共射放大器,需要使用片外的电感,具有3.0 dB的噪声系数和一12 dBm的IIP3。增益和噪声系数与在天线与LNA输入端之间的匹配网络和在LNA输出与混频器之间的LC谐振网络有关。需要从LNASRC引脚端连接一个电感到地(AGND)。这个电感设置在LNAIN引脚端的输入阻抗的实部,可以实现更多灵活的阻抗匹配,如使用PCB导线得到天线形式。对于50 Ω的输入阻抗,这个电感值为15 nH。注意这个电感值会受PCB导线长度的影响。

LC谐振滤波器连接到LNAOUT引脚端,由L3和C2组成(见典型应用电路)。选择L3和C2,谐振在要求的射频输入频率。谐振频率由 计算。式中,LTOTAL=L3+LPARASITICS;CTTOAL=C2+CPARASITICS。

计算。式中,LTOTAL=L3+LPARASITICS;CTTOAL=C2+CPARASITICS。

LPARASITICS和CCPARASITICS包括PCB板、引脚端、混频器输入阻抗、LNA输出阻抗的电感和电容。这些寄生参数不能忽略,否则会影响谐振滤波器的中心频率。

(3)自动增益控制

当AC引脚端是低电平时,AGC(Automatic Gait Contr01)电路监控RSSI输出。RSSI的输出达到1.98V时,对应的射频输入电平为一62 dBm,AGC开关通过减少电阻控制LNA增益;当RSDSI电平下降到低于1.39V时,对应的射频输入电平为一70 dBm,LNA恢复高增益模式。

当AC引脚端是高电平时和SHDN转向高电平时AGC电路不使能,LNA总是在高增益模式;当AC引脚端是低电平时和SHDN是高电平时,AGC功能恢复。

(4)混频器

MAX7033采用独特的镜像抑制混频器(Mixer)结构可以不使用价格高的SAW滤波器。混频器单元是一个双平衡的混频器对,完成射频信号到10.7 MHz IF的IQ下变频,本振(L0)频率采用低端注入形式。电路具有44dB的镜像抑制能力。IF输出阻抗330Ω,可以采用330Ω的陶瓷滤波器。

IRSEL引脚端是一个逻辑电平输入,可用来选择3个镜像抑制频率中的一个。当VIRSEL=0 V时,镜像抑制频率调谐在315 MHz。VIRSEL=VDDS/2,镜像抑制频率调谐在375 MHz;当VIRSEL=VDD5,镜像抑制频率调谐在433 MHz;当IRSEL引脚端不连接时,在内部设置到VDD5/2,不需要外部VDD5/2电压。

(5)PLL

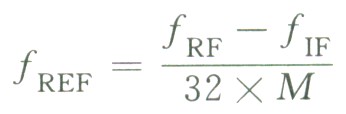

PLL(Phase-Locked Loop)功能块包含有相位检波器、充电泵、集成的回路滤波器、VCO、异步时钟分频器和晶体振荡器驱动器。除了晶振,PLL不需要其他外部元器件。VCO产生低端LO。基准频率、RF频率和IF频率的关系为

式中:M=1(VXTALSEL=VDD5),或者M=2(VXTALSEL=0 V)。

(6)中频和RSSI(Intermediate Frequency and RSSI)

IF部分提供差分330Ω输出阻抗,可以与片外的陶瓷滤波器匹配。6个内部AC耦合限幅放大器提供大约65 dB增益,IF带通滤波器的中心频率10.7 MHz,3 dB带宽大约为10 MHz。

RSSI电路解调IF信号,产生与IF信号电平成比例的直流电压输出,大约为14.2 mV/dB。

(7)晶体振荡器

在MAX7033中的晶体振荡器(crystal oscillator),在XTALI和XTAL2引脚端之间呈现的电容大约为3 pF。使用不同的负载电容,将改变晶振的标准基准频率,如4.7547 MHz的晶振使用10 pF的负载电容。MAX7033的振荡器频率为4.756 3 MHz,有大约100 kHz误差。

也可以使用外部基准振荡器驱动VCO,使用一个1 000 pF的电容交流耦合连接到XTAL2引脚端。

(8)数据滤波器

数据滤波器(data filter)是一个二阶低通Sallen-Key滤波器,需要2个片上的电阻和外部电容组合。调节外部电容的数值,可以改变滤波器的截止频率,以适应不同的数据速率。

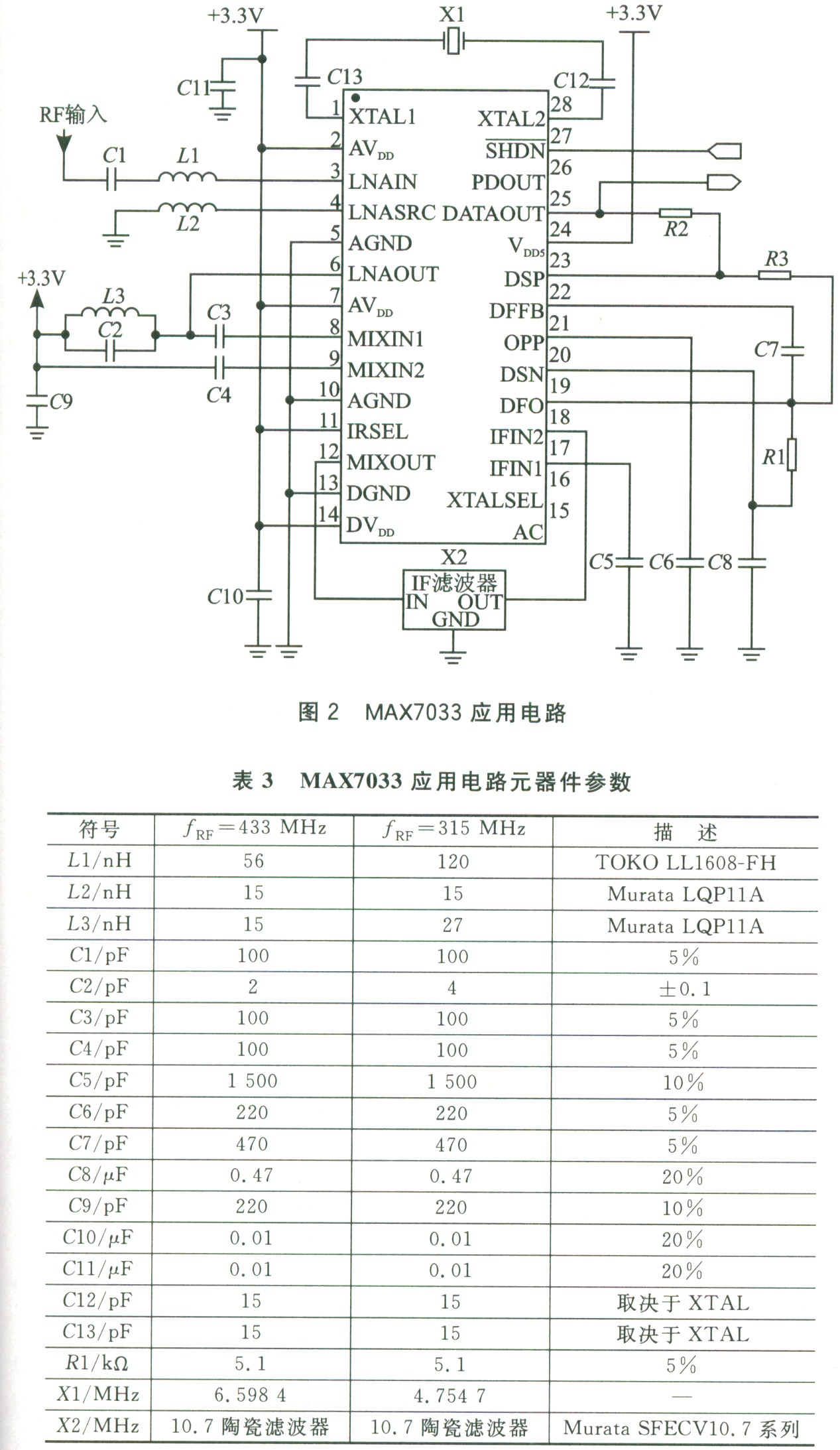

MAX7033的应用电路如图2所示,元器件参数如表3所列。

3 PCB设计考虑

恰当的PCB板设计是射频/微波电路设计的重要部分。在高频输入和输出引脚端使用控制阻抗的导线和使导线尽可能的短,以减少损耗和辐射。在高频,导线长度为λ/lO或者更长,其作用类似天线。保持导线尽可能地短,可以减少寄生电感。一般情况,2.54 cm(1英寸)的PCB导线长度,大约附加20 nH的寄生电感。寄生电感将影响实际的元件参数。例如:1.27 cm(O.5英寸)长的导线与一个100 nH的电感器连接,将增加额外的10 nH电感。使用宽的导线、可靠的接地或者电源板在信号导线的下面可以减少寄生电感。另外,所有的GND引脚端要求使用低电感连接到地,尽可能地靠近所有的VDD引脚端,连接退耦电容到地。

4 与微控制器的接口

MAX7044和MAX7033可以直接与微控制器接口。

微控制器的输出数据可以直接输入到MAX7044的数据输入引脚端(引脚端6,DA-TA),MAX7044可以通过时钟输出引脚端(引脚端5,CLKOUT),提供频率为fxTAL/16的时钟信号到微控制器。

MAX7033的接收数据可以通过数据输出引脚端(引脚端25,DATAOUT)输出到微控制器。微控制器可以通过控制MAX7033的低功耗控制引脚端(引脚端27,SHDN)的电平状态(低电平有效),使MAX7033进入低功耗模式。

采用MAX7044和MAX7033构成的无线收发电路,电路结构简单,用单片机控制进行的点对点无线收发,收发距离大于10O m,数据速率可达到1O0 kbps。

上一篇:降低CDMA/W-CDMA蜂窝电话射频功耗的设计

下一篇:基于nRF24E1的嵌入式2.4GHz无线接入系统

推荐阅读最新更新时间:2024-05-13 18:12

汽车用磁性材料-共模滤波电感

汽车用磁性材料-共模滤波电感 Verilog HDL数字集成电路设计原理与应用

Verilog HDL数字集成电路设计原理与应用

京公网安备 11010802033920号

京公网安备 11010802033920号