随着数据中心和电动汽车等大功率电子产品越来越受欢迎,电力电子行业正在经历快速创新。为了满足对高功率高效率不断增长的需求,宽带隙(WBG)半导体等许多新技术变得越来越重要。

在这些高功率应用中凸显出前景的一项技术是超结 MOSFET,它是对传统技术的改进,可提供更高的效率和更小的尺寸。

本周,Alpha&Omega(A&O)发布了两款直接针对这些大功率应用的新型超结MOSFET。

在本文中,我们将讨论超结技术——为什么它对数据中心至关重要,以及 A&O的解决方案。

高压下的 MOSFET 导通电阻挑战

对于功率开关应用中的 MOSFET,最关键的器件参数之一是导通电阻RDS(on)。

RDS(on) 测量晶体管的有效电阻,该规格直接决定 MOSFET 的功率效率。

影响 FET RDS(on) 电阻的最大因素之一是器件的外延 (epi) 层,它是器件的主要耐压区域。

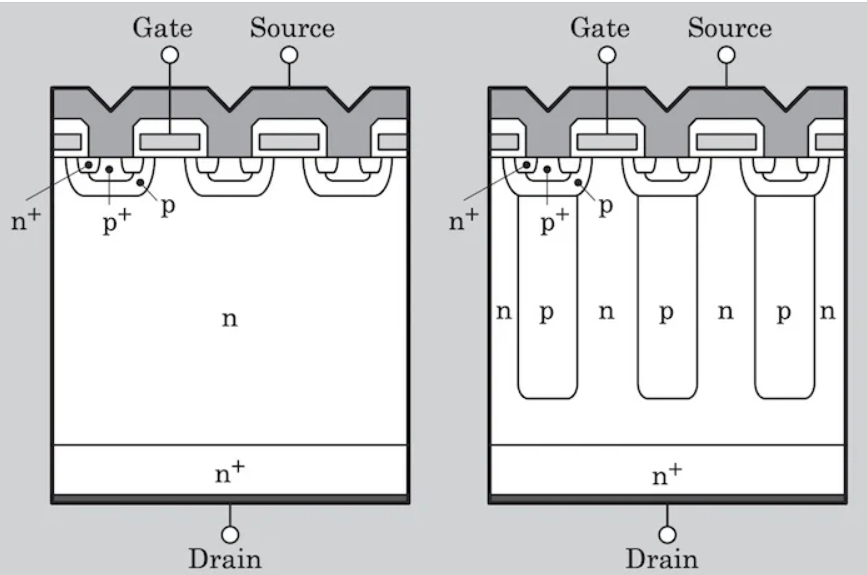

传统平面MOSFET的布局。

随着电压的增加,外延层也需要增加厚度并变得更轻掺杂以帮助阻挡高压。

然而,这会增加外延层的电阻,从而增加 MOSFET 的总RDS(on),从而产生不良影响。

对于额定电压为 600 V 的 MOSFET,超过 95% 的器件电阻直接来自外延层。具体而言,估计额定电压每增加一倍,维持先前 RDS(on) 所需的面积就会增加五倍。

数据中心高压应用

在设计高压应用中的功率 FET 时,晶体管尺寸、其电压隔离能力及RDS(on)之间要进行折衷。

具体来说,在数据中心的高压应用中,设计人员需要能够实现高效率和纤薄外形的功率 FET,以适应越来越薄的系统,例如 1 U 或 0.5 U。对于这些应用,超结 MOSFET 已成为可行的选择。

平面功率 MOSFET(左)和超结 MOSFET(右)的结构。

超结MOSFET是通过使用深沟槽填充等技术来克服外延层的电阻。

超结场效应管采用沟槽结构,多个垂直PN结排列,在保持高阻断电压的同时,有效降低了外延层的电阻率。

因此超结 MOSFET 可以实现极低的 RDS(on),同时保持小尺寸和高阻断电压。这一特性使该设备成为数据中心等大功率应用的流行选择。

A&O瞄准数据中心

如前所述,本周,A&O宣布发布两款针对数据中心应用的新型超结 MOSFET。

这两款新产品 AONV110A60 和 AONV140A60 都是 600 V 超结 FET,设计用于在小封装中具有极低的 RDS(on)。

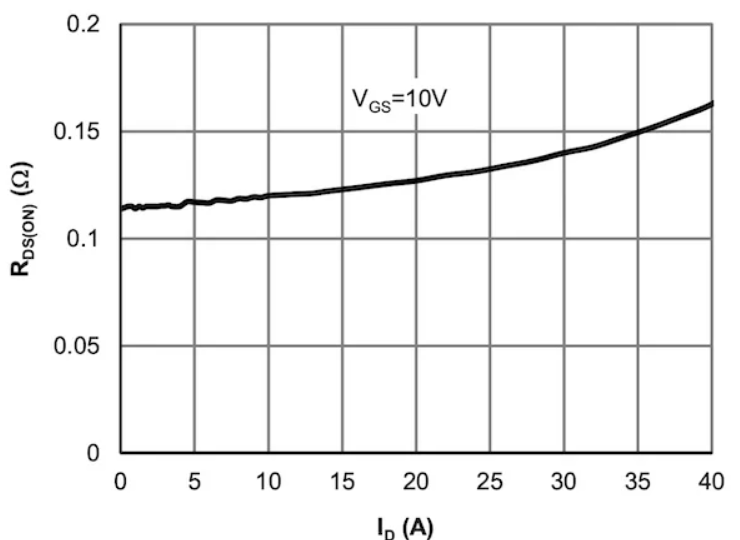

AONV140A60 导通电阻与漏极电流和栅极电压的关系。图片由A&O提供

根据数据表,这两款器件的 RDS(on) 分别为 0.11 Ω和0.14 Ω,同时均采用 8 mm x 8 mm x 0.9 mm DFN 封装。

除了数据中心,A&O声称这些产品非常适合各种其他应用,包括快充、太阳能逆变器和工业电源等。

上一篇:TDK推出EIA 2220尺寸的紧凑型CeraLink®电容器

下一篇:Bourns推出三款全新可高温运作半屏蔽功率电感器

Vishay线上图书馆

- 选型-汽车级表面贴装和通孔超快整流器

- 你知道吗?DC-LINK电容在高湿条件下具有高度稳定性

- microBUCK和microBRICK直流/直流稳压器解决方案

- SOP-4小型封装光伏MOSFET驱动器VOMDA1271

- 使用薄膜、大功率、背接触式电阻的优势

- SQJQ140E车规级N沟道40V MOSFET

- Bourns 推出两款厚膜电阻系列,具备高功率耗散能力, 采用紧凑型 TO-220 和 DPAK 封装设计

- Bourns 全新高脉冲制动电阻系列问世,展现卓越能量消散能力

- Nexperia推出新款120 V/4 A半桥栅极驱动器,进一步提高工业和汽车应用的鲁棒性和效率

- 英飞凌推出高效率、高功率密度的新一代氮化镓功率分立器件

- Vishay 新款150 V MOSFET具备业界领先的功率损耗性能

- 强茂SGT MOSFET第一代系列:创新槽沟技术 车规级60 V N通道 突破车用电子的高效表现

- 面向车载应用的 DC/DC 电源

- Vishay推出适用于恶劣环境的紧凑型密封式SMD微调电阻器

- MathWorks 和 NXP 合作推出用于电池管理系统的 Model-Based Design Toolbox

- AM2G-1215DH30Z ±15V 2 瓦 DC-DC 转换器的典型应用

- MC34072ADR2G 二阶高通有源滤波器的典型应用

- UMFT311GP, FT311 GPIO Board 是配合FT311D开发模块使用的屏蔽板

- 使用 Diodes Incorporated 的 PT8A3517 的参考设计

- 【涂鸦智能】门磁zigbee

- MC10XS4200 双路 24V 高边开关典型应用电路

- X-NUCLEO-IKS01A3,用于 STM32 Nucleo 的运动 MEMS 和环境传感器扩展板

- 基于CY8C3866AXI MCU的无传感器BLDC电机控制应用电路

- 用于MP3播放器坞站的D类、2.1声道音频放大器参考设计

- TWR-S08MM128: MC9S08MM医疗开发塔式系统模块

零基础学电子与Arduino:给编程新手的开发板入门指南

零基础学电子与Arduino:给编程新手的开发板入门指南

C44PPGR5330RASK

C44PPGR5330RASK

京公网安备 11010802033920号

京公网安备 11010802033920号