互连 —— 有时是将晶体管连接到 IC 上电路中的纳米宽的金属线 —— 需要进行「大修」。而随着芯片厂逐渐逼近摩尔定律的极限,互连也正成为行业的一大瓶颈。

在 2022 年 12 月初的第 68 届 IEEE 国际电子设备会议(IEDM)上,IBM 的 Chris Penny 告诉工程师们,「在大约 20-25 年的时间里,铜一直是互连的首选金属。然而现在铜的规模正在放缓,这便为替代导体提供了机会。」

根据 IEDM 2022 的研究报告,钌(Ruthenium)是第一大候选材料,但并不像用一种金属换成另一种金属那么简单。它们在芯片上成型的过程必须颠倒过来。这些新的连接将需要不同的形状和更高的密度,还需要更好的绝缘性能,以免信号消耗电容夺走它们所有的优势。

钌。图源:Wikipedia

互连的位置也注定要发生改变,并且这种改变很快就会到来。但研究逐渐表明,这种转变带来的好处背后需要付出一定的代价。

钌,顶部通孔和气隙

目前,钌是最受欢迎的铜替代品。但研究表明,用于建造铜互连的旧方法对钌并不适用。铜互连是用所谓的镶嵌工艺构建的。第一家芯片制造商使用光刻技术在晶体管上方的介电绝缘层中雕刻出互连的形状。然后,他们将衬垫(liner)和阻挡层(barrier)材料沉积,防止铜原子漂移到芯片的其他部分进而搞砸整个过程。然后用铜填充沟槽,通常会填得过满,所以多余的部分必须进行抛光擦掉。

Penny 对 IEDM 的工程师们表示,包括衬垫和阻挡层在内的所有额外的东西,占到了互连体积的 40- 50%。因此,互连的导电部分在变窄,特别是在互连层之间的超细垂直连接中,导致电阻增加。

但是,IBM 和三星的研究人员已经找到了一种方法,来构建紧密间隔、低电阻的钌互连,且不需要衬垫或种子。这种工艺被称为 spacer assisted litho-etch litho-etch(SALELE),它依赖于极紫外光刻的双重帮助。它没有填充沟槽,而是从层或金属中蚀刻出钌互连,然后用电介质填充缝隙。

研究人员使用超薄高密度的水平互连实现了最佳电阻,然而这又增加了电容,损失掉了好处。幸运的是,由于 SALELE 构建了被称为通孔(vias)的垂直连接方式(即在水平连接的顶部而不是下方),细长钌线之间的空间很容易有空气进入,这是目前可用的最佳绝缘体。Penny 表示,对于这些超薄且高密度的互连来说,增加气隙有巨大的潜在好处,可以减少 30% 的线路电容。可以这么说,SALELE 技术为 1 纳米及更高的工艺提供了路线图。

利用通孔走线的 PCB 板。图源:https://www.wevolver.com/article/what-is-a-via-a-comprehensive-guide

埋轨、背面供电技术和 3D 芯片

英特尔计划彻底改变为芯片上晶体管供电的互连位置,最早能在 2024 年实现。该方案被称为背面供电技术(back-side power delivery),即将供电互连网络移动到硅下方,从而从下方连接到晶体管。这种方案两个主要优点:一是允许电流通过更宽、电阻更小的互连,从而减少功率损失。二是为晶体管上方的信号传输互连腾出了空间,这意味着逻辑单元可以更小。

在 IEDM2022 大会上,Imec 研究人员提出了一些使背面供电更高效工作的方法,即将供电网络的端点(被称为埋入式电源轨)移动到更接近晶体管的地方,而不破坏这些晶体管的电子特性。但他们也发现了一个有点麻烦的问题,当用于 3D 堆叠芯片时,背面电源可能会导致热量积聚。

但好消息是:Imec 的研究人员在研究埋入式电源轨和晶体管之间需要多少水平距离时,答案几乎是零。即使需要额外的处理周期来确保晶体管不受影响,但研究人员称,可以在晶体管通道区域旁边构建轨道 —— 尽管仍然会在它下面几十纳米。这意味着逻辑单元可能会更小。

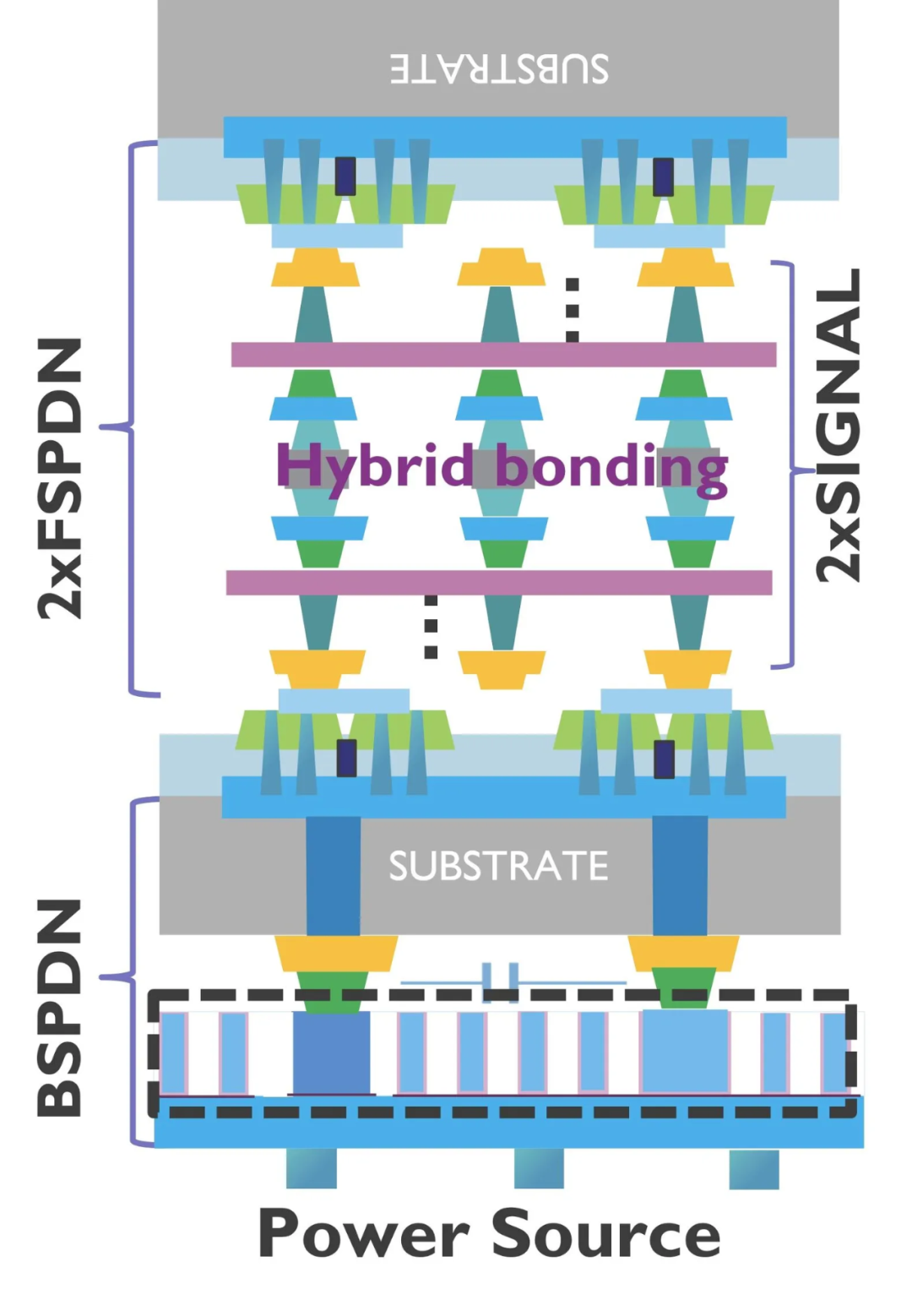

坏消息则是:在单独的研究中,Imec 工程师模拟了同一个未来 CPU 的几个版本。有些拥有如今使用的供电网络,被称为前端供电,其中包括数据和电力在内所有的互连都是在硅上的层中构建的。另一些拥有背面供电网络,其中一个是由两个 CPU 组成的 3D 堆栈,底部有背面电源,顶部有正面电源。

2D CPU 的模拟验证了背面供电的优越性。例如与正面供电相比,它将电力传输的损失减少了一半,瞬态电压下降不也太明显。更重要的是,CPU 面积缩小了 8%。但是,背面芯片的最热部分比正面芯片的最热部分高出 45% 左右。这可能是因为背面供电需要将芯片减薄,且薄到需要粘合到单独的硅片上以保持稳定。这个键(bond)可以阻挡热量流动。

真正的问题在 3D IC 上。顶部 CPU 必须从底部 CPU 获取能量,但通向顶部的漫长传输会出现一些问题。虽然底部 CPU 的压降特性仍优于前端芯片,但顶部 CPU 在这方面的表现就差很多。3D IC 的供电网络消耗的功率是单个前端芯片网络消耗功率的两倍。更糟糕的是,3D 堆栈的散热性能并不好,底部芯片最热的部分几乎是单个前置 CPU 的热 2.5 倍。顶部的 CPU 温度更低一些,但相差无几。

研究人员测试了这样一个场景:将一个带有背面供电网络的 CPU(底部为灰色)与另一个带有前端供电网络的 CPU(顶部为灰色)相连接。

Imec 的研究人员 Rongmei Chen 表示,3D IC 模拟确实有些不现实。将两个完全相同的 CPU 堆叠在一起是不太可能,而将内存与 CPU 堆叠在一起要常见得多。「这样对比有失公允,但它确实能映射出一些潜在的问题。」他说。

上一篇:DRAM正在经历史无前例的大溃败?

下一篇:戴尔被曝激进计划:将全面停用中国制造的芯片

- 热门资源推荐

- 热门放大器推荐

- 一场IC设计业盛宴!10场论坛 200位演讲嘉宾,300+展商亮相2万平米专业展会!

- 富昌电子于杭州举办技术日活动,聚焦新能源“芯”机遇

- 消息称铠侠最快明天获上市批准,市值有望达 7500 亿日元

- 美国政府敲定对格芯 15 亿美元《CHIPS》法案补贴,支持后者提升在美产能

- SK 海力士宣布量产全球最高的 321 层 1Tb TLC 4D NAND 闪存,计划 2025 上半年对外出货

- 三星电子 NRD-K 半导体研发综合体进机,将导入 ASML High NA EUV 光刻设备

- 芯片大混战将启:高通、联发科涉足笔记本,AMD 被曝入局手机

- Exynos 2600 芯片成关键,消息称三星将打响 2nm 芯片反击战

- 曾称华为不可能追上!台积电制程遥遥领先,2nm未量产已招大客户抢单

TMD26353M

TMD26353M

京公网安备 11010802033920号

京公网安备 11010802033920号